I

Изобретение относится к импульсной технике и может быть использовано для получения сложных модулирующих сигналов для систем передачи дискретной информации с ограниченным спектром.

Известно устройство, содержащее генератор, импульсов, счетчик, выходы которого соединены со входами блока памяти, выходы которого подключены ко входам цифроаналогового преобразователя, выход которого являетг ся выходом устройства, два элемента И, элемент НЕ, дешифраторы минимальной и максимальной кодовых комбинаций, причем генератор импульсов подключен к первым входам первого и второго элементов И, вторые входы которых соединены с выходами дешифраторов максимальной и минимальной кодовых комбинаций соответственно, входы которых подключены к выходам счетчика, входы сложения и вычитания которого подключены к выходам первого и второго элементов И соответст- венно, а вход синхронизации устройства соединен с третьим входом первого элемента И и через элемент НЕ с третьим входом второго элемен та ИГ1.

Однако данное устройство обладает недостаточно широкими функциональными возможностями, так как не позволяет получить синхронизирован10ные генерированные сигналы, относительно симметричные некоторого фиксированного значения напряжения.

Цель изобретения - расгаирение функциональных возможностей путем

15 генерирования сложных синхронизируемых сигналов, симйетричнь1х относите-льно своего среднего значения.

Поставленная цель достигается тем что в устройстве для генерирования

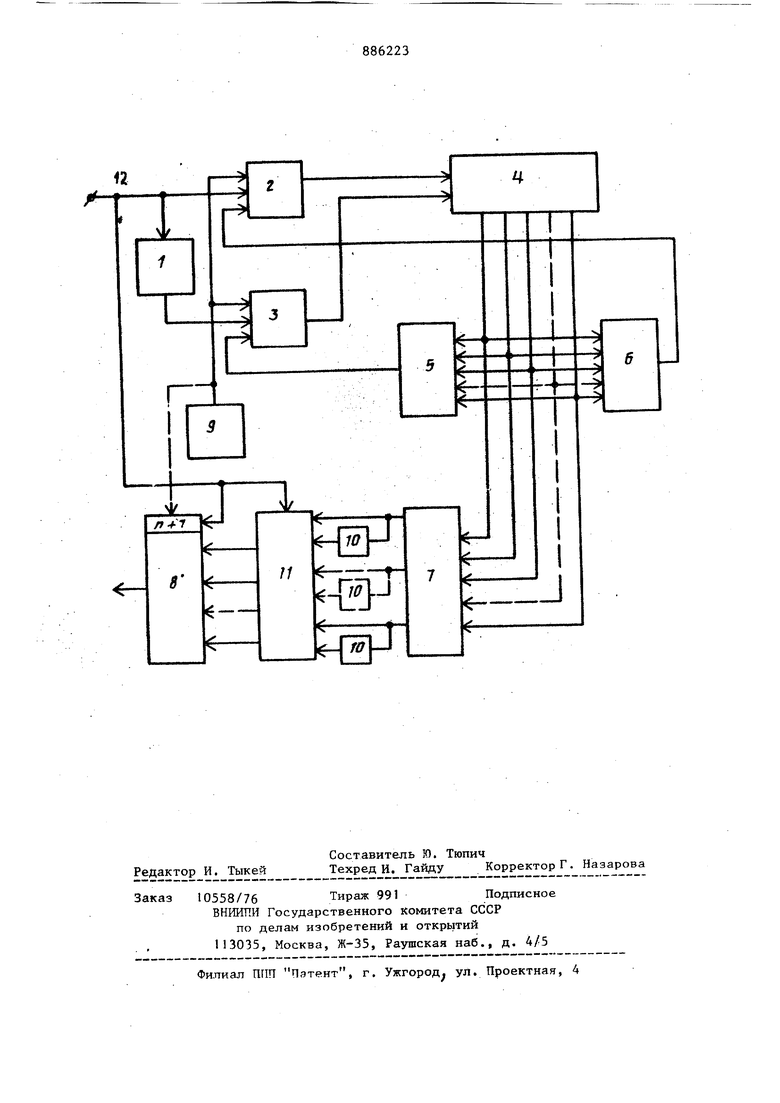

20 сигналов заданной формы, содержащем генератор импульсов, выход которого соединен с первыми входами первого и второго элементов И, вторые входы которьпс соединены друг с другом через инвертор, а третий вход соединен соответственно с выходами первого и второго дешифраторов, разрядные входы которых соединены между собой и подключены через реверсивный счетчик к выходам элементов И, а через блок памяти ко входам цифроаналогового преобразователя, введены п элементов НЕ и п-канальный д ухразрядный мультиплексор, разрядные выходы которого, кроме последнего, подключены к младшим разрядным входам цифроаналоговогс преобразователя, а вход управления соединен со входом синхронизации циф роаналогового преобразователя и входом старшего разряда устройства, пер вые входы п-канального двухразрядного мультиплексора соединены с выхода ми блока памяти непосредственно, а вторые входы соединены с выходами блока памяти через элементы НЕ. На чертеже представлена функциональная схема устройства. Устройство содержит элемент 1 НЕ элементы 2 и 3 И, реверсивный счетчик 4, дешифраторы 5 и 6, блок 7 памяти, цифроаналоговый преобразователь (НАЛ) 8, генератор 9 импульсов элементы i О НЕ, п-канальный двухразрядный мультиплексор 1. На черте же также показан вход 2 синхронизации . С помощью элементов 10 НЕ, мультиплексора 11, а также синхрон ноге управления п + разрядом цифроанааогового преобразователя 8 и муль типлексора 11, достигается формирование синхронизируемьпс симметричных функций. В случае использования дифроаналогового преобразователя 8с внутренней буферной памятью, вход . синхронизации его соединен с выходом генератора 9 импульсов. Устройство работает следующим образом. На вход 12 синхронизации подается бинарный сигнал, несущий информацию а с выхода генератора 9 импульсов Следуют тактовые импульсы с периодсУм не больше, чем 1/2 длительности самого короткого информационного импул са (где к - количество разрядов счет чика 4). Если в первый момент времени после включения счетчик 4 находится в промежуточном состоянии (не в экстремальном),то с выходов дешифраторов 5 и 6 минимальной и мак симальной кодовых комбинаций на входы элементов 2 и 3 И воздействуют логические I:. Допустим, что в момент включения на вход 12 синхронизации устройства воздействовала логическая 1.. В этЬм случае тактовые импульсы проходят вход сложения счетчика А через элемент 2 И. По мере поступления тактовых импульсов на счетчик 4 на адреснйге входы блока 7 памяти поступает сигнал с соответствующих выходов счетчика 4, который подается также на входы дешифратораi 5 и 6 экстремальных кодовых комбинаций. Блок 7 памяти осуществляет функциональное преобразование двоичного кода счетчика 4 в код большей разрядности п, линейно связанный с требуемым значением выходного напряжения устройства в данный момент времени. Кодовые комбинации (слова) с выхода блока 7 -памяти подаются через элементы 10 НЕ и двухразрядный п-канальный мультиплексор 11 на соответствующие входы цифроаналогового преобразователя 8. Если на вход управления мультиплексора I I воздейст вует логическая -, то кодовые комбинации через него проходят с первых видов всех п разрядов не инвертируясь и подаются на соответствующие входы младших разрядов цифроаналогового преобразователя 8. Если на вход управления мультиплексора 1 Г воздействует логический О, то кодовые комбинации на цифроаналоговый преобразователь 8 через мультиплексор 1 проходят со вторых входов инвертирую ясь элементами 10 НЕ. Воздействие на вход цифроаналогового преобразователя 8 логической I (при воздействии на остальные п входов нулевой кодовой комбинации с выходов мультиплексора 11 вызывает появление на его выходе соответствующего напряжения и„ , равного 0,5 и,,гдеи„а ределяется по формуле Ц +aU-. При воздействии на йходы цифроаналогового преобразователя 8 последовательности кодовых комбинаций с выхода мультиплексора I1 на его выходе формируется сигнал U(t), причем Ur,,,iU, и акоПосле достижения полного заполнения счетчика , сигнал навЫходе дешифратора 6 максимальной кодовой комбинации заменяется на логический О, а на выходе дешифратора 5 минимальной кодовой комбинации сохраня I, в результате ется логическая чего оба элемента 2 и ЗИ закрыты и тактовые импульсы на счетчик 4 не поступают.. На выходе цифроаналогового преобразователя 8 фиксируется заданный таблицей истинности.блока 7 памяти, некоторый уровень напряжения, лежаи(ий в инвервале (Ц .. . макс Устойчивое состояние схемы сохраняет ся до замены на входе синхронизации устройства логической I на логичес кий О. В этом случае элемент 2 И остается в закрытом состоянии, а на втором входе элемента 3 И после ин-. вертирования элементом 1 НЕ логический О заменяется на логическую 1 и элемент 3 И открывается. Тактовые импульсы, проходя через эле мент 3 И воздействуют на вход вычитания счетчика 4. Воздействие логического О на п+ разряд цифроаналогового преобразователя 8 вызы .вает появление на его выходе минимально возможного напряжения U (при воздействии на остальные п входов нулевой кодовой комбинации с вых дов мультиплексора П ). При воздействии на вход управления мультиплексор 11 логического О информация на его выход подается со вторых входов и, следовательно, инвертируется элементами 10 НЕ. Инвертированной после довательности кодовых комбинаций соответствует инвертированный сигнал. Таким образом в этом случае сигнал на выходе цифроаналогового преобразователя 8 изменяется в интервале йии n+V Формирование сигнала закапчивается при появлении на выходе дешифратора 5 минимальной кодовой комбинации логического О, в результате чего элемент 3 И закрывается и на выходе цифроаналогового преобразователя 8 фиксируется заданкый уровень напряжения. Это устойчивое состояние устройства сохраняется до замены на входе синхронизации устройства логического О на логическую 1, после чего процесс формирования сигнала повторится. Таким образом, предлагаемое устройство позволяет формировать сложные синхронизируемые сигналы, симметричные относительно своего среднего значения. Формула изобретения Устройство для генерирования сигналов заданной формы по авт. св. № 811237,о т личающееся тем, что, с целью расширения функциональных возможностей, в него введены п элементов НЕ и п-канальный двухразрядный мультиплексор, разрядные выходы которого, кроме последнего, подключены к младшим разрядным входам цифроаналогового преобразователя, а вход управления соединен со входом старшего разряда цифроаналогового преобразователя и входом синхронизации устройства, первые входы п-канального двухразрядного мультиплексора соединены с выходами блока памяти непосредственно, а вторые входы соединены с выходами блока памяти через элементы НЕ. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 811237, кл. Н 03 К 3/64, 1979.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ограничения спектра частотно-манипулированного сигнала | 1980 |

|

SU907852A1 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для передачи данных с самотестированием | 1988 |

|

SU1702376A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| Многоканальный цифроаналоговый преобразователь | 1989 |

|

SU1709527A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Частотный манипулятор | 1979 |

|

SU886300A1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

Авторы

Даты

1981-11-30—Публикация

1979-12-11—Подача