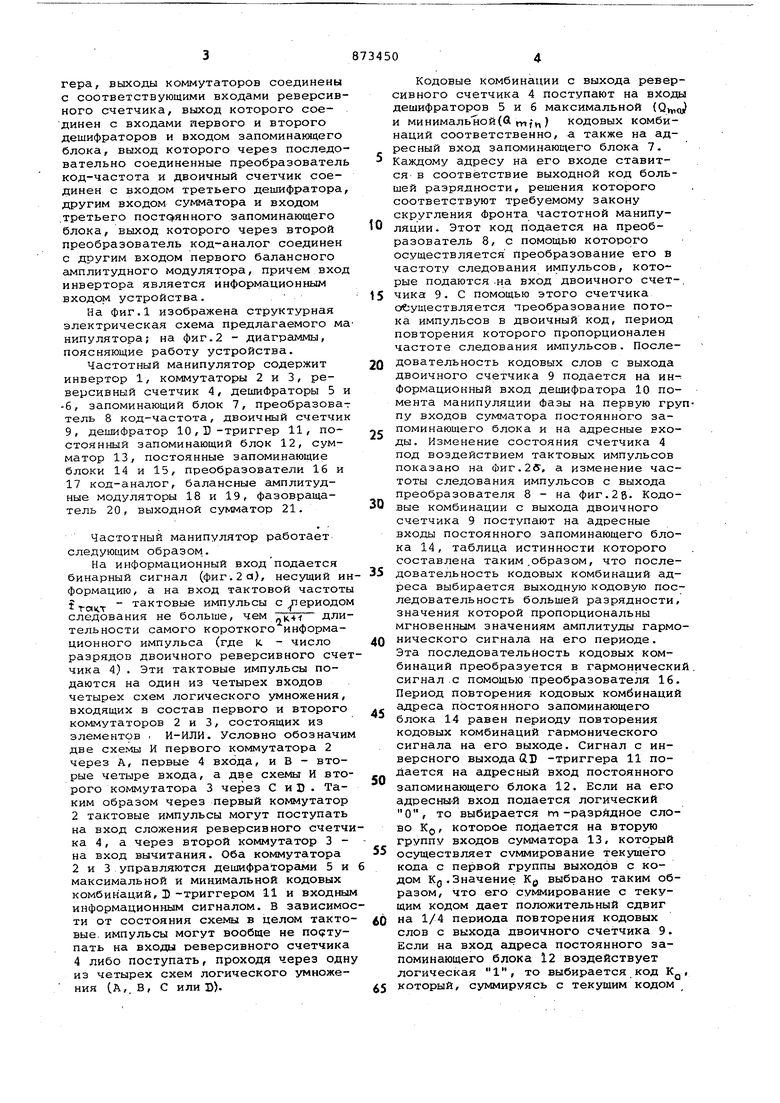

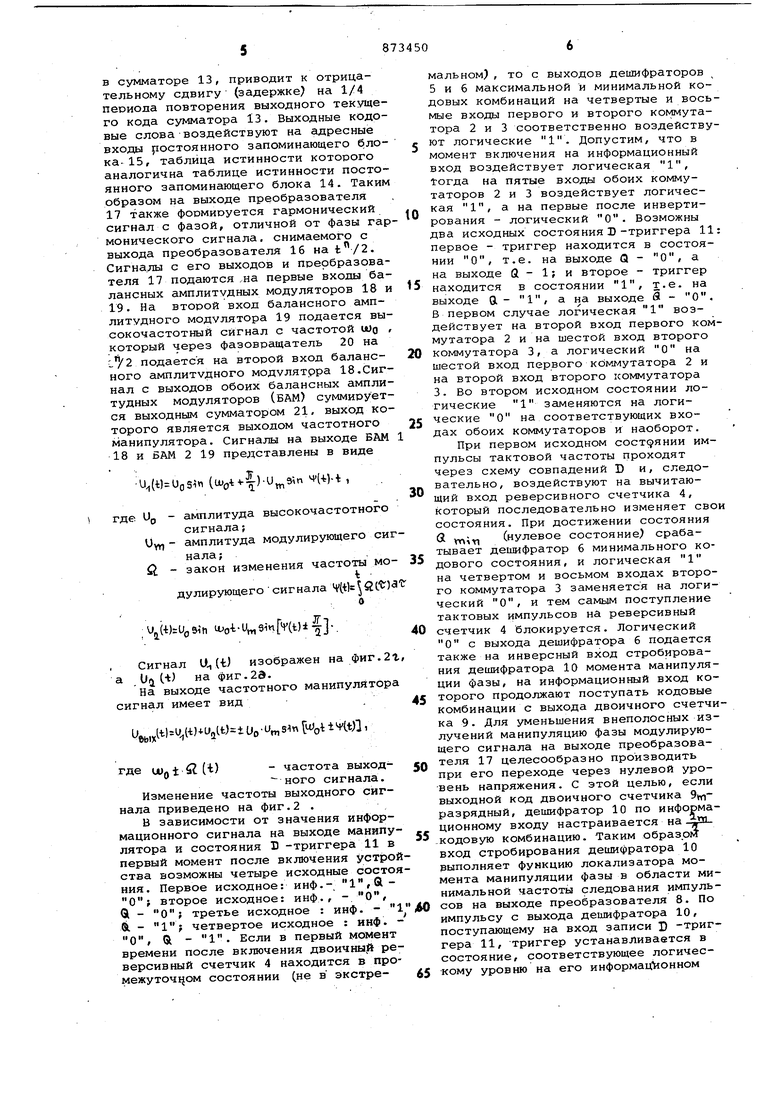

(54) ЧАСТОТНЫЙ МАНИПУЛЯТОР Изобретение относится к радиосвязи и может использоваться дл получения частотно-манипулированного сигнала со скругленными по выбран ному закону фронтами манипуляции для систем передачи дискретной информации с ограниченным спектром. Известен частотный манипулятор, содержащий последовательно соединен ные фазовращатель, первый балансный амплитудный модулятор и выходной сум матор, другой вход которого соедине с выходом второго амплитудного моду лятора 1 . Однако в известном устройстве не достаточная помехозащищенность. Цель изобретения повышение помехозащищенности путем подавления внеполосных излучений. Цель достигается тем, что в частотный манипулятор, содержащий последовательно соединенные фазовращатель, первый балансный амплитудный модулятор и выходной сумматор, ДРУгой вход которого соединен с выходом второго балансного амплитудного модулятора, введены инвертор, .Дв коммутатора, три дешифратора, D-три гер, три постоянных запоминающих блока, реверсивный счетчик, запомин ющий блок, двоичный счетчик, сумматор , преобразователь код-частота, два преобразователя код-аналог, причем выход инвертора соединен с первыми входами коммутаторов., вторые входы которых соединены с одним входом D-триггзра, соединенным с входом первого постоянного запоминающего блока, выход которого через последовательно соединенные сумматор, второй постоянный запоминающий блок и первый преобразователь код-аналог соединен с первым входом второго балансного амплитудного модулятора, второй вход которого и вход фазовращателя являются входом устройства, третьи входы коммутаторов объединены и соединены с входом инвертора и первым входом D-триггера, другой выход которого соединен с четвертыми входами коммутаторов, пятые и шестые входы которых объединены и являются тактовыми ВХОД61МИ, седьмой и восьмой входы одного коммутатора соединены с выходом первого дешифратора, седьмой и восьмой входы второго коммутатора соединены с выходом второго.дешифратора, соединенного с одним входом третьего дешифратора, выход которого соединен с вторым входом D-триггера, выходы коммутаторов соединены с соответствующими входами реверсивного счетчика, выход которого соединен с входами первого и второго дешифраторов и входом запоминающего блока, выход которого через последовательно соединенные преобразователь код-частота и двоичный счетчик соединен с входом третьего дешифратора другим входом сумматора и входом третьего постоянного запоминающего блока, выход которого через второй преобразователь код-аналог соединен с другим входом первого балансного амплитудного модулятора, причем вход инвертора является информационным входом устройства. На фиг.1 изображена структурная электрическая схема предлагаемого ма нипулятора; на фиг.2 - диаграммы, поясняющие работу устройства. Частотный манипулятор содержит инвертор 1, коммутаторы 2 и 3, реверсивный счетчик 4, дешифраторы 5 и -6, запоминающий блок 7, преобразователь 8 код-частота, двоичный счетчик 9, дешифратор 10,В -триггер 11, постоянный запоминающий блок 12, сумматор 13, постоянные запоминающие блоки 14 и 15, преобразователи 16 и 17 код-аналог, балансные амплитудные модуляторы 18 и 19, фазовращатель 20, выходной сумматор 21. Частотный манипулятор работает следующим образом. На информационный вход подается бинарный сигнал (фиг.2 а), несущий и формацию, а на вход тактовой частот ,, - тактовые импульсы с периодо следования не больше, чем Tjo+l- дли тельности самого короткого информационного импульса (где К. - число разрядов двоичного реверсивного сче чика 4). Эти тактовые импульсы подаются на один из четырех входов четырех схем логического умножения, входящих в состав первого и второго коммутаторов 2 и 3, состоящих из элементов . И-ИЛИ. Условно обозначи две схемы И первого коммутатора 2 через А, первые 4 входа, и В - вторые четыре входа, а две схемы И вто рого коммутатора 3 через С и В . Таким образом через первый коммутатор 2 тактовые импульсы могут поступать на вход сложения реверсивного счетч ка 4 , а через второй коммутатор 3 на вход вычитания. Оба коммутатора 2 и 3 управляются дешифраторами 5 и максимальной и минимальной кодовых комбинаций, D -триггером 11 и входны информационным сигналом. В зависимо ти от состояния схемы в целом такто вые, импульсы могут вообще не по ;тупать на входы реверсивного счетчика 4 либо поступать, проходя через одн из четырех схем логического умножения (А,, В, С или D). Кодовые комбинации с выхода реверсивного счетчика 4 поступают на входы дешифраторов 5 и б максимальной (Q)uJ и минимальной(С1 (-nf,) кодовых комбинаций соответственно, а также на адресный вход запоминающего блока 7. Каждому адресу на его входе ставится в соответствие выходной код большей разрядности, решения которого соответствуют требуемому закону скругления фронта частотной манипуляции. Этот код подается на преобразователь 8, с помощью которого осуществляется преобразование его в частоту следования импульсов, которые подаются .на вход двоичного счет-, чика 9. С помощью этого счетчика осуществляется преобразование потока импульсов в двоичный код, период повторения которого пропорционален частоте следования импульсов. Последовательность кодовых слов с выхода двоичного счетчика 9 подается на информационный вход дешифратора 10 помента манипуляции фазы на первую группу входов сумматора постоянного запоминающего блока и на адресные входы. Изменение состояния счетчика 4 под воздействием тактовых импульсов показано на Фиг.25, а изменение частоты следования импульсов с выхода преобразователя 8 - на фиг.2 В. Кодовые комбинации с выхода двоичного счетчика 9 поступают на адресные входы постоянного запоминающего блока 14, таблица истинности которого составлена таким .образом, что последовательность кодовых комбинаций адреса выбирается выходную кодовую последовательность большей разрядности, значения которой пропорциональны мгновенным значениям амплитуды гармонического сигнала на его периоде. Эта последовательность кодовых комбинаций преобразуется в гармонический. сигнал с помощью преобразователя 16. Период повторения кодовых комбинаций адреса постоянного запоминающего блока 14 равен периоду повторения кодовых комбинаций гармонического сигнала на его выходе. Сигнал с инверсного выхода ЙБ -триггера 11 подается на адресный вход постоянного запоминающего блока 12. Если на его адресный вход подается логический О, то выбирается m-разрядное слово KQ, которое подается на вторую группу входов сумматора 13, который осуществляет суммирование текущего кода с первой группы выходов с кодом KQ.Значение Kg выбрано таким образом, что его суммирование с текущим кодом дает положительный сдвиг на 1/4 периода повторения кодовых слов с выхода двоичного счетчика 9. Если на вход адреса постоянного запоминающего блока 12 воздействует логическая 1, то выбирается код К, который, суммируясь с текущим кодом в сумматоре 13, приводит к отрицательному сдвигу (задержке на 1/4 песиола повторения выходного текущего кода сумматора 13. Выходные кодовые слова воздействуют на адресные входы достоянного запоминающего бло ка-15, таблица истинности которого аналогична таблице истинности посто янного запоминающего блока 14. Таким образом на выходе преобразователя 17также формируется гармонический сигнал с фазой, отличной от фазы га монического сигнала. снимаемого с выхода преобразователя 16 . Сигна.лы с его выходов и преобразова теля 17 подаются ,на первые входы ба лансных амплитудных модуляторов 18 и 19. На второй вход балансного амплитудного модулятора 19 подается вы сокочастотный сигнал с частотой «JQ который через фазовращатель 20 на Iy 2 подается на второй вход балансного амплитудного модулятрра 18,Сигнал с выходов обоих балансных ампли тудных модуляторов (БАМ) суммирует ся выходным сумматором 21, выход ко торого является выходом частотного манипулятора. Сигналы на выходе БАМ 18и БАМ 2 19 представлены в виде U,(t)UoSifl () M-W-t , где UQ - амплитуда высокочастотного сигнала; UYY, - амплитуда модулирующего сиг нала; Q - закон изменения частоты мо дулирующего сигнала 4{tl fi(. ; U W Uo9it1 lOo4-U Sin nt)i f . Сигнал U,(t) изображен на фиг.2г а Uij (.-k) на фиг. 23. На выходе частотного манипулятора сигнал имеет вид Ujy/t)4,(i)Ualt)± Uo-LmS Kt , где u(jt(t) частота выходного сигнала. Изменение частоты выходного сигнала приведено на фиг.2 . В зависимости от значения информационного сигнала на выходе манипулятора и состояния 13 -триггера 11 в первый момент после включения устрой ства возможны четыре исходные состоя ния. Первое исходное: инф.- l,fi второе исходное: инф., - О, QI - третье исходное : инф. - 1 (Si - четвертое исходное : инф. , GI - 1. Если в первый момент времени после включения двоичный реверсивный счетчик 4 находится в промежуточ1}ом состоянии (не в Экстремальном), то с выходов дешифраторов 5 и 6 максимальной и минимальной кодовых комбинаций на четвертые и восьмые входы первого и второго коммутатора 2 и 3 соответственно воздействуют логические 1. Допустим, что в момент включения на информационный вход воздействует логическая 1, тогда на пятые входы обоих коммутаторов 2 и 3 воздействует логическая 1, а на первые после инвертирования - логический О. Возможны два исходных состояния 3)-триггера 11: первое - триггер находится в состоянии О, т.е. на выходе Q - О, а на выходе Q - 1; и второе - триггер находится в состоянии 1, т.е. на выходе OL - 1, а на выходе S - О. В первом случае логическая 1 воздействует на второй вход первого коммутатора 2 и на шестой вход второго коммутатора 3, а логический О на шестой вход первого кdм лyтaтopa 2 и на второй вход второго коммутатора 3. Во втором исходном состоянии логические 1 заменяются на логические О на соответствующих входах обоих коммутаторов и наоборот. При первом исходном сост9янии импульсы тактовой частоты проходят через схему совпадений D и, следовательно, воздействуют на вычитающий вход реверсивного счетчика 4, который последовательно изменяет свои состояния. При достижении состояния (нулевое состояние) срабатывает дешифратор 6 минимального кодового состояния, и логическая 1 на четвертом и восьмом входах второго коммутатора 3 заменяется на логический О, и тем самым поступление тактовых импульсов на реверсивный счетчик 4 блокируется. Логический О с выхода дешифратора б подается также на инверсный вход стробирования дешифратора 10 момента манипуляции фазы, на информационный вход которого продолжают поступать кодовые комбинации с выхода двоичного счетчика 9. Для уменьшения внеполосных излучений манипуляцию фазы модулирующего сигнала на выходе преобразователя 17 целесообразно производить при его переходе через нулевой уровень напряжения. С этой целью, если выходной код двоичного счетчика 9 разрядный, дешифратор 10 по информационному входу настраивается на уп. кодовую комбинацию. Таким образом вход стробирования дешифратора 10 выполняет функцию локализатора момента манипуляции фазы в области минимальной частоты следования импульсов на выходе преобразователя В. По импульсу с выхода дешифратора 10, поступающему на вход записи D -триггера 11, триггер устанавливается в состояние, соответствующее логическому уровню на его информац онном входе, т.е. в данном случае в состояние логической 1. Тем самым происходит манипуляция фазы сигнала с выхода преобразователя 17 на + п/2. Открывается схема логического умножения В, и тактовые импульсы начинают наступать на вход сложения реверсивного счетчика 4, а значит .частота выходного сигнала частотного манипулятора начинает возрастать от uUo до ШО+АШ (интервал ftQiil ;} на фиг.2(Ч- в. Начиная с этого момента, мгновённая частота выходного сигнала частотного манипулятора полностью определяется информационным сигналом и заданным законом изменения .частоты. При достижении реверсивным счетчиком 4 состояния (единичное состояние) срабатывает дешифратор 5 и, логические 1 на четвертом и восьмом входах первого коммутатора 2 заменяются на логические О, тем самым блокируя.поцтупление тактовых импульсов на счет чик 4 . На выходе частотного манипулятора формируется верхнее значение частоты оОр . Д W (момент -Ь на фиг .20- ej, которое остается до тех пор, пока логическая 1 на информационном входе не сменится на логический О (момент Ц на фиг.2«1 -е) После этого открывается схема совпадений С, и тактовые импульсы начинают поступать на вход вычитания реверсивного счетчика, уменьшая тем самым частоту следования тактовых им пульсов с выхода преобразователя 8, а значит и частоту гармонических модулирующих сигналов на выходах npe образователей 16 и 17. частота выход ного сигнала манипулятора уменьшается от верхнего значения ии + дш до величины несколько большей, чем tu которая определяется минимальной час тотой следования тактовых импульсов с выхода преобразователя 8. Для надежной работы частотного манипуля тора должно выполняться условие min nvL4 1 точт „,„ ми нимальная частота следования импульсов с выхода прейбраэователя 8. В этом случае достригается надежная локализация момента манипуляции фазы дешифратором 10., После выделения момента фазовой манипуляции импульсов выхода дешифратора 10 D -триггер 11 устанавливается в состояние код k-o на выходе постоянного запоминающего блока 12 заменяется на Кg и про исходит манипуляция фазы на - п/2 в сигнале на выходе КАП2 17 (момент t на фиг.2 q - в). Тактовые импульсы начинают поступать через схему логического умножения А на вход сложения ре версивного счетчика 4, тем самым частота на выходе манипулятора умень шается, по заданному закону, от шо до iUo-A(jD (интервал tj , на фиг.2 а-е. Затем по достижении происходит блокировка тактовых импульсов, и схема устанавливается / в устойчивое состояние, а на выходе манипулятора устанавливается частота a)-uLo (момент ь на фиг.2с(е7 Это устойчивое-состояние сохраняется до замены логического О на йнФормаци- онном входе на логическую Далее процесс повтосяется в описанном порядке . Таким образом, поедложенное устройство позволяет подавлять внеполосные излучения путем скругления фронтов манипуляции по любому выбранному закону, повышая помехозащищенность. Формула изобретения Частотный манипулятор, содержащий последовательно соединенные фазовращатель, первый балансный амплитудный модулятор и выходной сумматор, другой вход которого соединен с выходом второго балансного амплитудного модулятора, отличающийся тем, что, с целью повышения помехозащищенности путем подавления внеполосных излучений, введены инвертор, два коммутатора, три дешифратора, D-триггер, три постоянных запоминающих блока, реверсивный счетчик, запоминающий блок, двоичный счетчик, сумматор, преобразователь код-часто- . та, два преобразователя код-аналог, причем выход инвертора соединен с первыми входами коммутаторов, вторые входы которых соединены с одним входом D- триггера, соединенным с входом первого постоянного запоминающего блока, выход которого через последовательно соединенные сумматор, второй постоянный запоминающий блок и первый преобразователь код-аналог соединен с первым входом второго балансного амплитудного модулятора, второй вход которого и вход фазовращателя являются входом устройства, третьи входы коммутаторов объединены и соединены с входом инвертора и первым входом В -триггера, другой выход которого соединен с четвертыми входами коммутаторов, пятые и шестые входы которых объединены и являются тактовыми входами, седьмой и восьмой входы одного коммутатора соединены с выходом первого дешифратора,седьмой и восьмой входы второго коммутатора соединены . с выходом второго дешифратора, соединенного с одним входом третьего дешифратора, выход которого сюединен с вторым входом И -трих.гера, выходы коммутаторов соединены с соответствующими входами реверсивного счетчика, выход которого соединен с входами первого и второго дешифраторов и входом Зсшоминающего блока.

выход которого через последовательно соединенные преобразователь код-частота и двоичный счетчик соединен с входом третьего дешифратора, другим входом сумматора и входом третьего постоянного запоминающего блока, выход которого через второй преобразователь код-аналог соединен с другим входом первого балансного амплитудного модулятора, причем вход инвертора является информационным входом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР .№ 364069, кл. Н 03 С 3/00, 1970 Гпрототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый модулятор | 1978 |

|

SU771783A1 |

| Формирователь сигналов с угловой модуляцией | 1985 |

|

SU1241411A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1994 |

|

RU2083995C1 |

| Фазовый модулятор | 1986 |

|

SU1388974A2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1996 |

|

RU2099739C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1998 |

|

RU2124221C1 |

| СПОСОБ ОБНАРУЖЕНИЯ ЦЕЛЕЙ ИМПУЛЬСНОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИЕЙ И РАДИОЛОКАЦИОННАЯ СТАНЦИЯ ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2270461C2 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| Частотный модулятор | 1984 |

|

SU1160589A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

Авторы

Даты

1981-10-15—Публикация

1980-01-11—Подача