второго триггера, второй вход которого соединен с установочным входом устройства, а выход является соответствующим выходом идентификации устройства, введен элемент ИЛИ, причем i-й вход элемента ИЛИ соединен с вторым выходом второго триггера г-го канала и вторым входом первого триггера того же канала, а выход подключен к первым входам элементов И, вторые входы которых являются соответствующими входами синхронизации устройства, а выходы соединены с третьими входами вторых триггеров одноименных каналов (,M).

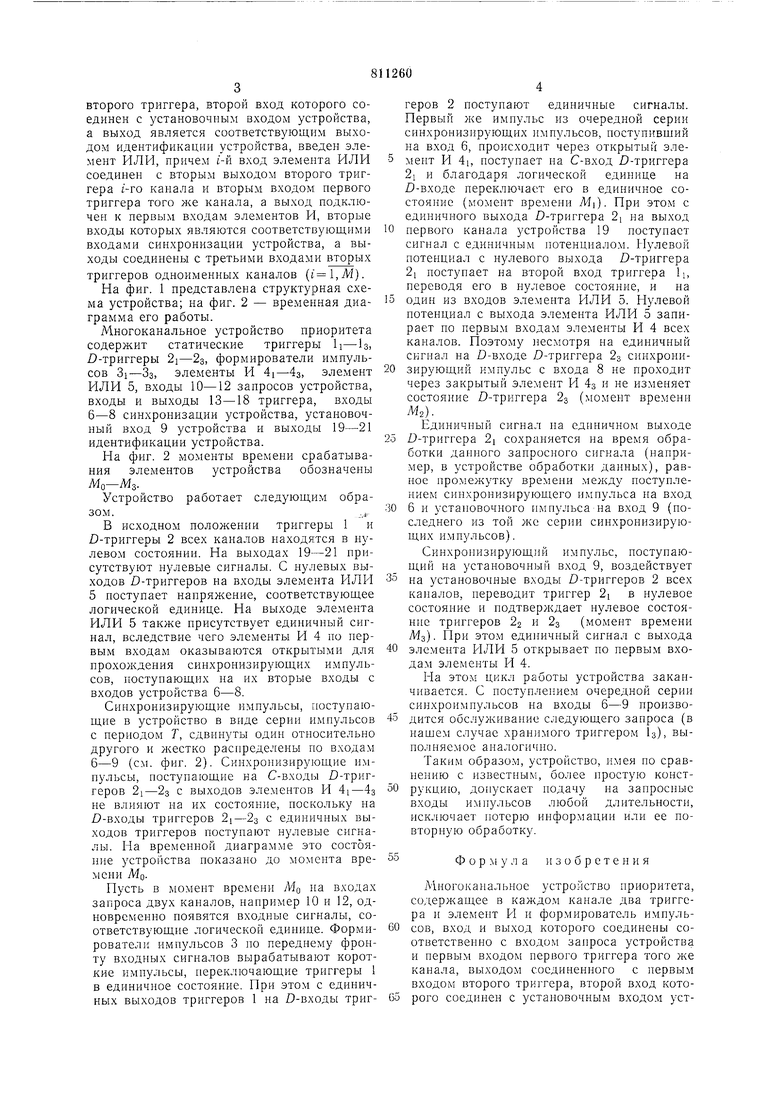

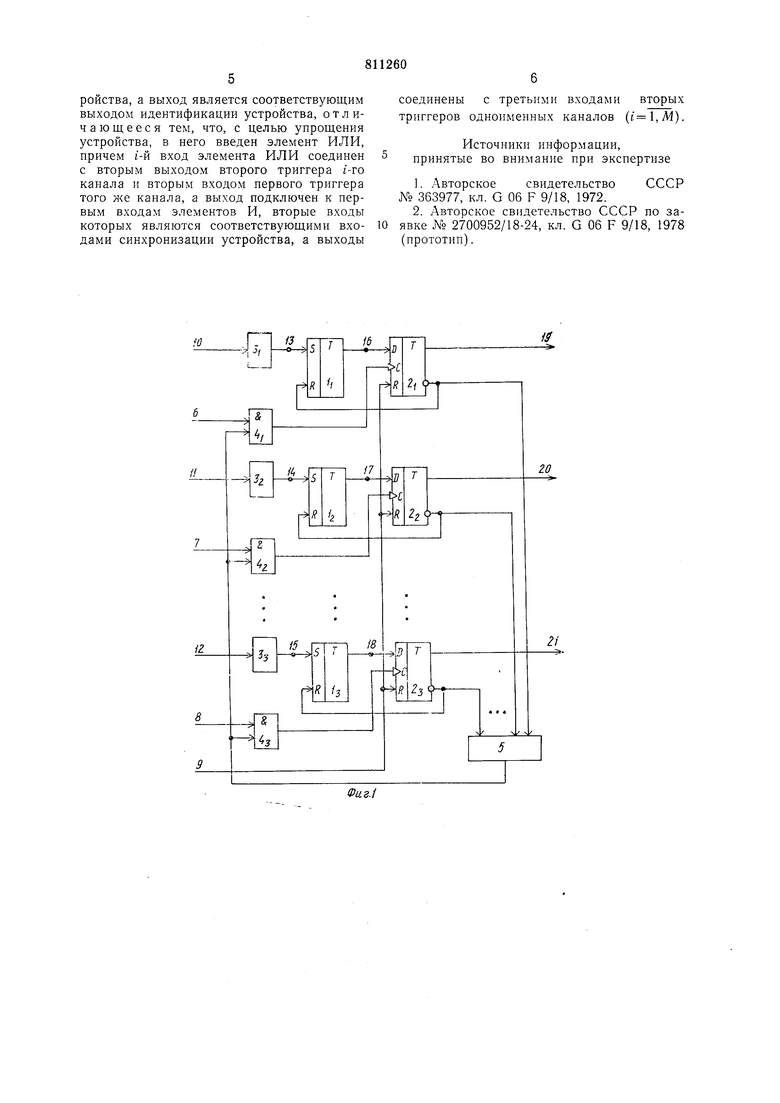

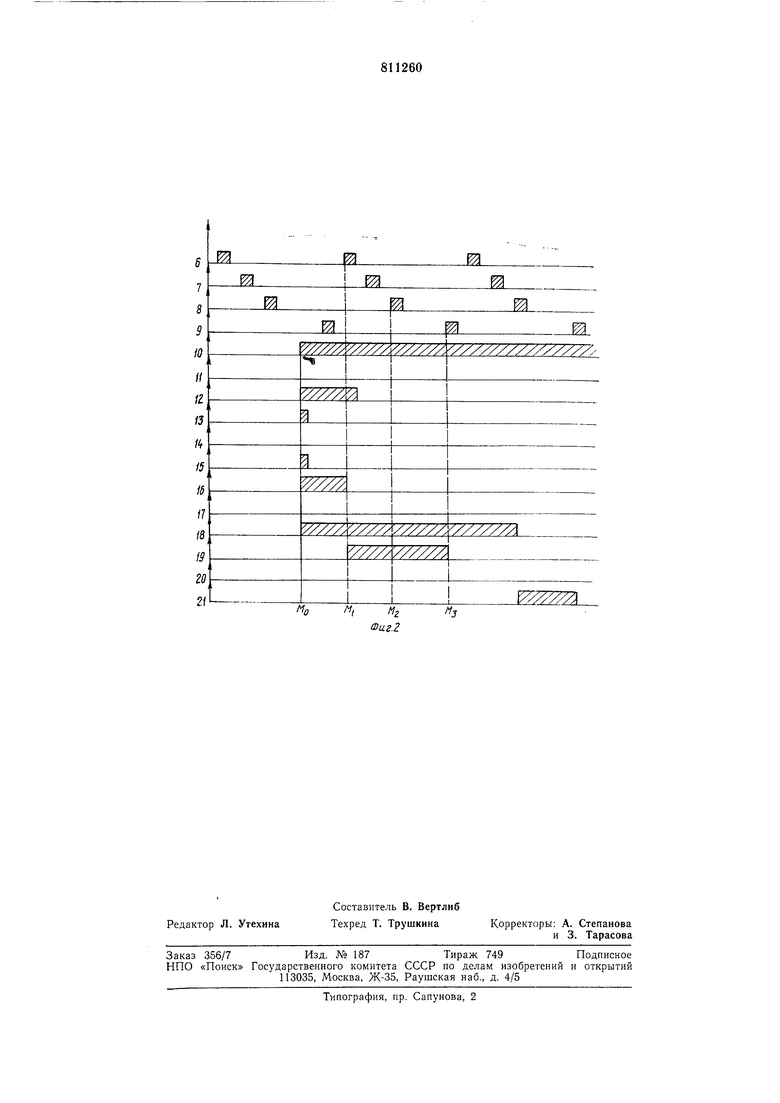

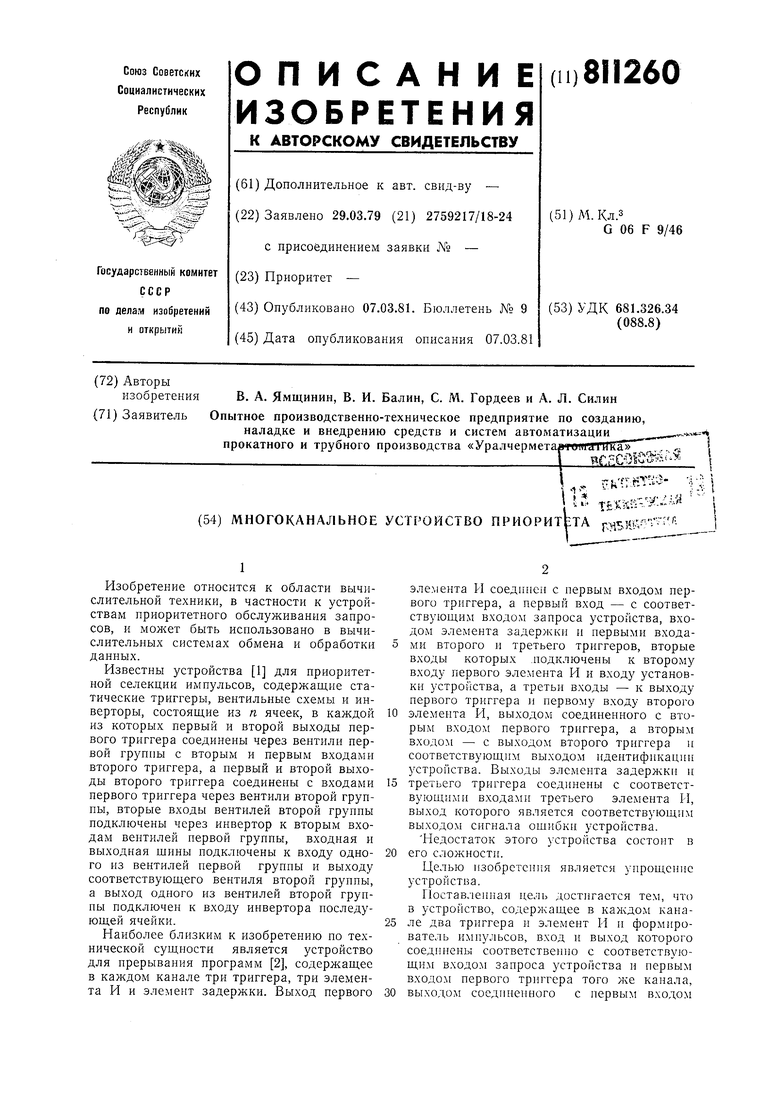

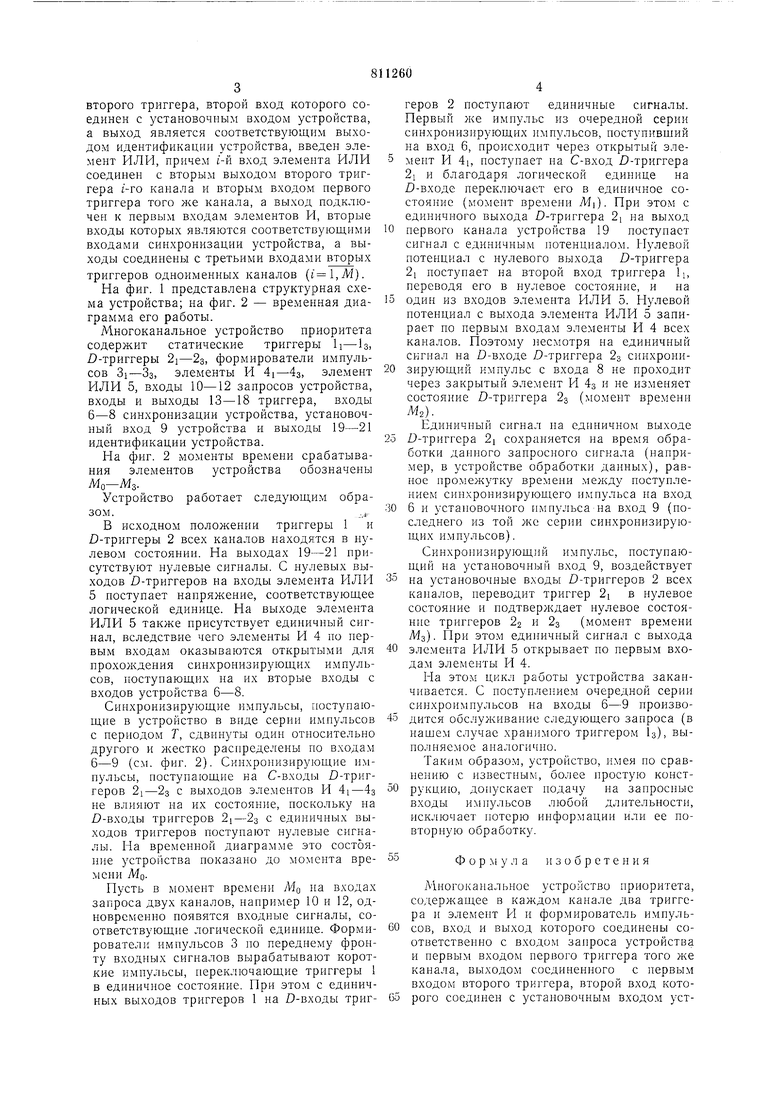

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временная диаграмма его работы.

Многоканальное устройство приоритета содержит статические триггеры li-Ь, D-триггеры 2i-2з, формирователи импульсов 3i-Зз, элементы И , элемент ИЛИ 5, входы 10-12 запросов устройства, входы и выходы 13-18 триггера, входы 6-8 синхронизации устройства, установочный вход 9 устройства и выходы 19-21 идентификации устройства.

На фиг. 2 моменты времени срабатывания элементов устройства обозначены Мо-М,.

Устройство работает следующим образом.

В исходном положении триггеры 1 и D-триггеры 2 всех каналов находятся в нулевом состоянии. На выходах 19-21 присутствуют нулевые сигналы. С нулевых выходов D-триггеров на входы элемента ИЛИ 5 поступает напряжение, соответствующее логической единице. На выходе элемента ИЛР1 5 также присутствует единичный сигнал, вследствие чего элементы И 4 по первым входам оказываются открытыми для прохождения синхронизирующих импульсов, поступающих на их вторые входы с входов устройства 6-8.

Синхронизирующие импульсы, поступающие в устройство в виде серии импульсов с периодом Т, сдвинуты один относительно другого и жестко распределены по входам 6-9 (см. фиг. 2). Синхронизирующие импульсы, поступающие на С-входы D-триггеров 2i-2з с выходов элементов И 4i-4з не влияют на их состояние, поскольку на 1)-входы триггеров 2i-2з с единичных выходов триггеров поступают нулевые сигналы. На временной диаграмме это состояние устройства показано до момента времепп Mfj.

Пусть в момент времени MQ на входах запроса двух каналов, например 10 и 12, одновременно появятся входные сигналы, соответствующие логической единице. Формирователи импульсов 3 по переднему фронту входных сигналов вырабатывают короткие импульсы, переключающие триггеры 1 в единичное состояние. При этом с единичных выходов триггеров 1 на /)-входы триггеров 2 поступают единичные сигналы. Первый же импульс из очередной серии синхронизирующих пмпульсов, поступивщий на вход 6, происходит через открытый элемент И 4i, поступает на С-вход /)-триггера 2i и благодаря логической единице на /)-входе переключает его в единичное состояние (момент времени MI). При этом с единичного выхода D-триггера 2i на выход

первого канала устройства 19 поступает сигнал с единичным потенциалом. Нулевой потенциал с нулевого выхода /З-триггера 2i поступает на второй вход триггера Ц, переводя его в нулевое состояние, и на

один из входов элемента ИЛИ 5. Нулевой потенциал с выхода элемента ИЛИ 5 запирает по первым входам элементы И 4 всех каналов. Поэтому несмотря на единичный сигнал на Д-входе D-триггера 2з синхронизирующий импульс с входа 8 не проходит через закрытый элемент И 4з и не изменяет состояние Л-триггера 2з (момент времени М,).

Единичный сигнал на единичном выходе

D-триггера 2i сохраняется на время обработки данного запросного сигнала (например, в устройстве обработки данных), равное промежутку времени между поступлением синхронизирующего импульса на вход

6 и установочного импульса-на вход 9 (последнего из той же серии синхронизирующих импульсов).

Синхронизирующий импульс, поступающий на установочный вход 9, воздействует

на установочные входы /)-триггеров 2 всех каналов, переводит триггер 2; в нулевое состояние и подтверждает нулевое состояние триггеров 22 и 2з (момент времени Мз). При этом единичный сигнал с выхода

элемента ИЛИ 5 открывает по первым входам элементы И 4.

На этом цикл работы устройства заканчивается. С поступлением очередной серии синхроимпульсов на входы б-9 производится обслуживание следующего запроса (в нашем случае хранимого триггером 1з), выполняемое аналогично.

Таким образом, устройство, имея по сравнению с известным, более простую конструкцию, допускает подачу на запросные входы импульсов любой длительности, исключает потерю информации или ее повторную обработку.

Формула изобретения

Многоканальное устройство приоритета, содержащее в каждом канале два триггера и элемент И и формирователь импульсов, вход и выход которого соединены соответственно с входом запроса устройства и первым входом первого триггера того же канала, выходом соединенного с первым входом второго триггера, второй вход которого соединен с установочным входом устройства, а выход является соответствующим выходом идентификации устройства, отличающееся тем, что, с целью упрощения устройства, в него введен элемент ИЛИ, причем г-й вход элемента ИЛИ соединен с вторым выходом второго триггера f-ro канала и вторым входом первого триггера того же канала, а выход подключен к первым входам элементов И, вторые входы которых являются соответствующими входами синхронизации устройства, а выходы

соединены с третьими входами вторых триггеров одноименных каналов (,Л1).

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 363977, кл. G 06 F 9/18, 1972.

2.Авторское свидетельство СССР по заявке № 2700952/18-24, кл. G 06 F 9/18, 1978

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1985 |

|

SU1302280A1 |

| Многоканальное устройство для управления очередностью запросов | 1982 |

|

SU1061143A1 |

| Многоканальное устройство приоритета | 1979 |

|

SU822185A1 |

| Система электропитания постоянным током | 1990 |

|

SU1818660A1 |

| Многоканальное устройство для обслуживания запросов | 1985 |

|

SU1290326A1 |

| Многоканальное устройство связи для вычислительной системы | 1980 |

|

SU943695A1 |

| Система электропитания | 1990 |

|

SU1758768A1 |

| Многоканальная система электропитания постоянным током | 1989 |

|

SU1758771A1 |

| Устройство циклического приоритета | 1990 |

|

SU1805468A1 |

| Многоканальное устройство для управления очередностью обработки запросов | 1980 |

|

SU868759A1 |

Авторы

Даты

1981-03-07—Публикация

1979-03-29—Подача