(5) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СВЯЗИ ДЛЯ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU898413A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU962907A1 |

| Устройство связи для вычислительной системы | 1981 |

|

SU983699A1 |

| Многоканальное устройство связи для вычислительной системы | 1982 |

|

SU1083174A1 |

| Устройство связи для вычислительнойСиСТЕМы | 1979 |

|

SU802957A1 |

| Устройство связи для вычислительной системы | 1980 |

|

SU924694A1 |

| Устройство для сопряжения модулейВычиСлиТЕльНОй СиСТЕМы C KOHTPO-лЕМ | 1978 |

|

SU807258A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1042008A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в однопроцессорных, мульти- процессорных и распределенных вычислительных системах кольцевой структуры.

Известно устройство связи для вычислительной системы, содержащее блок синхронизации и группу каналов, каждый из которых включает буферный регистр, регистр адреса, приемный и передающий регистры, управляющий регистр, распределитель импульсов, узел синхронизации, блок сравнения, узел коммутации управляющих сигналов П .

Недостаток этого устройства состоит в низком быстродействии.

Наиболее близким к изобретению по технической сущности и достигаемому эффекту является многоканальное устройство связи, содержащееблок тактовых импульсов, а в каждом канале - первый и второй приемные,

первый и второй передающие регистры, первый и второй элементы ИЛИ, распределитель импульсов, узел коммутации управляющих сигналов, блок сравнения, первый и второй буферные регистры, управляющий регистр, узел синхронизации, регистр признака передачи, блок формирования признака обмена и регистр адреса Г2,

to

Недостатком этого устройства является низкое быстродействие, так как из-за отсутствия предварительного анализа физического расположения несмежных вычислительных модулей

15 друг относительно друга перекрестные обмены между несмежными модулями } в худшем случаевыполняются за чремя цикла магистрали (произведение числа подключенных модулей за время

20 такта магистрали без времени такта магистрали.

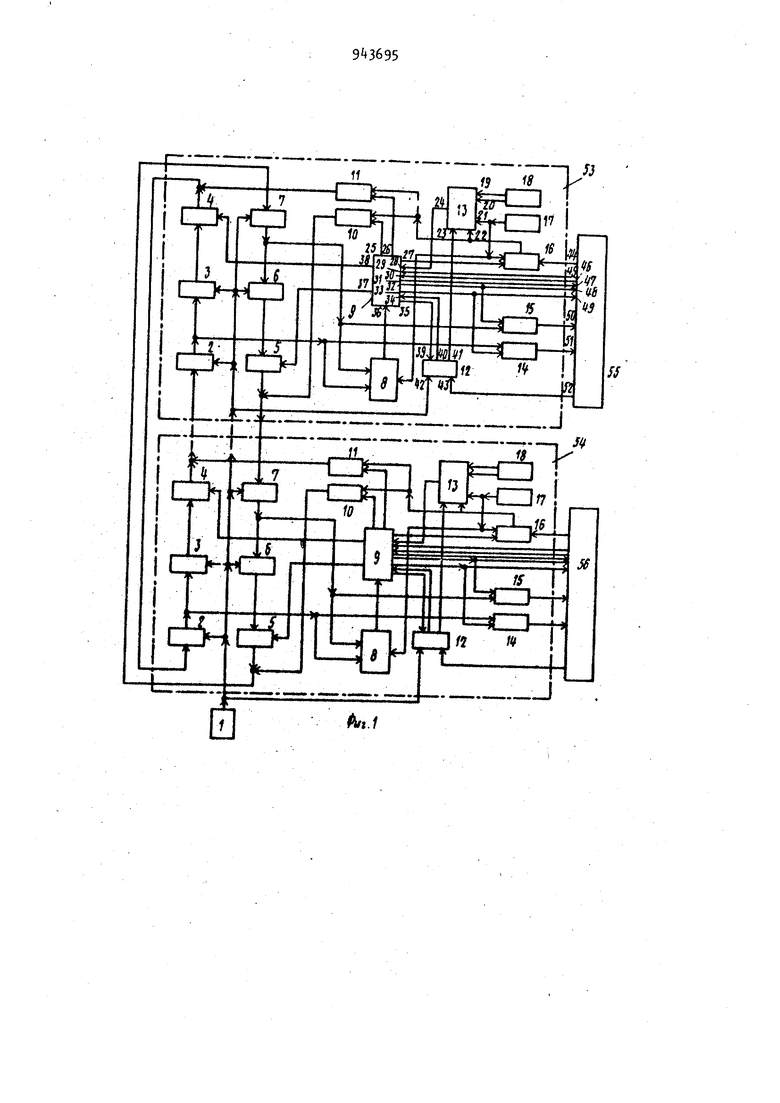

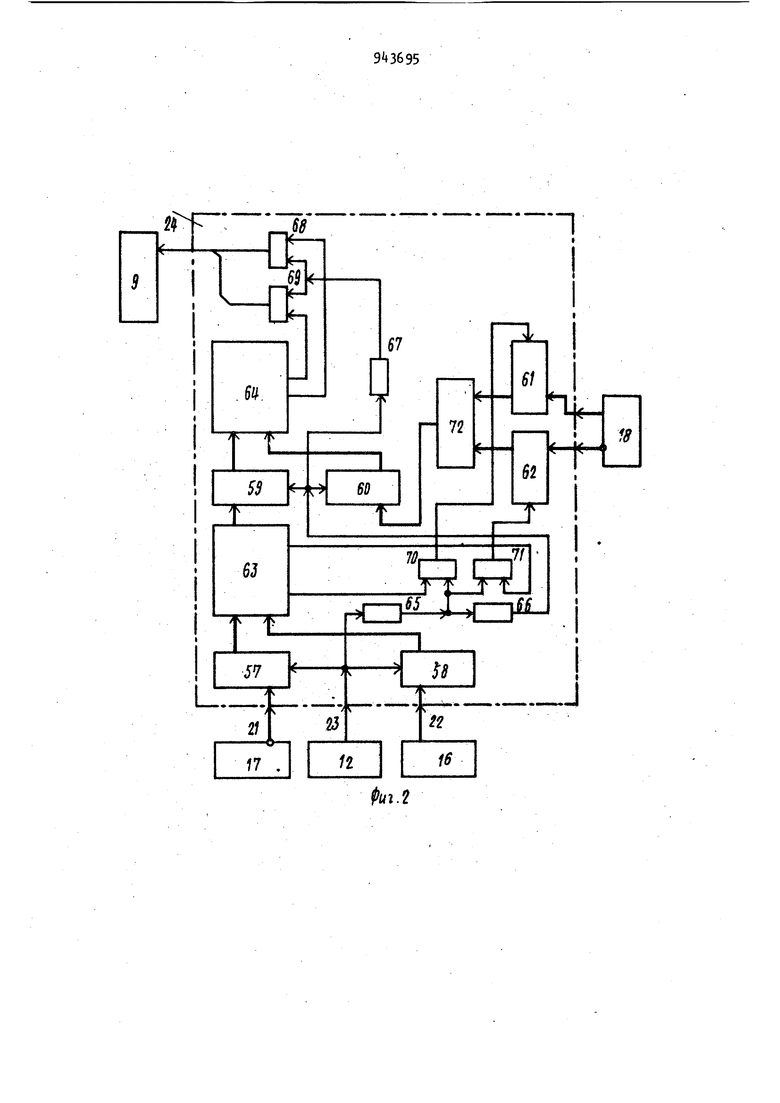

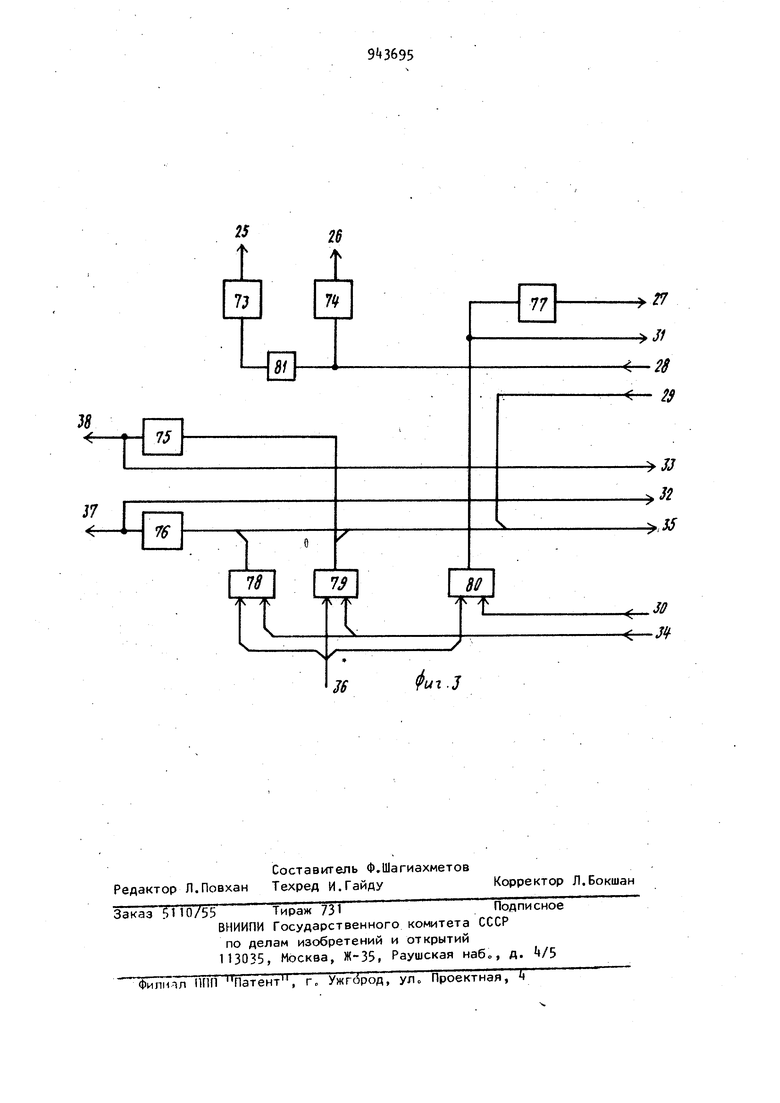

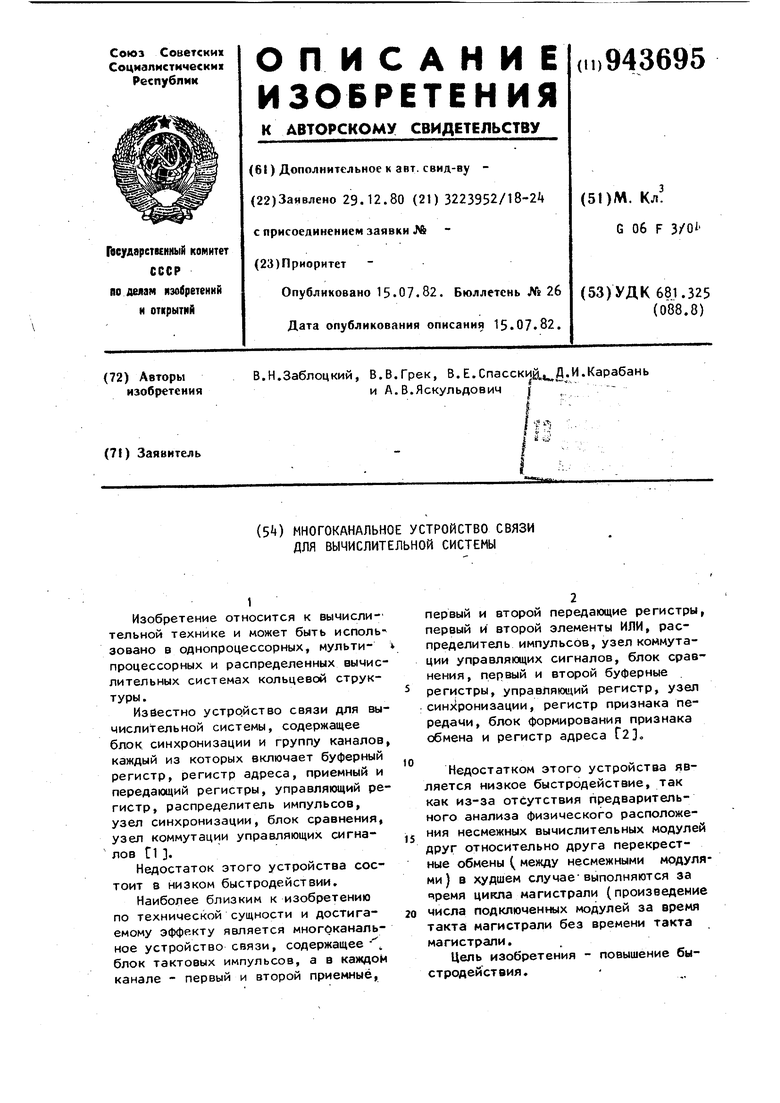

Цель изобретения - повышение быстродействия. Поставленная цель достигается те что в многоканальное устройство связи для вычислительной системы, содер жащее объединенные в кольцо каналы и генератор тактовых импульсов, а в каждом канале - два приемных реги ра, два передающих регистра, четыре группы элементов И, схему сравнения, блок управления, регистр состоя ния, регистр адреса и три буферные регистра, причем выход первого приемного регистра канала соединен с ин формационными входами первого передающего регистра канала, первого буферного регистра канала, с первым информационным входом схемы сравнени канала, выход первого передающего регистра канала соединен с информационным входом первой группы элементов И канала, выход второго приемного регистра канала соединен с информационными входами второго передающего регистра канала, второго буферного регистра канала, со вторым информационным входом схемы сравнения канала, выход второго передающего регистра канала соединен с информационным входом элементов И второй группы канала, выход регистра адреса канала соединен с третьим информационным входом схемы с|эавнения канала и синформационным входом третьего буферного регистра канала, выход третьего буферного регистра ка нала соединен с информационными вход ми элементов И третьей и четвертой групп канала, с первого по пятый выходы разрешения выдачи блока управ ления канала соединены с управляющими входами элементов И соответственно первой - четвертой групп канала и третьего буферного регистра канала, вход завершения приема канала, запросный и установочный входы канал соединены соответственно со входом завершения приема блока управления канала, с запросным входом блока управления канала и с первым установоч ным входом регистра состояния сигнала, первый выход разрешения приема блока управления канала соединен с управляющим входом первого буферного регистра канала и с первым управляющим выходом канала, второй выход разрешения приема блока управления канала соединен с управляющим входом второго буферного регистра канала и со вторым управляющим выходом канала, выход удовлетворения 5 запроса блока управления канала является третьим управляющим выходом канала, выход схемы сравнения канала соединен с запускающим входом блока управления канала, признаковой вход и гасящий выход блока управления канала соединены соответственно с первым выходом и вторым установочным входом регистра состояния канала, синхронизирующие входы приемных, передающих регистров и регистров состояния каналов соединены с выходом генератор: тактовых импульсов, выход элементов И первой и четвертой групп канала соединен со входом первого приемного регистра последующего канала, вход второго приемного регистра канала соединен с выходами элементов И второй и третьей групп предыдущего канала, выходы первого и второго буферных регистров канала и вход третьего буферного регистра канала являются соответственно первым, вторым информационными выходами канала и информационным входом канала, в каждый канал введены блок формирования направления записи и регистр константы, причем первый - четвертый информационные и управлякзщий входы и. выход блока формирования направления записи канала соединены соответственно с пряка 1м и инверсным выходами регистра константы канала, с выходами регистра адреса канала и третьего буферного регистра канала со вторым выходом регистра состояния канала и со входом переключения магистралей блока управления канала. Поставленная цель достигается также тем, что блок формирования направления записи содержит два сумматора, шесть групп элементов И, группу элементов ИЛИ, четыре элемента И, три элемента задержки, причем управляющий вход блока соединен с управляющими входами элементов И первой и второй групп и со входом первого элемента задержки, выход которого соединен с первыми входами первого и второго элементов И и со входом второго элемента задержки, выход которого соединен с управляющими входами элементов И третьей и четвертой групп и со входом третьего элемента задержки, выход которого соединен с первыми входами третьего и четвертого элементов И, выходы которых соединены с выходом блока, первый и второй информационные онными входами элементов И соответственно пятой и шестой групп, выходы которых через группу элементов ИЛИ соединены с информационным входом элементов И четвертой группы, выход которой и выход элементов И третьей группы соединены соответственно с первым и вторым входами первого сумматора, первый и второй выходы которого соединены со вторыми входами соответственно третьего и четвертого элементов И, третий и четвертый информационные входы блока соединены с информационными входами элементов И соответственно первой и второй групп, выходы которых соединены соответственно с первым и вторым входами второго сумматора, информационный и первый, второй управляющие выходы которого сое динены соответственно с информационным входом элементов И, третьей группы и с вторыми входами первого и второго элементов И, выходы первого и второго элементов И соединен с управляющими входами элементов И соответственно пятой и шестой групп Поставленная цель достигается также тем, что блок управления канала содержит пять D-триггеров, три элемента И и элемент задержки, причем запускающий вход блока соединен с первыми входами первого, второго и третьего элементов И, признаковый вход блока соединен со вторыми входами первого и.второго элементов И, запросный вход блока соединен со вторым входом третьего элемента И, выход которого является выходом удовлетворения запроса блока, и с D-входом первого D-триггера, выход которого является пятым выходом разрешения выдачи блока, вход завершения приема блока, выход первого и второго элементов И блока являются гасящим выходом блока, вых первого элемента И соединен с D-вхо дом второго О-триггера, выход кото рого является вторым входом разреше ния выдачи блока и вторым выходом разрешения приема блока, выход вто рого элемента И соединен с О-входом третьего О-триггера, выход которого является первым выходом разрешения выдачи блока и первым выходом разрешения приема блока, вход переключения магистрали блока соединен с О-ходом четвертого 0-тригдом пятого О-триггера, выходы пятого и четвертого D-триггеров являются соответственно третьим и четвертым выходами разрешения выдачи блока. На фиг. 1 .представлена структурная схема устройства; на фиг. 2 структурная схема блока формирования направления записи-, на фиг. 3 - вариант структурной схемы блока управления канала. Устройство связи содержит (фиг. 1) генератор тактовых импульсов 1, а в каждом канале - первый приемный регистр 2, первый передающий регистр 3, первую k и вторую 5 группы элементов k, вторые передающий 6 и приемный 7 регистры, схему сравнения 8, блок управления 9, третью 10 и четвертую 11 группы элементов И, регистр состояния 12, блок 13 формирования направления записи первый Т), второй 15 и третий 16 буферные регистры, регистр адреса 17, регистр константы 18, первый 19, второй 20, третий 21, четвертый 22 информационные входы, управляющий вход 23 и выход блока формирования направления записи, входы и выходы блока управления: 25 третий выход разрешения выдачи, 2б - четвертый выход разрешения выдачи, 27 - пятый выход разрешения выдачи, 28 - вход пере-, ключения магистралей, 29 - вход завершения приема, 30 - запросный вход, 31- выход удовлетворения запроса, 32- второй выход разрешения приема, 33- первый выход разрешения приема, З - признаковый вход, 35 гасящий выход, 36 - запускающий вход, 37 второй выход разрешения выдачи, 38 первый выход разрешения выдачи; входы и выходы регистра состояния; 39 первый установочный вход, 40, Ц первый и второй выходы, i2 - синхронизирующий вход, второй установочный вход; входы и выходы канала; k - информационный вход, 45 вход завершения приема, +6 - запросный вход, , +8 - первый и второй управляющие выходы, 49 - третий управляющий выход первый 50 и второй 51 информационные выходы, 52 - устачовочный вход. Позициями 53, 5 обозначены каналы устройства позициями 55, 56 - модули вычислительной системы. Блок формирования направления записи сЪдержит (фиг. 2). первую 57 7 вторую 58, третью 59, четвертую 60, пятую 61, шестую 62 группы элементо И, сумматоры 63, 6, элементы задер 65-67, третий 68, четвертый 69 пер вый 70, второй 71 элементы И, групп 72 элементов ИЛИ. Остальные обозначения аналогичны обозначениям фиг. Блок управления может быть выпол нен например в виде .(фиг. геров 73-77, элементов И 78-80, эле мента НЕ 81. Остальные обозначения аналогичны обозначениям на фиг. 1. Генератор 1 тактовых импульсов предназначен для синхронизации работы устройства. Формат слова информации, пересылаемого между приемными и передающими регистрами, имеет следующие поля: -признак занятости слова ин1формации (Занято Свободно); адрес получателя; адрес отправителя; данные (собственно информация, адрес ячейки памяти). Первая k, вторая 5, третья 10 и четвертая 11 гру пы элементов и канала содержат элементы с выходами на три состояния, например ИС 155 ЛП8 , Когда на управляющих входах групп 4, 5,10 и 11 элементов И низкий уровень напряжения,на информационных выходах этих групп присутствует 14 формация, поступающая на их формационные входы (состояния О или 1). Когда на управляющих входах групп Ц, 5, 10 и 11 элементов И высокий уровень напряжения, то на информаци онных выходах этих групп высокоимпеданское состояние (третье состояние) независимо от состояния на их информационных входах Это позволяет объединить эти группы элемен тов и по информационным выходам и подключать к общей линии связи, пра тически не оказывая влияния на прохождение информации по линии связи. Схема сравнения 8 содержит два элемента НЕ и два узла поразрядного сложения по модулю 2 и предназначена для сравнения адресов получателе поступающих на первые и вторые информационные входы с адресами, соде жащимися в регистре 17 адреса. Регистры состояния содержат элементы занесения, сброса, первые, вторые и третьи триггеры, указывающие состояние (Занято Свободно первых, вторых и третьих буферных р гистров Ut и 15 и 16 соответственно Блок 13 .предназначен для формирования признака направления записи, т.е. записи в первую или вторую магистраль при передаче слов информации (режим Запись) из модулей вь(числительной системы. Формирование осуществляется на основании анализа результата выполнения арифметических операций над следующими слагаемыми: адресами отправителя, адресами получателя и константы. Передача слов информации в первой магистрали осуществляется слева направо (первый приемный регистр 2, первый передающий регистр 3, первая группа 4 элементов И, а во второй магистрали - справа налево (второй приемный регистр 7, второй передающий регистр 6 вторая группа 5 элементов и). Сумматор 63 представляет собой сумматор комбинационного типа, содержит набор элементов И, ИЛИ, НЕ и предназначен для сложения по модулю 2 обратного кода адреса отправителя (со знаковым разрядом) с адресом получателя (со знаковым разрядом). Сумматор 6k структурно аналогичен сумматору 63 и предназначен для сложения по модулю 2 суммы, полученнай в сумматоре 63 с или обратным кодом (со знаковым разрядом) константы, поступающей из регистра константы 18, Первые и вторые буферные регистры 14 и 15 (фиг, 1) содержат триггеры, узлы занесения и выдачи информации и предназначены для приема слов информации соответственно из первой и второй магистралей (из первого и второго приемных регистров 2 и 7 соо ветственно), их хранения и переда чи в модули вычислительной системы. Третьи буферные регистры 16 содержат триггеры, узлы занесения и выдачи информации и предназначены для приема информации (адреса получателя, данные) из модулей вычислительной системы, адресов отправителей из регистров 17 адреса и передачи сформированных слов информации в первую или вторую магистрали через четвертую 11 или третью 10 группы элементов И. Регистры 17 адреса, предназначенные для хранения адресов отправителей, содержат триггеры, узлы сброса и занесения информации с пульта управления (на чертеже не показан). Адреса отправителей хранятся в регистре 17 адреса в прямом коде. Знаковый разряд регистров 17 адреса равен нулю. Единичные выходы регистров 17 адреса (без знакового разряда) подключены к первым информационным входам третьих буферных регистров 16 и тре тьим информационным входам схем сра нения 8, а нулевые выходы регистров 17 адреса (адреса отправителей со знаковым разрядом в обратном коде) подключены ко вторым информационным входам блоков 13. Регистр 18 константы содержит триггеры, узлы сбро са и занесения информации с пульта управления (на чертеже не показан) и предназначен для хранения констан ты, равной М/2 в двоичном представлении в прямом коде, где М - количество модулей вычислительной системы. Знаковый разряд регистра 18 константы равен нулю. Единичные и нулевые выходы регистра 18 константы (прямой и обратный коды константы со знаковым разрядом) подключены соответственно ко второму и первому информационным входам блока 13. В качестве модулей 55 и 5б вычислительной системы могут использоватьс процессоры, блоки памяти и т,п. Работу устройства связи для вычислительной систекы будем рассматривать на примере работы некоторого К-го канала устройства совместно с генератором 1 тактовых импульсов. По пуску устройства генератор 1 тактовых импульсов начинает вырабатывать тактовые импульсы, под управ лением которых в устройстве начинают циркулировать свободные слова информации. По каждому тактовому им пульсу происходит передача слов информации между соседними каналами устройства По переднему фронту тактового импульса информация с информационных выходов первой группы k элементов И канала К+1 (либо четвертой группы 11 элементов И канала К+1 и информационных выходов второй группы 5 элементов И канала К-1 (ли бо третьей группы 10 элементов И ка ла К-1 переписывается соответственн в первый приемный регистр 2 канала К и второй приемный регистр 7 канала К. По заднему фронту тактового импульса информация из первого приемного регистра 2 канала К и второго приемного регистра 7 канала К , переписывается соответственно впервый передающий регистр 3 канала К и во второй передающий регистр 6 канала К. Каждый К-ый канал обмена мо- . жет работать в двух режимах: Чтение ; Запись Режим .Чтение предназначен для приема информации,адресованной К-ому модулю (К-ому каналу) и передачи ее в К-ый модуль вычислительной системы. По переднему фронту тактово- го импульса информация из (К+1)-ого канала и (K-l)-oro канала записывается соответственно в первый и второй приемные регистры 2 канала К Vi 7канала К. По заднему фронту тактового импульса информация.из первого и второго приемных регистров 2 канала К и 7 канала К переписывается соответственно в первый и второй передающие регистры 3 канала К и 6 канала К. По приему информации в первый и второй приемные регистры 2 канала К и 7 канала К схема сравнения 8 канала К анализирует поля адреса получателя в принятых словах информации на равенство адресу К-ого модуля вычислительной систеия, хранящемуся в регистре 17 канала К, и поля занятости слова информации. В результате анализа схема сравнения 8канала К выдает сигналы: Свободно 1, Свободно 2, 1, Равно 2. В режиме Чтения используются два последних сигнала Сигнал Равно 1 означает, что в первом приемном регистре 2 канала К записана информация, адресованная данному модулю К вычислительной системы. Сигнал Равно 2 означает, что во втором приемном регистре 7 канала К записана информация, адресованная данному модулю К вычислительной системы. По сигналу Равно 1 и состоянию Свободно первого триггера регистра, состоянию Свободно первого триггера регистра состояния 12 канала К блок управления 9 канала К вырабатывает сигналы, поступающие в регистр состояния канэла , первую группу (элементов И канала К, первый буферный регистр 1 канала К, и сигнал Принять 1, поступающий на выход на канала К. По сигналу из блока управления 9 канала К в первый регистр 1 канала К записывается информация (адрес отправителя, данные ) из первого приемного регистра 2 канала К. По высокому уровню напряжения сигнала из блока 9 управления канала К первай пэуппа k элемен9тов И канала К переходит в высокоимпедансное состояние, которое обеспечивает запись нулевбго слова информации в следующем дакте в первый приемный регистр 2 канала (К-1) (при отсутствии режима Запись). В следующем такте по переднему фронту так тового импульса и сигналу из блока управления 9 канала К первый триггер регистра состояния 12 канала К пере.ходит в состояние Занято По сигналу Принять 1 модуль К вычислительной системы переписывает на свои регистры информацию из первого буферного регистра k канала К и выдает сигнал Принято 1 на вход kS канала К. По заднему фронту тактового импульса и сигнала Принято 1 первы триггер регистра состояния 12 канала К переходит в состояние Свободно По сигналу Равно 2 и состоянию Свободно второго триггера регистра состояния 12 канала К блок управления 9 канала К вырабатывает сигналы, поступающие в регистр состояния 12 канала К, вторую группу 5 элементов И канала К, буферный регистр 15 канала К, и сигнал Принять 2, поступающий на выход М8 канала К. По сигналу из блока управления 9 канала К во второй буферный рег|1стр 15 канала К записывается информация (адрес отправителя, данные) из второго приемного регистра 7 канала,К, По высокому уровню напряжения сигнала из блока 9 управления канала К вторая группа 5 элементов И канала, К переходит в высокоимпедансно состояние, которое обеспечивает запись нулевого слова информации в следующем такте во второй приемный регистр 7 канала (К+1) (при отсутствии режима Запись). В следующем такте по переднему фронту тактового импульса и сигналу из блока управления 9 канала К второй триггер сое тояния регистра 12 канала К переходи в состояние Занято. По сигналу Принять 2 модуль К вычислительной системы переписывает на свои регистры информацию из второго буферного регистра 15 канала К и выдает на вхо 15 канала К сигнал Принято 2. По заднему фронту тактового импульса и сигналу Принято 2 второй триггер регистра состояния 12 канала К переходит в состояние Свободно. Описанные выше действия по сигналам Равно 1 и Равно 2 могут произ12водиться одновременно. В отсутствии i сигналов Равно 1 и Равно 2 либо по состояниям Занято первого и второго тоиггеров регистра состояние 12 канала К режим Чтение не выполняется и на управляющих входах первой k и второй 5 групп элементов И канала К присутствуют низкие уровни напряжения сигналов, поступающие из блока управления 9 канала К. На информацинных выходах первой t и второй 5 групп элементов И канала К присутствует информация, находящаяся на информационных выходах соответственно первого и второго передающих регистров 3 и 6 канала К. В следующем такте по переднему фронту тактового импульса информация с информационных выходов первой t и второй 5 групп элементов И канала К записывается соответственно в первый приемный регистр 2 канала (К-1) и во второй приемный регистр 7 канала (К+1). Режим Запись предназначен для выдачи информации из К-,го модуля вычислительной системы в первую или вторую магистрали в зависимости от адреса получателя, В этом режиме используются все сигналы, поступающие из схемы сравнения 8 канала К. Когда модулю К вычислительной системы необходимо передать информацию, он устанавливает ее (адрес получателя, данные) на входе канала К, по входу 6 канала К посылает в блок управления 9 канала К сигнал Запрос на передачу. По состоянию Свободно третьего триггера регистра состояния 12 канала К и сигналу Запрос на передачу блок управления 9 канала К вырабатывает сигналы, поступающие в третий буферный регистр 16 канала К, регистр состояния 12 канала К, и сигнал Запрос удовлетворен, поступающий нв выход Э канала К. По сигналу из блока управления 9 канала К в третий буферный регистр 16 канала К записывается информация (адрес, получателя, данные) из модуля К вычислительной системы, адрес отправителя из регистра 17 канала К и а разряд поля занятости слова записывается единица. В ответ на сигнал Запрос удовлетворен модуль К вычислительной системы снимает сигнал Запрос на передачу и информацию со входа k канала К, По сигналу из блока управления 9 канала К третий триггер регистра состояния канала 12 К устанавливается в состояние Занято. По состоянию Занято третьего триггера регистра состояния 12 канала К происходит выбор первой или второй магистрали для передачи слова информации из модуля К вычислительной системы. В качестве критерия выбора номера магистрали используется время достижения слова информации адресного модуля Н ( , М; Нз К). Для этого в блоке 13 канала К производят следующие действия. По состоянию Занято третьего триггера регистра состояния 12 канала К (фиг, 2) адрес отправителя (со знаковым разрядом) в обратном коде из регистра 17 канала К и адрес полу чателя в прямом коде (со знаковым разрядом из третьего буферного регистра 16 канала К поступают на вто рой сумматор 63, в котором происходит их суммирование. Если знаковый разряд результата суммирования раве О, то на втором управляющем выходе сумматора 63 присутствует сигнал, п которому на информационный вход группы 72 элементов ИЛИ через шестую группу 62 элементов И подается константа (со знаковым разрядом) в обратном коде из регистра 18 канала К. Если знаковый разряд результата суммирования равен 1, то на первом управляющем выходе сумматора 63 при сутствует сигнал, по которому на ин формационный выход группы 72 элементов ИЛИ через пятую группу 61 элементов И подается константа (со знаковым разрядом) в прямом коде из регистра 18 канала К, По задержанно му сигналу на второй элемент задерж ки 66 на первый и второй информацио ные входы сумматора 64 через группы 59, 60 элементов И соответственно поступают результат суммирования (со знаковым разрядом) с информационного выхода сумматора 63 и константа (со знаковым разрядом) в прямом, либо обратном коде, с информационного выхода группы 72 элементов ИЛИ, Если знаковый разряд результата суммирования равен О, то на втором управляющем выходе сум матора 6 присутствует сигнал, и по приходу задержанного сигнала с элемента задержки б7 в блок-, управле иия 9 канала К поступает сигнал За пись 2, означающий, что слово информации из третьего буферного регистра 16 канала К необходимо передать во вторую магистраль. Если знаковый разряд результата суммирования равен 1, то на первом управляю- щем выходе сумматора 6 присутствует сигнал, и по приходу задержанного сигнал с элемента задержки б7 в блок управления 9 канала К поступает сигнал Запись 1, означающий,, что слово информации из третьего буферного регистра 16 канала К необходимо передать в первую магистраль, По сигналу Запись 1 из блока 13 канала и сигналу Свободно 1 из схемы сравнения 8 канала К блок 9 канала К вырабатывает управляющие сигналы, поступающие в первую и четвертую 11 группы элементов И канала К, По высокому уровню напряжения управляющего сигнала первая группа Ц элементов И переходит в высокоимпеданское состояние, а по низкому уровню напряжения управляющего сигнала на информационный выход четвертой группы 11 элементов И канала К поступает информация из третьего буферного регистра 16 канала К, В следующем такте информация записывается в первый приемный регистр 2 канала (К-1),и третий триггер регистра состояния 12 канала К переходит в состояние Свободно, Если происходит режим Чтение из первой магистрали, то по сигналу Запись 1 блок управления 9 канала К вырабатывает управляющие сигналы, поступающие в первую k и четвертую 11 группы элементов И канала К, и происхрдят действия по записи в первую магистраль, описанные выше. По сигналу Запись 2 из блока 13 канала К и по сигналу Свободно 2 из схемы сравнения 8 канала К блок управления 9 канала К вырабатывает управляющие сигналы, поступающие во вторую 5 и третью 10 группы элементов И канала К, По высокому уровню напряжения управляющего сигнала вторая группа 5 элементов И канала К переходит в высокоимпедансное состояние, а по низкому уровню напряжения управляющего сигнала на информационный выход третьей- группы 10 элементов И канала К поступает информация из третьего буферного регистра 10 канала К, В следующем такте эта информация записывается во второй приемный регистр 7 канала (К+1) и третий, триггер регистра состояния 12 канала К переходит в состояние Свободно. Если происходит режим Чтение из второй магистрали, то по сигналу Запись 2 блок управления 9 канала К вырабатывает управлякхдие сигналы, поступающие во вторую 5 и третью 10 группы элементов И канала К и происходят действия по записи во вторую магистраль, описанные выше. Таким образом, предлагаемое изобретение обладает более высоким быстродействием, чем известное поскольку в нем время выполнения перекрестного обмена имеет величину не более половины времени цикла магистрали. В известном устройстве это время (в худшем случае) равняется времени цикла магистрали без времени одного такта магистрали. Формула изобретения 1. Многоканальное устройство связи для вычислительной системы, содержащее объединенные в кольцо канал и генератор тактовых импульсов, а в каждом канале два приемнй 1х регистра, два передающих регистра, четыре груп пы элементов И, схему сравнения , блок управления, регистр состояния, регистр адреса и три буферных регист ра, причем выход первого приемного регистра канала соединен с информаци онными входами первого передающего регистра канала, первого буферного регистра канала, с первым информационным входом схемы сравнения канала, выход первого передающего регистра канала соединен с информационным вхо дом элементов И первой группы канала выход второго приемного регистра канала соединен с информационными входами второго передающего регистра канала, второго буферного регистра к нала, со вторым информационным входом схемы сравнения канала, выход вт рогр передающего регистра канала сое динен с информационным входом элементов И второй группы канала, выход регистра адреса канала соединен с тр тьим информационным входом схемы сравнения канала и с информационным входом третьего буферного регистра канала, выход третьего буферного регистра канала соединен с информационными входами элементов И третьей и четвертой групп канала, с первого по пятый выходы разрешения выдачи блока управления канала соединены с управляющими входами элементов И соответственно первой - четвертой групп канала и третьего буферного регистра канала, вход завершения приема канала, запросный и установочный входы канала соединены соответственно со входом завершения приема блока управления канала, с запросным входом блока управления канала и с первым установочным входом регистра состояния канала, первый разрешения приема блока управления канала соединен с управ|пяющим входом первого буферного регистра канала и с первым управляющим выходом канала, второй выход разрешения приема блока управления канала соединен с управляющим входом второго буферного регистра канала и со вторым управляющим выходом канала, выход удовлетворения запроса блока управления канала является третьим управляющим выходом канала, выход схемы сравнения канала соединен с запускающим входом блока управления канала, признаковый вход и гасящий выход блока управления канала соединены соответственно с первым выходом и вторым установочным входом регистра состояния канала, синхронизирующие входы приемных, передающих регистров и регистров состояния каналов соединены с выходом генератора тактовых импульсов, выход элементов И первой и четвертой групп канала соединен со входом первого приемного регистра последующего канала, вход второго приемного регистра канала соединенс выходами элементов И второй и третьей групп предыдущего канала, выходы первого и второго буферных регистров канала и вход третьего буферного регистра канала являются соответственно первым, вторым информационными выходами канала и информационным входом канала, о т личающееся тем, что, с повышения быстродействия, каждый канал содержит блок формирования направления записи и регистр констан- ты, причем первый - четвертый информационные и управляющий входы и выход блока формирования направления записи канала соединены соответственно с прямым и инверсным выходами регистра константы канала, с выходами регистра адреса канала и 7Э третьего буферного регистра канала, со вторым выходом регистра состояния канала и со входом переключения магистралей блока управления канала. 2. Устройство по п. 1, о т л и чающееся тем, что блок формирования направления записи содержит два сумматора, шесть групп элементов И, группу элементов ИЛИ, четы ре элемента И, три элемента задержки причем управляющий вход блока соединен с управляющими входами элементов И первой и второй групп и со входом первого элемента задержки, выход которого coeji HeH с первыми входами первого и второго элементов И и со входом второго элемента задержки, выход которого соединен с уп равляющими входами элементов И третьей и четвертой групп и со входомтретьего элемента задержки, выход которого соединен с первыми Ъхода «4 третьего и четвертого элементов И, выходы которых соединены с выходом блока, первый и второй информационные входы блока соединены с информационными входами элементов И со ответственно пятой и шестой групп, выходы которых через группу элементов ИЛИ соединены с информационным входом элементов И четвертой группы, выход которой и выход элементов И третьей групп соединены СОСУТветственно с первым и вторым входа м первого сумматора, первый и второй выходы которого соединены со вторыми входами соответственно третьего и че вертого элементов И, третий и четвертый информационные входы блока со динены с информационными входами элементов И соответственно первой и второй групп, выходы которых соединены соответственно с первым и вторым входами второго сумматора, информационный и первый, второй управляющие выходы которого соединены соответственно с информационным входом элементов И третьей группы и с вторыми входами первого и второго элементов И, выходы первого и второго . элементов И соединены с управляющими входами элементов И соответственно пятой и шестой групп, 3. Устройство по п. 1, отличающееся тем, что блок управления канала содержит пять О-триггеров, три элемента И и элемент задержки, причем запускающий вход блока соединен с первыми входами первого, второго и третьего элементов И, признаковый вход блока соединен со вторыми входами первого и второго элементов И, запросный вход блока соединен со вторым входом третьего элемента И, выход которого является выходом удовлетворения запроса блока, и с D-входом первого Ь-триггера, выход которого является пятым выходом разрешения выдачи блока, вход завершения приема блока, выходы первого и второго элементов И блока являются гасящим выходом блока, выход первого элемента соединен сD-входом второго D-триггера, выход которого является вторым выходом разрешения выдачи блока, и вторым выходом разрешения приема блока, выход второго элемента И соединен с D-входом третьего D-триггера, выход которого является первым выходом разрешения шдачи блока, и первым выходом разрешения приема блока, вход переключения магистрали блока соединен с D-входом четвертого D-триггера и через элемент НЕ с D-входом пятого D-триггера, выходы пятого и четвертого D-триггеров являются соответственно третьим и четвертым выходами разрешения выдачи блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № , кл. G Об F З/О, 1980. 2,Авторское свидетельство СССР tr 2907230/18-2i, кл. G 06 F З/О 1980 (прототип).

25

26

L A

Авторы

Даты

1982-07-15—Публикация

1980-12-29—Подача