I

Изобретение относится к устройствам для индикации двоичной информации, в частности информации типа «есть-нет, «данет, «свободно-занято, «включено выключено и т. п.

Известно устройство для индикации двоичной информации, содержащее пульт управления, световое табло и блок коммутации 1.

Основным недостатком этого устройства является то, что оно не обеспечивает возможности контроля занесения информации в табло и контроля состояния табло, т. е. возможность вызова хранящейся в памяти табло информации на пульт управления.

Наиболее близким к предлагаемому является устройство для индикации двоичной информации, содержащее информационное табдо с ячейками двоичной информации, пульт управления с формирователями команд «есть и «нет, адресный блок и блок контроля состояния табло 2.

Недостатком этого устройства является то, что с увеличением числа индикаторов в строке возрастает число соединительных проводов между адресным блоком и ячейками двоичной информации и существенно увеличивается время на выполнение операций занесения информации на табло, так как в результате одной операции занесения информации на табло вводится только 1 бит информации. Кроме того, при контроле состояния табло на пульт вызывается информация о состоянии только одной ячейки. Цель изобретения - упрощение устройства и расщирения его функциональных возможностей путем обеспечения возмож-0 ности контроля состояния табло.

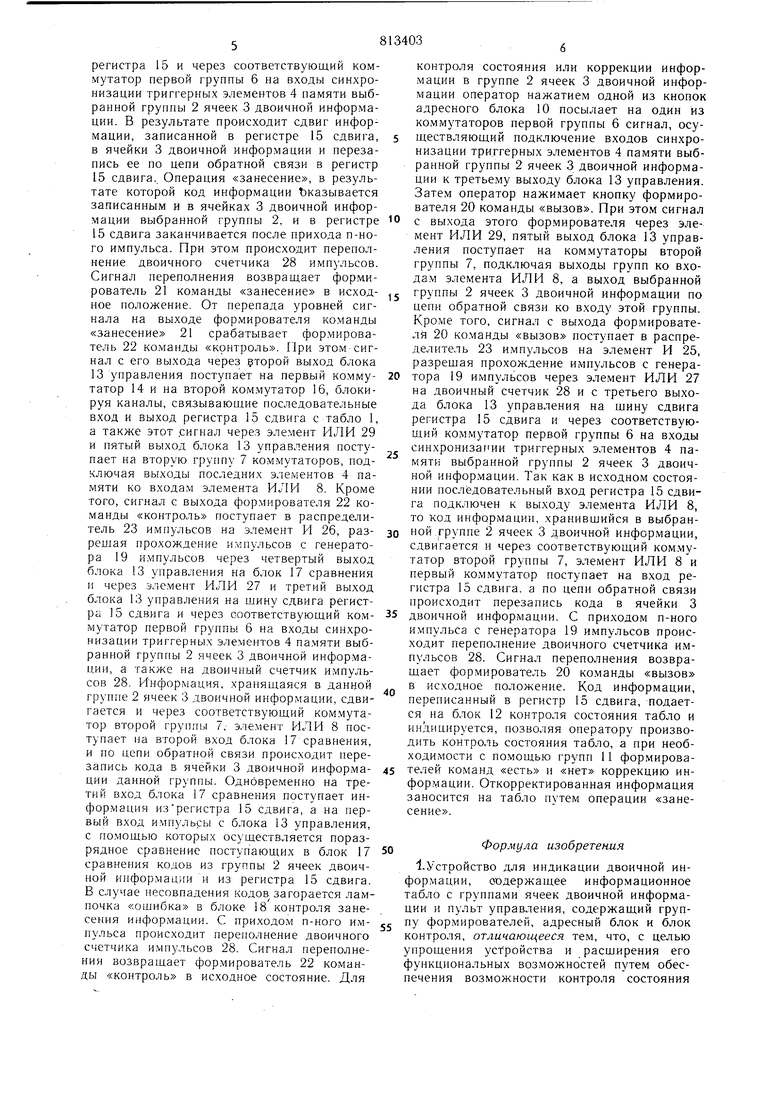

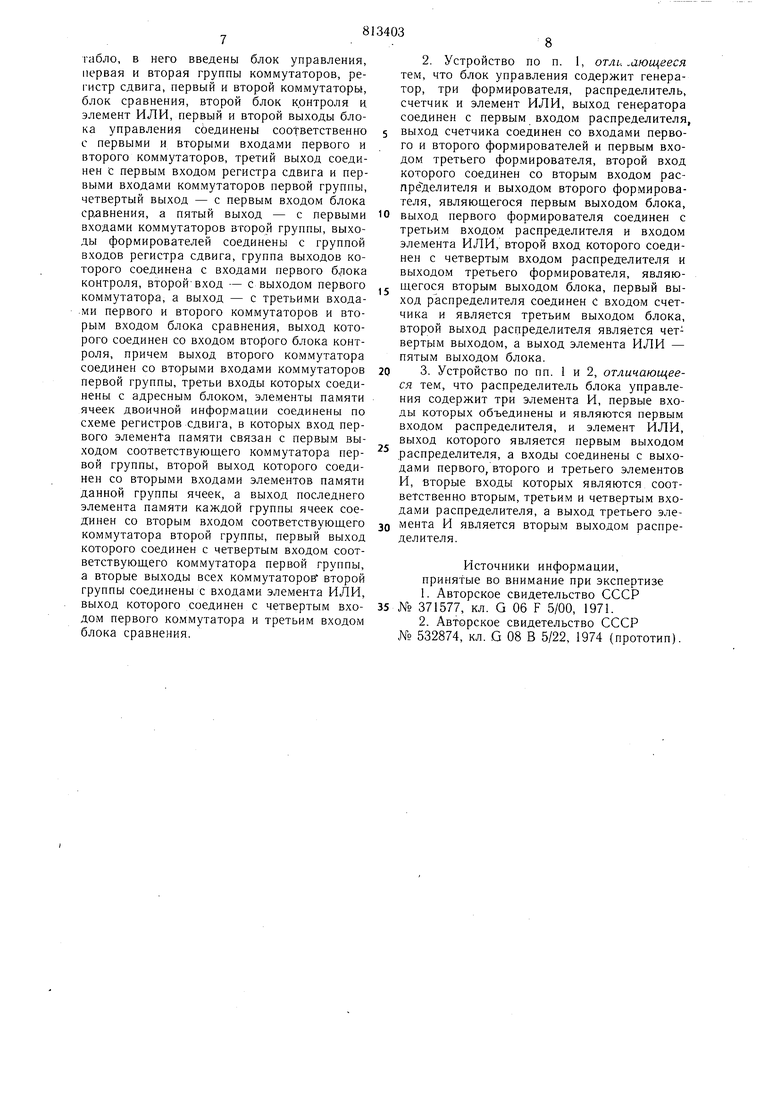

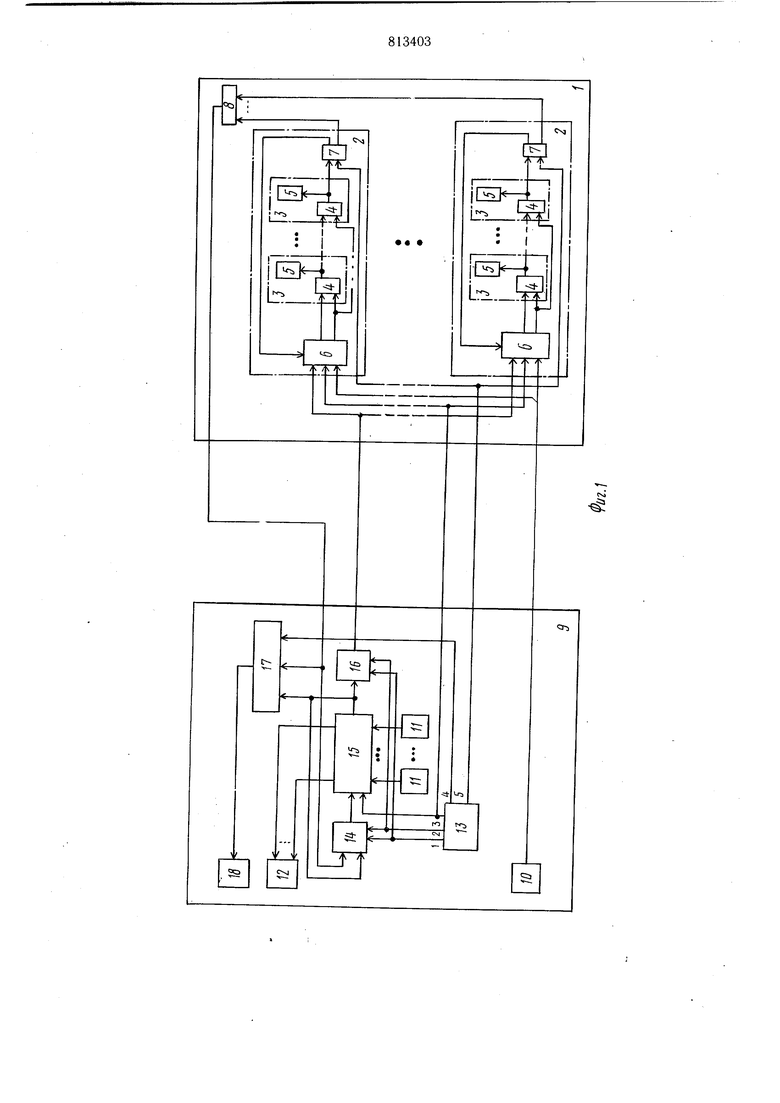

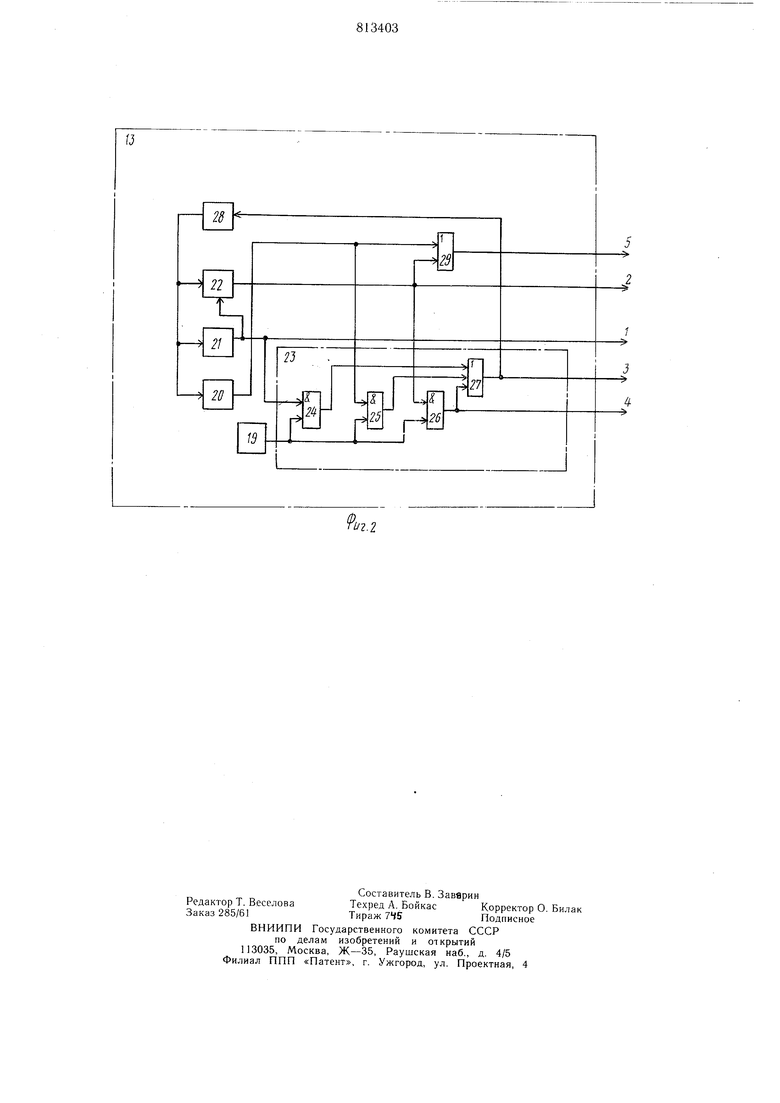

Поставленная цель достигается тем, что устройство для индикации двоичной информации содержит блок управления, первую и вторую группы коммутаторов, регистр сдвига, первый и второй коммутаторы, блок сравнения, второй блок контроля и элемент ИЛИ, первый и второй выходы блока управления соединены соответственно с первыми и вторыми входами первого и второго коммутаторов, третий выход соединен с первым вхоj дом регистра сдвига и первыми входами коммутаторов первой группы, четвертый выход - с первым входом блока сравнения, а пятый выход - с первыми входами коммутаторов второй группы, выходы формирователеи соединены с группой входов регистра сдвига, группа выходов которого соединена с входами первого блока контроля, второй вход - с выходом первого коммутатора, а выход - с третьими входами первого и второго коммутаторов и вторым входом блока сравнения, выход которого соединен с входом второго блока контроля, причем выход второго коммутатора соединен со вторыми входами коммутаторов первой групны, третьи входы которых соединены с адресным блоком, элементы памяти ячеек двоичной информации соединены по схеме регистров сдвига, в которых вход первого элемента памяти связан с первым выходом соответствуюш,его коммутатора первой группы, второй выход которого соединен со вторыми входами элементов памяти данной группы ячеек, а выход последнего элемента памяти каждой группы ячеек соединен со вторым входом соответствующего коммутатора второй группы, первый выход которого соединен с четвертым входом соответствуюидего коммутатора первой группы, а вторые выходы всех коммутаторов второй группы соединены со входами элемента ИЛИ, выход которого соединен с четвертым входом первого коммутатора и третьим входом блока сравнения. Причем блок управления устройства содержит генератор, три формирователя, распрелТ,елитель, счетчик и элемент ИЛИ, генератора соединен с первым входом распределителя, выход счетчика соединен со входами первого и второго формирователей и первым входом третьего формирователя, второй вход которого соединен со вторым входом распределителя и выходом второго формирователя, являющегося первым выходом блока, выход первого формирователя соединен с третьим входом распределителя и входом элемента ИЛИ, второй вход которого соединен с четвертым входом распределителя и выходом третьего формирователя, являюп1,егося вторым выходом блока, первый выход распределителя соединен с входом счетчика и является третьим выходом блока, второй выход распределителя является четвертым выходом, а выход элемента ИЛИ - пятым выходом блока. Кроме того распределитель блока управления устройства содержит три элемента И, первые входы которых объединены и являются первым входом распределителя, и элемент ИЛИ, выход которого является первым выходом распределителя, а входы соединены с выходами первого, второго и третье го элементов И, вторые входы которых являются соответственно вторым, третьим и четвертым входами распределителя, а выход третьего элемента И является вторым выхо-до.м распределителя. На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока управления. Устройство содержит информационное табло 1, состоящее из скомпонованных в группы 2 по п ячеек 3 двоичной информации, содержащих триггерные эле.менты 4 памяти, соединенные по схеме регистра сдвига, и элемент 5 отображения, первую группу 6 коммутаторов и вторую группу 7 коммутаторов, элемент ИЛИ 8 и пульт 9 управления, состоящий из адресного блока 10, содержащего кнопки, количество которых соответствует количеству групп 2 ячеек 3 двоичной информации, группу И из п формирователей команд «есть и «нет. Выходы формирователей подключены к установочным входам соответствующих триггеров п-разрядного регистра 15 сдвига, последовательный ввод информации в этот регистр осуществляется через первый коммутатор 14, последовательный вывод через второй коммутатор 16. Параллельные выходы регистра 15 сдвига соединены с соответствующими сигнальными лампочками блока 12 контроля состояния табло. Кроме того, в состав пульта 9 управления входят блок 17 сравнения, блок 18 контроля занесения информации, представляющий собой сигнальную лампочку, и блок 13 управления, который содержит генератор 19 синхроимпульсов, формирователи 20 команд «вызов,, «занесение 21 и «контроль 22, распределитель 23, состоящий из элементов И 24, 25, 26 и элемента ИЛИ 27, двоичный счетчик 28 и элемент ИЛИ 29. Устройство работает следующим образо.м. При занесении информации на табло 1 оператор нажатием кнопки соответствующих формирователей команд «есть и «нет в группе 11 записывает в регистре 15 сдвига п-разрядный двоичный код. Правильность записи контролируется по сигнальным лампам блока 12 контроля состояния табло. Затем нажатие.м одной из кнопок адресного блока 10 на один из коммутаторов nejjвой группы 6 посылается сигнал, осуществляющий коммутацию входных цепей и подготавливающий соответствующую группу 2 ячеек к приему инфор.мации с пульта. Занесение инфор.мации с пульта начинается после нажатия кнопки формирователя 21 команды «занесение. При этом с первого блока 13 управления на первый коммутатор 14 и второй ко.ммутатор 16 поступает сигнал, осуществляющий коммутацию, в результате которой к выходу регистра 15 сдвига подключается вход выбранной группы 2 ячеек двоичной информации и по цепи обратной связи последовательный вход данного регистра. Одновременно сигнал с формирователя 21 команды «занесение поступает в распределитель 23 импульсов на элемент И 24, разрешая прохождение импульсов с генератора 19 импульсов через элемент ИЛИ 27 на двоичный счетчик 28, с третьего выхода блока 13 управления ца тину сдвига регистра 15 и через соответствующий коммутатор первой группы 6 на входы синхронизации триггерных элементов 4 памяти выбранной группы 2 ячеек 3 двоичной информации. В результате происходит сдвиг информации, записанной в регистре 15 сдвига, в ячейки 3 двоичной информации и перезапись ее по цепи обратной связи в регистр 15 сдвига. Операция «занесение, в результате которой код информации Ъказывается записанным и в ячейках 3 двоичной информации выбранной группы 2, и в регистре 15 сдвига заканчивается после прихода п-ного импульса. При этом происходит переполнение двоичного счетчика 28 импульсов. Сигнал переполнения возвращает формирователь 21 ко.манды «занесение в исход/ .. .. .jj ное положение. От перепада уровней сигнала на выходе формирователя ко.манды «занесение 21 срабатывает фор.мирователь 22 ко.манды «контроль. При этом сигнал с его выхода через торой выход блока 13 управления поступает на первый коммутатор 14 и на второй коммутатор 16, блокируя каналы, связываюпдие последовательные вход и выход регистра 15 сдвига с табло 1, а также этот .сигнал через элемент ИЛИ 29 и пятый выход блока 13 управ.тения поступает на вторую группу 7 ком.мутаторов, подключая выходы последних элементов 4 памяти ко входам элемента И/1И 8. Кроме того, сигнал с выхода формирователя 22 команды «контроль поступает в распределитель 23 импульсов на элемент И 26, разреи1ая прохождение импульсов с генератора 19 и.мпульсов через четвертый выход блока 13 управления на блок 17 сравнения и через э.1е.мент ИЛИ 27 и третий выход блока 13 управления на шину сдвига регистра 15 сдвига и через соответствующий ко.ммутатор первой группы 6 на входы синхронизации триггерных элементов 4 па.мяти выбранной группы 2 ячеек 3 двоичной инфор.мации, а также на двоичный счетчик и.мпульсов 28. Информация, храняо аяся в данной группе 2 ячеек 3 двоичной инфор.мации, сдвигается и через соответствующий ком.мутатор второй группы 7, эле.мент ИЛИ 8 поступает на второй вход блока 17 сравнения, и по цепи обратной связи происходит перезапись кода в ячейки 3 двоичной информации данной группы. Одновременно на третий вход блока 17 сравнения поступает инфор.мация изрегистра 15 сдвига, а на первый вход импульсы с блока 13 управления, с по.мощью которых осуществляется поразрядное сравнение поступающих в блок 17 сравнения кодов из группы 2 ячеек двоичной информации и из регистра 15 сдвига. В случае песовпадения кодов загорается лампочка «ошибка в блоке 18контроля занесения инфор.мации. С приходо.м п-ного импульса происходит переполнение двоичного счетчика импульсов 28. Сигнал переполнения возвращает фор.мирователь 22 команды «контроль в исходное состояние. Для контроля состояния или коррекции информации в группе 2 ячеек 3 двоичной информации оператор нажатием одной из кнопок адресного блока 10 посылает на один из коммутаторов первой группы 6 сигнал, осуществляющий подключение входов синхронизации триггерных элементов 4 памяти выбранной группы 2 ячеек 3 двоичной информации к третьему выходу блока 13 управления. Затем оператор нажимает кнопку формирователя 20 команды «вызов. При этом сигнал с выхода этого фор.мирователя через элемент ИЛИ 29, пятый выход блока 13 управления поступает на коммутаторы второй группы 7, подключая выходы групп ко входам элемента ИЛИ 8, а выход выбранной группы 2 ячеек 3 двоичной информации по цепи обратной связи ко входу этой группы. . . . V . Кроме того, сигнал с выхода фор.мирователя 20 команды «вызов поступает в распределитель 23 и.мпульсов на элемент И 25, разрешая прохождение импульсов с генератора 19 импульсов через элемент ИЛИ 27 на двоичный счетчик 28 и с третьего выхода блока 13 управления на щину сдвига регистра 15 сдвига и через соответствующий коммутатор первой группы 6 на входы синхронизации триггерных элементов 4 па.мяти выбранной группы 2 ячеек 3 двоичной информации. Так как в исходном состоянии последовательный вход регистра 15 сдвига подключен к выходу элемента ИЛИ 8, то код информации, хранившийся в выбранной,группе 2 ячеек 3 двоичной информации, сдвигается п через соответствующий ком.мутатор второй группы 7, элемент ИЛИ 8 и первый коммутатор поступает на вход регистра 15 сдвига, а по цепи обратной связи происходит перезапись кода в ячейки 3 двоичной информации. С приходом п-ного импульса с генератора 19 импульсов происходит переполнение двоичного счетчика импульсов 28. Сигнал переполнения возвращает формирователь 20 ко.манды «вызов в исходное положение. Код информации, переписанный в регистр 15 сдвига, подается на блок 12 контроля состояния табло и индицируется, позволяя оператору производить контроль состояния табло, а при необходи.мости с помощью групп 11 формирователей команд «есть и «нет коррекцию инфор.мации. Откорректированная информация заносится на табло путем операции «занесение. Формула изобретения .Устройство для индикации двоичной инфор.мации, содержащее информационное табло с группами ячеек двоичной информации и пульт управления, содержащий группу формирователей, адресный блок и блок контроля, отличающееся тем, что, с целью прощения устройства и расширения его yнкциoнav ьныx возможностей путем обеспечения возможности контроля состояния табло, в него введены блок управления, первая и вторая группы коммутаторов, регистр сдвига, первый и второй коммутаторы, блок сравнения, второй блок контроля и. элемент ИЛИ, первый и второй выходы блока управления сбединены соответственно с первыми и вторыми входами первого и второго коммутаторов, третий выход соединен с первым входом регистра сдвига и первыми входами коммутаторов первой группы, четвертый выход - с первым входом блока сравнения, а пятый выход - с первыми входами коммутаторов второй группы, выходы формирователей соединены с группой входов регистра сдвига, группа выходов которого соединена с входами первого блока контроля, второйвход - с выходом первого коммутатора, а выход - с третьими входа-ми первого и второго коммутаторов и вторым входом блока сравнения, выход которого соединен со входом второго блока контроля, причем выход второго коммутатора соединен со вторыми входами коммутаторов первой группы, третьи входы которых соединены с адресным блоком, элементы памяти ячеек двоичной информации соединены по схеме регистров сдвига, в которых вход первого элeмeнta памяти связан с первым выходом соответствуюш.его коммутатора первой группы, второй выход которого соединен со вторыми входами элементов памяти данной группы ячеек, а выход последнего элемента памяти каждой группы ячеек соединен со вторым входом соответствуюш.его коммутатора второй группы, первый выход которого соединен с четвертым входом соответствующего коммутатора первой группы, а вторые выходы всех коммутаторов второй группы соединены с входами элемента ИЛИ, выход которого соединен с четвертым входом первого коммутатора и третьим входом блока сравнения. 2.Устройство по п. 1, отли .ающееся тем, что блок управления содержит генератор, три формирователя, распределитель, счетчик и элемент ИЛИ, выход генератора соединен с первым входом распределителя, выход счетчика соединен со входами первого и второго формирователей и первым входом третьего формирователя, второй вход которого соединен со вторым входом распределителя и выходом второго формирователя, являющегося первым выходом блока, выход первого формирователя соединен с третьим входом распределителя и входом элемента ИЛИ, второй вход которого соединен с четвертым входом распределителя и выходом третьего формирователя, являющегося вторым выходом блока, первый выход распределителя соединен с входом счетчика и является третьим выходом блока, второй выход распределителя является четвертым выходом, а выход элемента ИЛИ - пятым выходом блока. 3.Устройство по пп. 1 и 2, отличающееся тем, что распределитель блока управления содержит три элемента И, первые входы которых объединены и являются первым входом распределителя, и элемент ИЛИ, выход которого является первым выходом распределителя, а входы соединены с выходами первого, второго и третьего элементов И, вторые входы которых являются соответственно вторым, третьим и четвертым входами распределителя, а выход третьего элемента И является вторым выходом распределителя, Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 371577, кл. G 06 F 5/00, 1971. 2.Авторское свидетельство СССР № 532874, кл. G 08 В 5/22, 1974 (прототип).

1 I , Ч1

i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1982 |

|

SU1095225A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для ранжирования чисел | 2022 |

|

RU2792182C1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Автоматизированный класс для контроля знаний обучаемых | 1981 |

|

SU1012318A1 |

| Устройство для приема и обработки команд телеуправления | 1989 |

|

SU1667137A1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| Устройство для селекции изображений объектов | 1983 |

|

SU1188765A1 |

ITi.

L.-m

0 J

Авторы

Даты

1981-03-15—Публикация

1978-06-01—Подача