(54) ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА

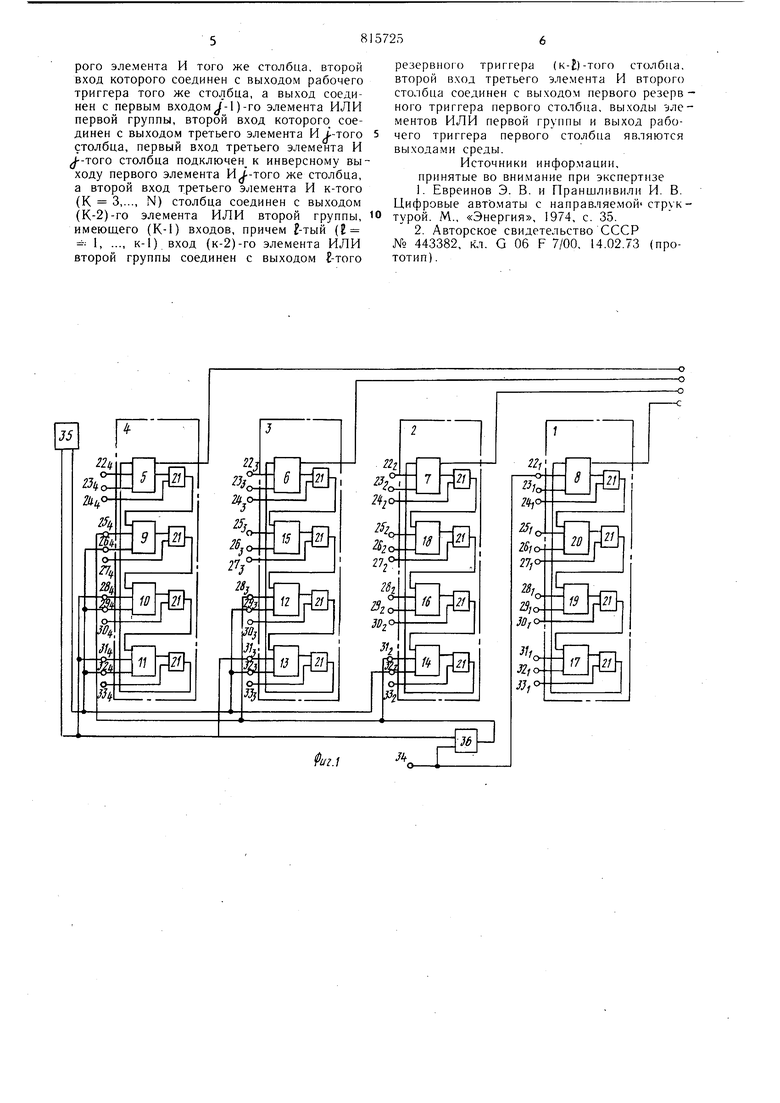

4-х разрядной среды; на фиг. 2 - то, же, со связями, обеспечивающими выдачу информации со среды.

Однородная вычислительная среда содержит столб цы -4, рабочие триггеры основных разрядов 5-8, тестирующие триггеры 9-14, резервные триггеры 15-20, элементы 21 И, внешние выводы ,, 23, -23, ,, 25, -25, 26.,-26, 27 27., 28,-28,, 29,-29v, 30,-30, 31i-31i,, 32,-32;у, , вход 34. генератор 35 тестовых сигналов, элемент 36 ИЛИ, доиолнительные элементы 37 ИЛИ, элементы 3S-40 И, элементы 41 ИЛИ, выходные шины однородной вычислительной среды 42-45.

Принцип работы однородной вычислительной среды состоит в следующем.

Входная информация подается независимо в столбцы 1-4. Для хранения и выдачи информации используются триггеры 58, а также триггеры 15-20. Триггеры 9-14 используются для тестового контроля. Исправность 4-го (старшего) разряда контролируется триггерами 9-11, исправность 3-го разряда - триггерами 12 и 13, исправность 2-го разряда - триггером 14, исправность 1-го разряда не контролируется.

Наличие корреляционных связей между разрядами в интегрально.м исполнении позволяет применить косвенный контроль.

Количество тестирующих триггеров каждого разряда кратно весу разряда (фиг. 1). Для резервирования основных разрядов используются резервные разряды.

Триггер основного 4-го разряда резервируется триггерами 15-17, триггер 3-го разряда - триггерами 18 и 19, триггер 2-го разряда - триггером 20, триггер 1-го разряда не резервируется. Количество резервных триггеров также кратно весу разряда (фиг. 1).

Таким образом, предлагаемый резервированный регистр сохраняет работоспособность при отказах типа «ложный ноль, т. е. тогда, когда требуемые логические единицы не могут быть выданы и вместо них выдаются нули.

Однородная вычислительная среда работает следующим образом.

В режиме записи информация поступает на вход 34 независимо в каждый столбец 1-4 на внешние выводы 25/,, , 21 и 22. Для разрыва цепи сдвига от старщего к младшему разряду на выводы 24i,, 27j, 30, и 33, подается внешний потенциал запрета, а на выводы 24.,-24, ,, 27, 30,, 3Gj, 30 и подается внешний потенциал, разрешающий сдвиг информации.

В режиме контроля тест-программа проверки исправности модулей с первого выхода генератора 35 подается на выходные выводы 26, 29,, 29; и 32,-32 и устанавливают тестирующие триггеры контрольных разрядов в «ноль, со второго вывода генератора 35 импульс подается на входные

выводы 28 31ч, 31 - непосредственно и через элемент 36 на выводы 254., 28д и 314. Второй импульс от генератора 35 устанавливает тестирующие триггеры в «единицу.

В случае неисправности какого-либо модуля исключается считывание информации с рабочего триггера данного столбца.

При контроле однородной вычислительной среды сигналы тестирующих триггеров подаются на элементы 39 И (фиг. 2). В случае исправности с прямого выхода элемен та 39 И на один из входов элемента 40 И подается разрещающий потенциал, на второй вход элемента 40 И поступает информа.ция, подлежащая считыванию с рабочего григгера, которая с выхода элемента 40 И через элемент 41 ИЛИ подается на соответствующую выходную щину. При неисправности тестирующих триггеров с прямого выхода элемента 39 И выдается запрещащий потенциал, а с инверсного - разрещающий. Разрещающий потенциал поступает на один из входов элемента 38 И, а на другой вход которого подается информация с выхода соответствующих элементов 37 ИЛИ, и выходная информация с выхода элементов 38 И через соответствующий элемент 41 ИЛИ подается на щину выходной информации. Таким образом, при неисправности какого-либо столбца используется информация резервных разрядов.

Технико-экономический эффект от применения изобретения состоит в повыщении надежности однородной вычислительной ере ды за счет контроля и резервирования кратного весу разряда. При последовательных отказах любых интегральных схем с однородной вычислительной среды продолжает поступать информация без потери точности. Лишь неисправность интегральной схемы, с которой снимается первый основной разряд, приводит к потере точности на величину младщего разряда. Кроме того, имеется возможность контроля однородной вычислительной среды без нарущения цикла работы.

Формула изобретения

Однородная вычислительная среда, содержащая матрицу триггеров из N .строк и N столбцов, причем каждый i-тый (i 1,..., N) столбец матрицы содержит рабочий триггер, (i-I) тестирующих триггеров, (N-i) резервных триггеров, отличающаяся тем, что, с целью повыщения надежности, в среду введены две группы элементов ИЛИ и в каждый столбец матрицы , кроме первого, введены три элемента И, причем входы первого элемента И каждого -того (- 2, ... N) столбца соединены с выходами тестирующих триггеров того же столбца, прямой выход первого элемента И соединен с первым входом второго элемента И того же столбца, второй вход которого соединен с выходом рабочего триггера того же столбца, а выход соединен с первым входом -)-го элемента ИЛИ первой группы, второй вход которого соединен с выходом третьего элемента И J -того столбца, первый вход третьего элемента И -того столбца подключен к инверсному выходу первого элемента И -того же столбца, а второй вход третьего элемента И к-того (К 3,..., N) столбца соединен с выходом (К-2)-го элемента ИЛИ второй группы, имеющего (К-1) входов, причем -тый (Е 1, ..., к-1) вход (к-2)-го элемента ИЛИ второй группы соединен с выходом -того

резервного триггера (к-Е)-того столбца, второй вход третьего элемента И второго столбца соединен с выходом первого резервного триггера первого столбца, выходы элементов ИЛИ первой группы и выход рабочего триггера первого столбца являются выходами среды.

Источники информации, принятые во внимание при экспертизе

1.Евреинов Э. В. и Праншливили И. В. Цифровые автоматы с направляемой структурой. М., «Энергия, 1974, с. 35.

2.Авторское свидетельство СССР

№ 443382, кл. G 06 F 7/00, 14.02.73 (прототип).

«

:S«3

o,К5

| название | год | авторы | номер документа |

|---|---|---|---|

| Однородная вычислительная среда | 1979 |

|

SU826336A1 |

| Резервированный сдвигающий регистр | 1976 |

|

SU693439A1 |

| Однородная вычислительная среда | 1979 |

|

SU885992A1 |

| Двоичный счетчик | 1978 |

|

SU782168A1 |

| Сдвиговое устройство | 1978 |

|

SU765879A1 |

| Однородная вычислительная структура | 1982 |

|

SU1164713A1 |

| Оперативное запоминающее устройство с резервированием строк | 1986 |

|

SU1462426A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Блок обработки матричной вычислительной системы | 1991 |

|

SU1827675A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

г,;

1Щ

ft

35

Авторы

Даты

1981-03-23—Публикация

1978-07-07—Подача