Г54) ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Однородная вычислительная среда | 1979 |

|

SU826336A1 |

| Однородная вычислительная среда | 1978 |

|

SU815725A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Модуль однородной вычислительной структуры | 1987 |

|

SU1495809A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Двоичный счетчик | 1978 |

|

SU782168A1 |

| Матричное устройство для возведения в квадрат | 1989 |

|

SU1619260A1 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| Резервированный сдвигающий регистр | 1976 |

|

SU693439A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ | 1993 |

|

RU2117986C1 |

1

Изобретение относится к вычислительной технике и дискретной автоматике и может быть использовано при построении цифровой аппаратуры повещенной надежности.

Известна однородная вычислительная среда содержащая N модулей, причем i-й модуль (i 1,..,N ) содержит один рабочий триггер. (i-1) контрольных триггеров, (N-i) резервных триггеров, а также группы элементов И и ИЛИ, осуществляющие контроль и коммутацию, выходы которых соединены с выходами среды 1.

Недостатком этой однородной среды является отсутствие проверки контрольных злементов модулей на отказ типа ложная единица, т. е. на тот отказ, при котором соответствующие логические нули не могут быть вьщаиы и вместо них выдаются единицы.

Наиболее близкой к предлагаемой является однородная вьгчислшельная среда, содержащая N многофушсдиональнь1Х модулей и элементы И и ИЛИ, причем каждый и -й многофункциональный модуль (i 1,..., N) содержит рабочий триггер, (i-1) контрольных триггеров, (N-i)

резервньи триггеров, вь1ход рабочего триггера j-ro многофункционального модуля (,...,N-1) соединен с первым входом соответствующего злемента И первой группы, выход которого соединен с первым входом соответствующего злемента ИЛИ первой группы, второй вход которого соединен с выходом соответствз ощего злемента И второй группы, а выход - с соответствующим выходом вычислительной среды, выход рабочего триггера N-ro многофункциональиого модуля соединен с соответствующим выходом вычислительной среды, первый вход

к-го злемеита И первой группы (к 2N-1)

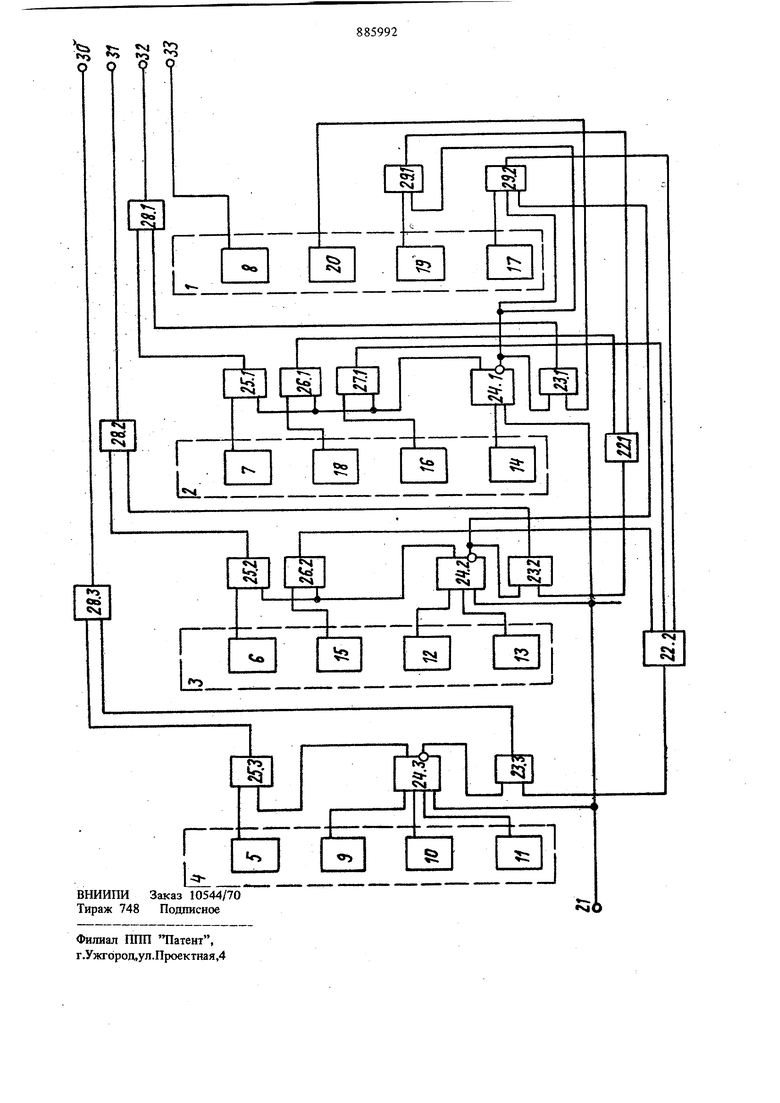

соединен с выходом соответствующего элемент ИЛИ второй группы, первый вход (N-1)-го элемента И второй гругаты соединен с выходом младщего резервного триггера N-ro многофункцишального модуля, содержащая также (N-1) триггеров фиксащш исправности, вход каждого из которых соединен с выходом старшего контрольного триггера соответствующего многофункционального модуля, выходы старших (N-2) резервных триггеров N-ro миогофункционалыюго модуля соединены с первыми входами соответствующих , элементов И третьей группы, остальные входы каждого т-го элемента И третьей группы (т 1,..., IM-2) соединены с инверсными выходами 1-х триггеров фиксации исправности (1 m +1, ..., N-1), инверсный выход каждого триггера фиксации исправноста подключен ко второму входу соответствующего элемента И йторой группы, выход каждого иэ (J-1) резервных триггеров j-ro многофункционального модуля соединен с первым входом (Соответствующего элемента И (|+3)-й группы; вторые входы элементов И первой группы и элементов И каждой (j+3)-и группы соединены с ярямыми выходами соответствующих триггеров фиксации исправности, входы канщого к-го элемента ИЛИ второй группы саединены с выходами (к-И)-х элементов И каждой (+3)-й группы и выходом к-го элемента И третьей грушш Ш. йедостзтком этой однородной среды являетс недостаточная надежность, связанная с фиксацией каждого моцуля. Цель изобретения - повышение надежности однородаой вычислительной среды по отношению к осаовным типам отказов. Пос1звяЁНная достта-ается тем, что в однородную вычислительную Среду, соцержаздую N модулей группы элементов И и ИЛИ, причем каждый (-ймодуш (...., N) содержит одю рабочий триггер, -1)контрольньк т| 1ггеров (N-О резервных триггеров, выходы элементов ИЛИ первой группы и выход рабочего i iHFrepa первого мод)71Я соединены с соотв етств)аошими выходами среды, первый вход элемента ИЛИ йервой грушш соедини с выхопом соответствующего элемента И не|жой фунлв, первый вхсщ первого элемент И первой групш) соединен с выходом первого резервного три1тера netmofo моауля, перкф вход к-го элемента И Шфвой (,...,М-1) соединен евьвсодом 6с-1)-го элецеяга ИЛИ вторМ грзошы второй вход каждого элемё па ШШ первой грушш сое;фшен б выходом соответствующего элемента И . первый вход т-го элемента И группы (т«1,..., N-1) соединен с выходом рабочего триггера (т+1)-го модуля, р-я груша элементов И (,...,Ы),мэдер5Кит (N-p+1) элемв|нтов И, о-й элементе И р-й грушш (q I,..., N-p+I) соединен первым входом с выходом (р-2)-го резервного фштера (q+l)-ro модуля, вход каждого эжмента И (Nfi)-и группы соединен с выходами резервных триггеров первого модуля со второго по (IVf-1)-й соответ ственно, выходы элементов (Ы+1)-й группы соединены со вторыми входами соответствующих элементов ИЛИ в/орой группы, выход q-ro элемента И р-й группы соединён со входом (р + q - 3) -го элемента ИЛИ второй груп пы, введены (N-1) схема сравнения, первая группа входов j-й схемь{ сравнения соединена с выходами контрольных триггеров (j-H)-ro модуля (,-, N-1), а вторая группа входов - с контрольным входом однородной среды, инверсный и прямой выходы j-й схемы сравнения соединены со вторыми входами j-x элементов И первой и второй групп соответственно, второй вход д-го элемента И р-й группы cofc динен с прямым выходом q-й схемы сравнения, инверсный выход j-й схемы сравнения соединен со входами элементов И (N -г 1)-й группы с j-ro по (Н-2)-й. На чертеже приведена структурная блок-схема однородной вычислительной среды. Однородная вычислительная среда содержит модули 1-4, в интегральном исполнении, содержащие рабочие триггеры 5-8, контрольные триггеры 9-14, резервные триггеры 15-20, контрольнь1Й вход 21 среды, элементы ИЛИ 22, элементы И 23, схемы 24 сравнения, элементы И 25, элементы И 26, элементы ИЛИ 27 и 28, элементы И 29, выходы 30-33. Выход триггера 5 и прямой выход схемы сравнения 24J подключены соответственно к первому и второму входам элемента И 25.3, выход триггер 6 и прямой выход схемы 24.3 сравнения подключены соответственно к первому и второму входам элемента И 25.2, выход триггера 7 и прямой выход схемы 24,1 сравнения подключены соответственно к первому и второму входам элемента И 25.1, а выход триггера 8 подключен непосредственно к выходу 33 сред)л. Выходы триггеров 9-11 подключены к первой группе входов схемы 24.3 сравнения, выходы триггеров 12 и 13 подключеиы к первой группе входов схемы 24.2 сравнения, выход триггера 14 подключен к первому входу схеt&i 24.1 сравнения, другие входы схем 24.1-24.3 сравнения подключены к контрольному входу 21 среды. Прямой выход схемы 24.3 сравнения П01цключен ко второму входу элемента И 25.3, прямой выход схемы 24.2 сравнения Подключен ко вторым входам элементов И 25.2 и 26.2, а прямой выход схемы 24.1 сравнения подключен ко вторым входам элементов И 25.1-27.1. Выход элемента И 25.1 подключен ко второму входу элемента ИЛИ 28.1, первый вход которого подключен к выходу элемента И 23.3, выход элемента И 25.2 подключеи ко второму входу элемента ИЛИ 28.2, первый . вход которого подключен к выходу элемента И 23.2, выход элемента И 25.1 подключеи ко второму входу элемента ИЛИ 28.1, первый вход которого подключен к выходу элемента И 23.1. Выход триггера 15 подключен к первому входу элемента И 26.2, выходы триггеров 18 и 16 подключены к первым входам соответственно элементов И 26.1 и 27.1. Инверсный выход 5 схемы 24.3 сравнения подключен к первому входу элемента И 23.3, инверсный выход схемы 24.2 сравнения подключен к первому входу элемента И 23.2, к третьему входу элемента И 29.2, инверсный выход схемы 24.1 сравнения подключен к первому входу элемента И 23.1, ко второму входу элемента И 29.2 и ко второму входу элемента И 29.1. Вторые входы элементов И 23.3, 23.2 подключены к выходам элементов ИЛИ - 22.2, 22.1 соответственно, а второй вход эдемеита И 23.1 подключен к выходу триггера 20; К первому, второму и третьему входам элемента ИЛИ 22.2 второй группы подключены выходы элементов И 6.2 и 27.1 к 29.2, соответственно, к nepieoMy и второму входам элемента ИЛИ 22.1 подключены выходы элементов И 26.1 к 29.1 собтветствецно, при этом первые входы элементов И 29.1, 29.2 подключены к выходам триггеров 19 н 17 соответственно, а 8Ь{ходы элементов ИЛИ 28.3 ч 28.1 подключены к выходам 30-32 соответственно. Принщш работы однородной вычислительной среды состоит в следующем. Входная информация подается неэависимо в модули 1-4. Для хранения и выдачи информации в модулях испольэуются рабочие триггеры 5-8, а также резервные триггеры 15-20. Триггеры 9-14 .используются для косвениого контроля. Исправность модуля 4 контролируется тремя трштеракш 9-11, исправность модуля 3 ксжтршшруется двумя трштер мн 12 и 13, исправность модуля 2 контролируется одним . трштером 14. Исправность модуля 1 не контрошсруется. Наличие 1(орреляшкишой связи между триггерами одного модуля позволяет лриМ(ШИ1Ъ косвенный контроль. Количество кая трояьных триггеров каждого модуля кратно отиосятельному информащкяшому весу рабочего триггера этого модуля. jEbui резервирования рабочих 1| иггеров используются резервные триг гфы. 1Ъбочий триггер модуля 4 резервируется тремя триггерами 15-17, рабочий триггер модуля 3 резерв1фуется двумя триггерами 18 и 19, триггер модуля 2 резервируется ощаол триггером 20, а рабочий триггер модуля 1 не резервируется. Количество резервных тригге ров каждого модуля тшс же кратно относительному информационному весу рабочего триг гера данного модуля. В режиме контроля тест-прогремма проверки нсправности модулей среды подается на контрольные триггеры модулей 2-4. Тест-программа представляет собой последовательность импульсов, с помощью которой контрольные триггеры модулей 2-4 устанавливаются в состоянии О н 1. Таким образом, с помощью тест-программ различной длнны реализуются разлнчные переходы контрольных триггеров из 2 состоштия О в состояние О, из сосгояния О в состояние I, нэ состояния 1 в состояние О, из состояния 1 в состояние 1. Таким образом среда сохраняет работоспособность при отказах ложный ноль, ложная единица и других типах отказов, при которых управляемость логическими состояниями мод лей нарущается. В случае ненсправностн среды исключается считывание информации с рабочего триггера данного модуля. При контроле среды сигналы с контрольных триггеров подаются на входы схем 24 сравнения. Схема 24 сравнения сравнивает информацшо, полученную с контрольных триггеров модуля с информацией, получешюй через контрольный вход 21 среды. В случае несовпадення Ш1формашга модуль расценивается как неис1фавный, а в случае совпадения - модуль считается исправньпи. В случае исправности модуля 4, с прямого выхода схемы 24.1 совпадения на вторые входы соответствуюощх элементов И 25-27 выдается разрег шаюадай потенщал, П1Ж этом на первые входы этих элементов пост)гпает информация в рабочих н резервных триггеров дашюто мо)Ц(уля. В этом случае информация, подлежащая счишванню , с рабочего триггера данного модуля через элементы И 25 н ИЛИ ,28, выдается на соответству ющий вьосод 30-32 среды, а информация с соответствующнх элементов И 26 и 27 поступает на входы соответствующнх элементов ИЛИ 22. При зтом с инверсного выхода схемы 24 сравнения выдается запрещающий потенцнал, который поступает на первый вход элемента И 23, а также на входы соответствующих элементов И 29, в результате чего выдача информации с резервных триггеров в данную выходную шину блокируется. Прн неисправности контрольных трштер(Ж модуля с прямого выхода схемы 24 сравнеш вьздаетсн запрещающий потенциал, а с инверсного - раэрешаюищй. В этом слуол запрершо1ДНЙ потешщал, попадая на вторые входы cooiветствуюыдах элементов И 25-27 блокирует выдачу информации с рабочего и трнггеров модуля. Рирешающнй потенцнал .с явверсного выхода схемы 24 сравнения псшадает на первый вход соответствующего злемепха И 23, на вход которого поступает информация с соответствуницего элемента ИЛИ 22 на входы которого поступает ннформация с резервных трштеров нсправных модулей. Таким образом, в этом случае информация с резервных трштеров через элементы И 23, ИЛИ 28 попадает на соответствующнй выход среды. В случае отказа модулей 4, 3 н 2информация на выходы среды выдается с основ.ного н резервных трнггеров модуля 1. Такнм .образом, при неисправности среды используется информация резервных триггеров. Технический эффект предлагаемого изобретения заключается в повышении надежности сре ды за счет косвенного контроля и резервирования, кратного информационному весу элемен та. При последовательных отказах любых со среды продолжает поступать информация без по тери точности. Лишь неисправность модуля, с которого снимается первый основной разряд для N-разрядной среды, приводит к потери точ ности-f/g 2 100%. Кроме того, шмеется воз можность контроля среды без нарушения цикла работы. Формула изобретения Однородная вьпшслительная среда, содержащая N модулей, группы элементов И н ИЛИ, щ}ичем ка}кдый i-й (- t,...,N) содержит один .рабочий триггер, (i-1) контрольных триггеров, (N-i) резервных триггеров, выходы элементов ИЛИ первой группы и выход рабочего триггера первого модуля соединены с соответствующими выходами среды, первый вход каж дого элемента ИЛИ первой группы соединен с выходом соответствующего элемента И первой группы, первый вход первого элемента И первой группы соединен с выходом первого резервного триггера первого модуля, первый вход к-го элемента И первой rpyraibi (,..., N-1) соединен с выходом (к-1)-го элемента ИЛИ второй группы, второй вход каждого элемента ИЛИ первой группы соединен с выходом соответствующего элемента И второй группы, первый вход т-го элемента И второй группы (т Т,..., N-i) соединен с выходом рабочего триггера (гц-И)-го модуля, р-я группа элементов И (р-3, N) содержит (N-p-H) элементов И, q-й элемент И р-й группы (,..., N-p+I) соединен первым входом с выходом (р-2)-го резервного триггера (q+l)-ro модуля, первый вход каждого элемента И ()-й группы соединен с выходом первого модуля со второго по (N-i)-и, соответственно, выходы элементов ()-й группы соединены со вторыми входами соотвётствую1цйх элементов ИЛИ второй грунпы, выход q-ro элемента И р-ой группы соединен со входом (р+с}-3)-го элемента ИЛИ второй группы, отличающаяся тем, что, с целью повышения надежности среды, в нее введены (N-1) схема сравнения, первая группа входов j-й схемы сравнения соединена с выходами контрольных триггеров (j+I)-ro модуля (,...,N-l), а вторая группа входов - с контрольным входом однородной среды, инверсный и прямой выходы j-й схемь сравнения, соединены со вторыми входами j-x элементов И первой и второй групп соответственно, второй вход q-ro элемента И р-й группы соединен с прямым выходом q-й схемы сравнения, инверсный выход 1-й схемы сравнения соединен со входами элементов И (М+1)-й гр)ашы с j-ro по (Ы-2)-й. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке № 2640972 ,/18-24, кл. G 06-F 7/00, 1978. 2. Авторское свидетельство СССР по заявке N1 2749377/18-24, кл, G Об F 7/00, 06.04.79 (прототип).

LTLJ

Авторы

Даты

1981-11-30—Публикация

1979-05-25—Подача