i4

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1988 |

|

SU1596393A1 |

| Запоминающее устройство с резервированием | 1987 |

|

SU1411824A1 |

| Запоминающее устройство | 1985 |

|

SU1252816A1 |

| Запоминающее устройство с резервированием | 1986 |

|

SU1417042A1 |

| Оперативное запоминающее устройство с коррекцией ошибок и резервированием | 1989 |

|

SU1709397A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU959166A1 |

| Постоянное запоминающее устройство | 1987 |

|

SU1418816A1 |

| Оперативное запоминающее устройство с самоконтролем | 1985 |

|

SU1300569A1 |

| Дешифратор | 1988 |

|

SU1594605A1 |

Изобретение относится к вычислительной технике, в частности к резервированным запоминающим устройствам, изобретения повышение быстродействия устройства. В оперативное запоьшнающее устройство с резервированием строк, содержащее основной накопитель 1, резервный накопитель 2, основной дешифратор 3, резервный де- шифратор 4, адресные формирователи 5, дешифратор 6, введены дополнительный столбец 10 элементов памяти и элементы И-НЕ 1 I. Перед работой программируется дешифратор 6 на выявление отказавших строк, а в элементы памяти дополнительного столбда 10, соответствующие отказавшим строкам, заносятся единицы, формирующие на выходах соответствуюцих элементов И-НЕ 11 сигнапы блокировки выходов основного адресного дешифратора 3. Сигналы с выходов дешифратора 6 через резервный дешифратор 4 подключают строку резервного накопителя 2. 2 ил. (

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано при создании оперативных запоминаю 11лх устройств в интегральном исполнении.

Целью изобретения является повыше ние быстродействия устройства.

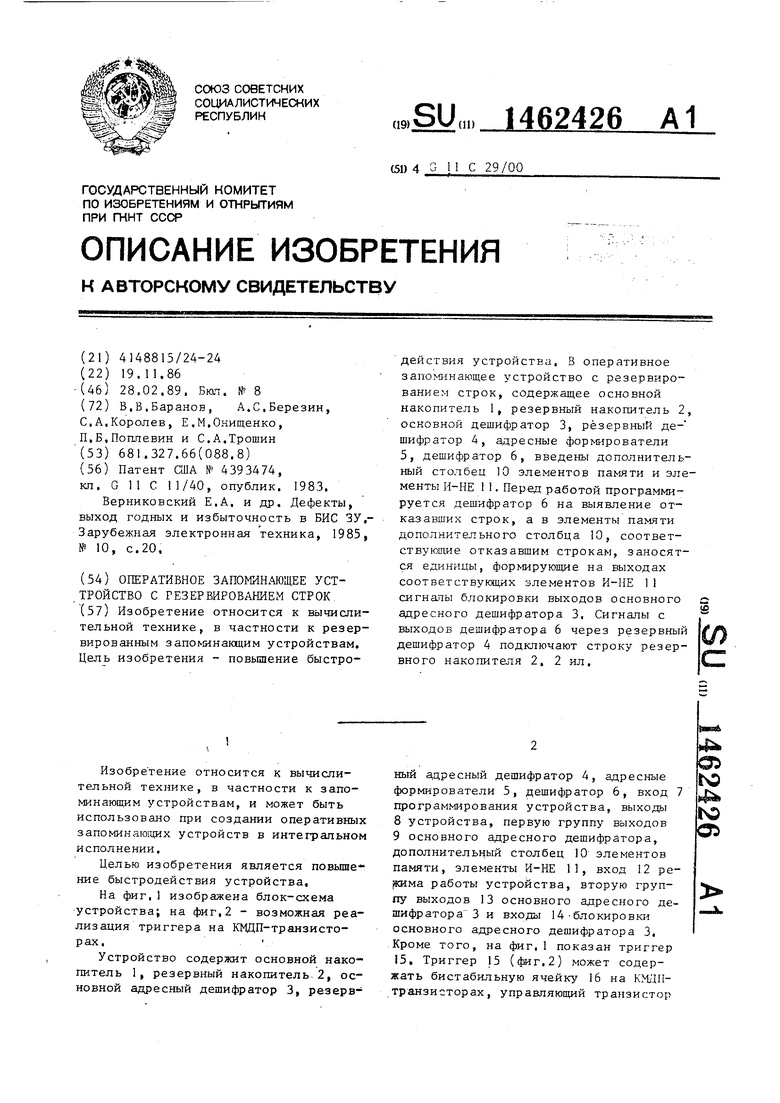

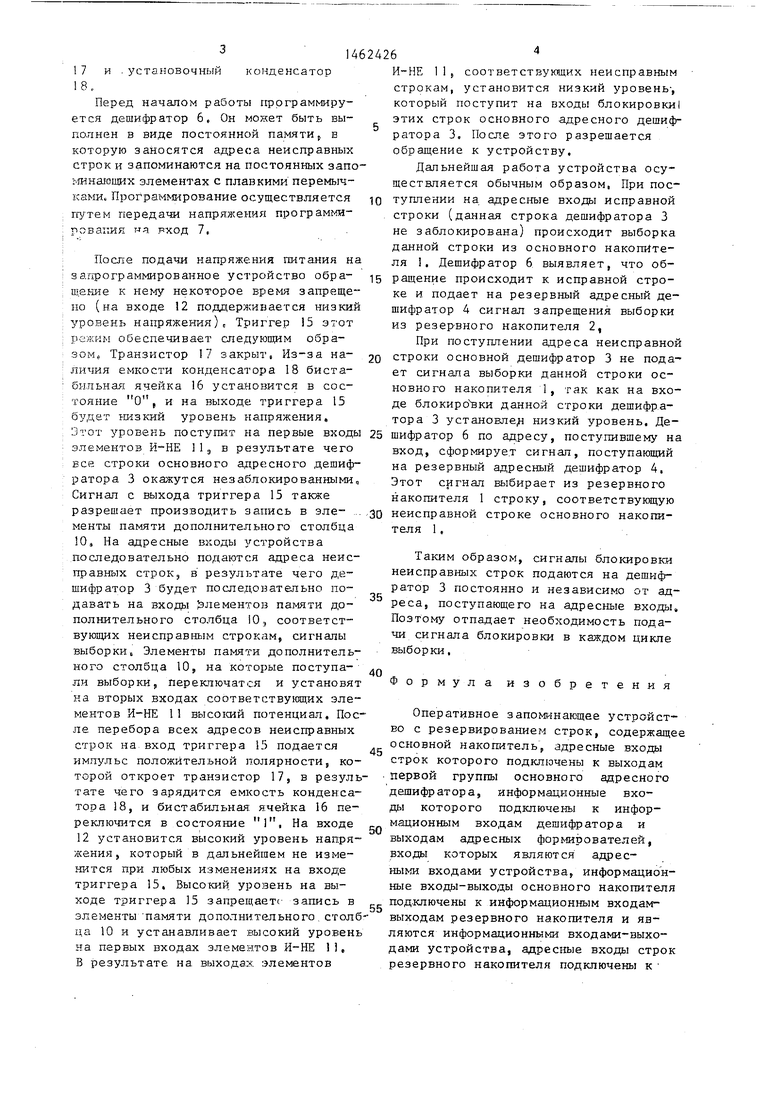

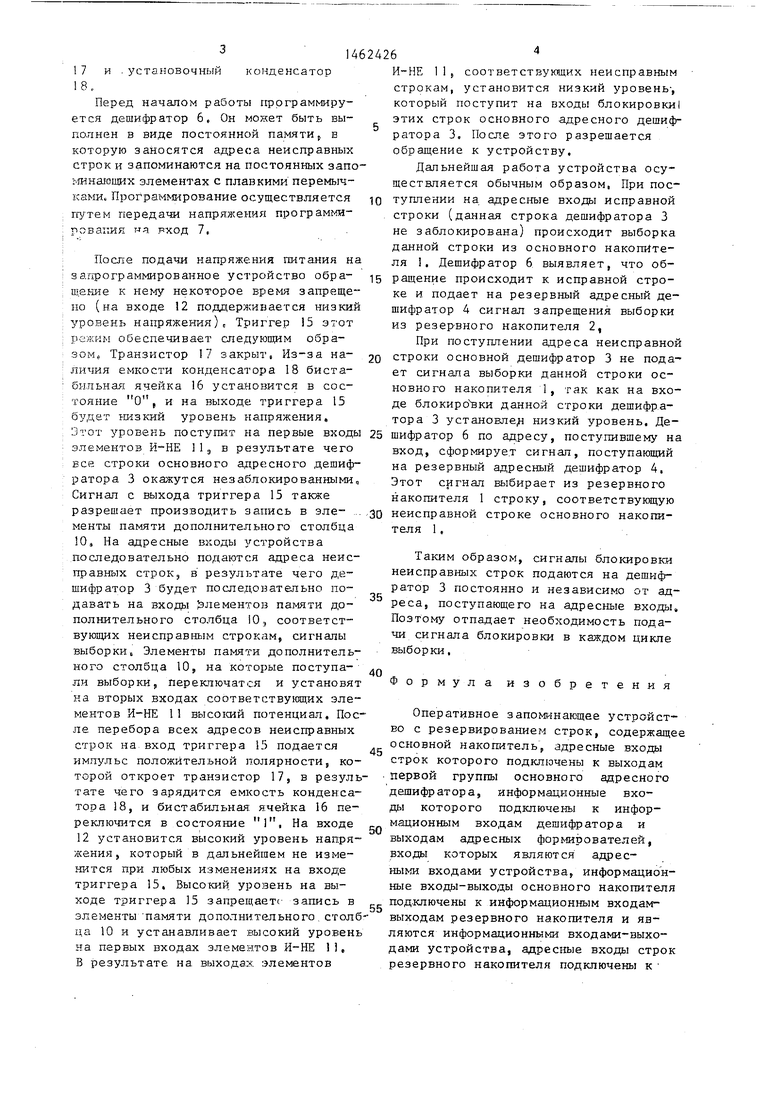

На фиг.1 изображена блок-схема устройства; на фиг,2 - возможная реализация триггера на КМДП-транзисто- рах.

Устройство содержит основной накопитель 1, резервный накопитель 2, основной адресный дешифратор 3, резервный а,цресный дешифратор 4, адресные формирователи 5, дешифратор 6, вход 7 программирования устройства, выходы

8устройства, первую группу выходов

9основного адресного дешифратора, дополнительный столбец 10 элементов памяти, элементы И-НЕ 11, вход 12 ре- яима работы устройства, вторую группу выходов 13 основного адресного дешифратора 3 и входы 14-блокировки основного адресного дешифратора 3.

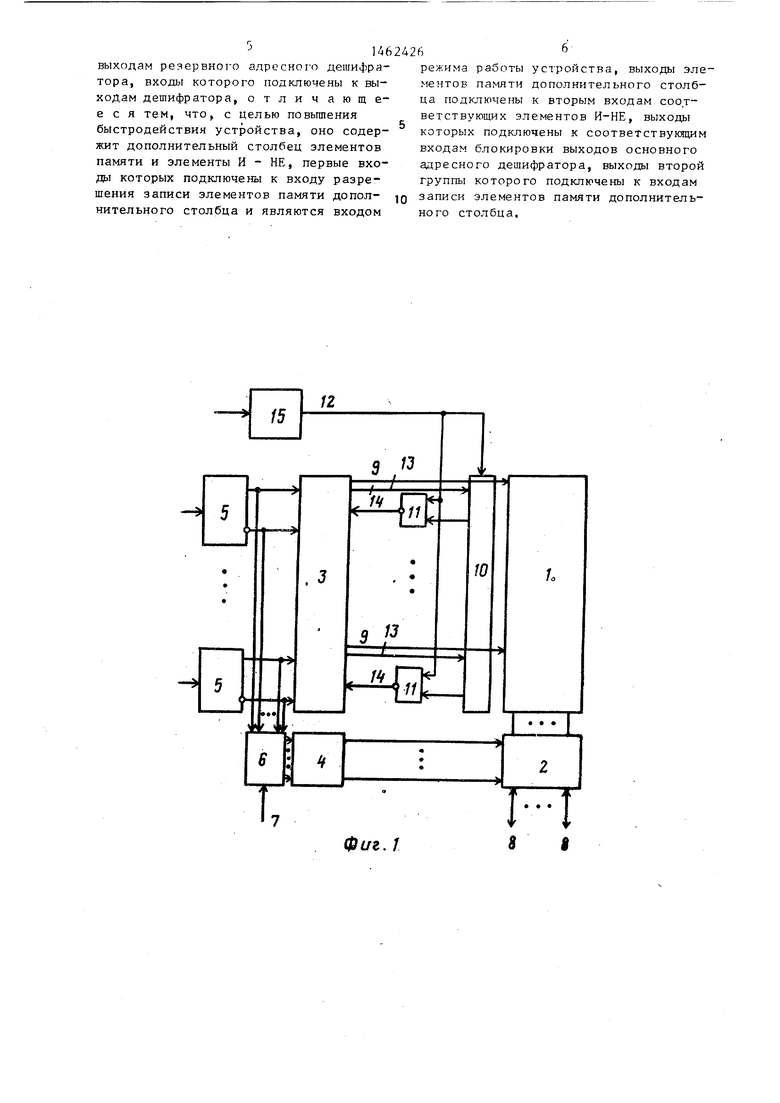

.Кроме того, на фиг.1 показан триггер 15, Триггер 15 (фиг.2) может содержать бистабильную ячейку 16 на KMjjri- транзисторах, управляющий транзистор

ГчЭ

Ю

о:)

и .установочный

конденсатор

17 8,

Перед началом работы ггррграммиру- ется дешифратор 6, Он может быть выполнен в виде постоянной памятир в которую заносятся адреса неисправных строк и запоминаются на постоянных зап гданшоших элементах с плавкими перемычками. Программирование осуществляется путем передачи напряжения программи- РХ- ВВПИЙ wa рход 7,

1

После подачи напряжения питания на запрограммированное устройство обра- ш.ение к нему некоторое время запрещено (на входе 12 поддерживается низкий уровень напряжения)t Триггер 15 этот режиь обеспечивает следующим обра- зоме Транзистор 17 закрыт. Из-за наличия емкости конденсатора 18 биста- бильна ячейка 16 установится в состояние О, и на выходе триггера 15 будет уровень напряжения.

При поступлении адреса неисправной строки основной дешифратор 3 не подает сигнала выборки данной строки основного накопителя 1, так как на входе блокиро ки данной строки дешифр.а- тора 3 ycтaнoвлe низкий уровень. ДеЗтот уровень поступит на первые входы 25 шифратор 6 по адресу, поступившему на

35

элементов И-НЕ 11, в результате чего все строки основного адре;сного дешифратора 3 окажутся незаблокированными. Сигнал с выхода триггера 15 также разрешает производить запись в зле- „. менты памяти дополнительного столбца 10, На адресные входы устройства последовательно подаются адреса неисправных строк, в результате чего дешифратор 3 будет последовательно подавать на входь Элементов памяти дополнительного столбца 10, соответствующих неисправным строкам, сигналы выборки. Элементы дополнительного столбца 10, на которые поступали выборки, переключатся и установят ка вторых входах соответству(щих элементов И-НЕ 1 высокий потенциал. После перебора всех адресов неисправных строк на вход триггера 15 подается,j. основной накопитель, адресные входы

имяульс положительной полярности, ко- строк которого подключены к выходам торой откроет транзистор 17, в резуль- -первой группы тате чего зарядится емкость конденсатора 18, и бистабильная: ячейка 16 переключится в состояние 1, На входе 12 установится высокий уровень напрявход, сформирует сигнал, поступающей на резервный адресный дешифратор 4, Этот сигнал выбирает из резервного накопителя 1 строку, соответствукнцую 3D неисправной строке основного накопителя 1,

Таким образом, сигналы блокировки неисправных строк подаются на дешифратор 3 постоянно и независимо от адреса, поступающего на адресные входы. Поэтому отпадает необходимость подачи сигнала блокировки в каждом цикле выборки,

40

Фор мул

изобретения

Оперативное запоминающее устройство с резервированием строк, содержащее

50

первои группы основного адресного дешифратора, информационные входы которого подключены к информационным входам дешифратора и выходам адресных формирователей, входы которых являются адрес- ныьм входами устройства, информационные входгз1-выхсды основного накопителя

жения, который в дальнейшем не измепервои группы основного адресного дешифратора, информационные входы которого подключены к информационным входам дешифратора и выходам адресных формирователей, входы которых являются адрес- ныьм входами устройства, информационные входгз1-выхсды основного накопителя

нится при любых изменениях на входе триггера 15, Высокий уровень на выходе триггера 15 запрещаете запись впод.ключены к информационным входам- элементы-памяти дополнительного.столб- выходам резервного накопителя и яв- ца 10 и устанавливает высокий уровеньляются информационными входами-выхо- на первых входах элементов И-НЕ П,дами устройства, адресные входы строк В результате на выходах элементоврезервного накопителя подключены к

И-НЕ

0

g

0

, соответствующих неисправным строкам, установится низкий уровень-, который поступит на входы блокировки этих строк основного адресного дешифратора 3. После этого разрещается обращение к устройству.

Дальнейшая работа устройства осуществляется обычным образом, При поступлении на адресные входа исправной строки (данная строка дешифратора 3 не заблокирована) происходит выборка данной строки из основного накопИте- ля I. Дешифратор 6 выявляет, что обращение происходит к исправной строке и подает на резервный адресный дешифратор 4 сигнал запрещения выборки из резервного накопителя 2,

При поступлении адреса неисправной строки основной дешифратор 3 не подает сигнала выборки данной строки основного накопителя 1, так как на входе блокиро ки данной строки дешифр.а- тора 3 ycтaнoвлe низкий уровень. Де5 шифратор 6 по адресу, поступившему на

,j. основной накопитель, адресные входы

вход, сформирует сигнал, поступающей на резервный адресный дешифратор 4, Этот сигнал выбирает из резервного накопителя 1 строку, соответствукнцую 3D неисправной строке основного накопителя 1,

35

,j. основной накопитель, адресные входы

Таким образом, сигналы блокировки неисправных строк подаются на дешифратор 3 постоянно и независимо от адреса, поступающего на адресные входы. Поэтому отпадает необходимость подачи сигнала блокировки в каждом цикле выборки,

,j. основной накопитель, адресные входы

40

Фор мул

изобретения

основной накопитель, адресные входы

Оперативное запоминающее устройство с резервированием строк, содержащее

строк которого подключены к выходам -первой группы

0

первои группы основного адресного дешифратора, информационные входы которого подключены к информационным входам дешифратора и выходам адресных формирователей, входы которых являются адрес- ныьм входами устройства, информационные входгз1-выхсды основного накопителя

под.ключены к информационным входам- выходам резервного накопителя и яв- ляются информационными входами-выхо- дами устройства, адресные входы строк резервного накопителя подключены к

1/.

выходам резервного адресного дешифра тора, входы которого подключены к выходам дешифратора, отличающе е с я тем, что, с целью повышения быстродействия устройства, оно содержит дополнительный столбец элементов памяти и элементы И - НЕ, первые входы которых подключены к входу разрешения записи элементов памяти дополнительного столбца и являются входом

фиг. 1

2426

режима работы устройства, выходы элементов памяти дополнительного столбца подключены к вторым входам соответствующих элементов И-НЕ, выходы которых подключены к соответствукяцим входам блокировки выходов основного адресного дешифратора, выходы второй группы которого подключены к входам Q записи элементов памяти дополнительного столбца.

I-T

17

// I Ць

-J bU

I

фиг. 2

| Патент GUA № 4393474, кп | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Верниковский Е.А | |||

| и др | |||

| Дефекты, выход годных и избыточность в БИС ЗУ,- Зарубежная электронная техника, 1985, № 10, с.20. | |||

Авторы

Даты

1989-02-28—Публикация

1986-11-19—Подача