Изобретение относится к вычислительной технике, в частности к архитектурам перестраиваемых матричных процессорных СБИС, использующих структурную перестройку, т.е. замену отказавших блоков обработки информации на резервные,

Сущность изобретения состоит в расширении функциональных возможностей путем обеспечений работоспособного состояния матрицы БОИ в целом при возникновении такого распределения отказавших БОИ, которые в устройстве-прототипе приводят к ФО, но при меньшей вычислительной размерности матрицы переводят в режим транзита БОИ крайних строк и столбцов, т.е. их последовательного вычеркивания,

Например, после первого вычеркивания первые строки и столбец и N-e - строка и столбец как бы перестают существовать, а (М-1)-я строка и столбец становятся резервными. Таким образом, если отказавшие БОИ, находятся в вычеркнутых строках, то после изменения в них режима эти строки исключены из рассмотрения, а матрица в целом сохраняет работоспособность, но при меньшей размерности - (N-2)-x (N-2) и

т.д.

Предлагаемое устройство обеспечивает расширение области применения для построения матричных процессорных СБИС с деградирующей размерностью (производительностью), а также СБИС с управляемой размерностью вычислительной структуры.

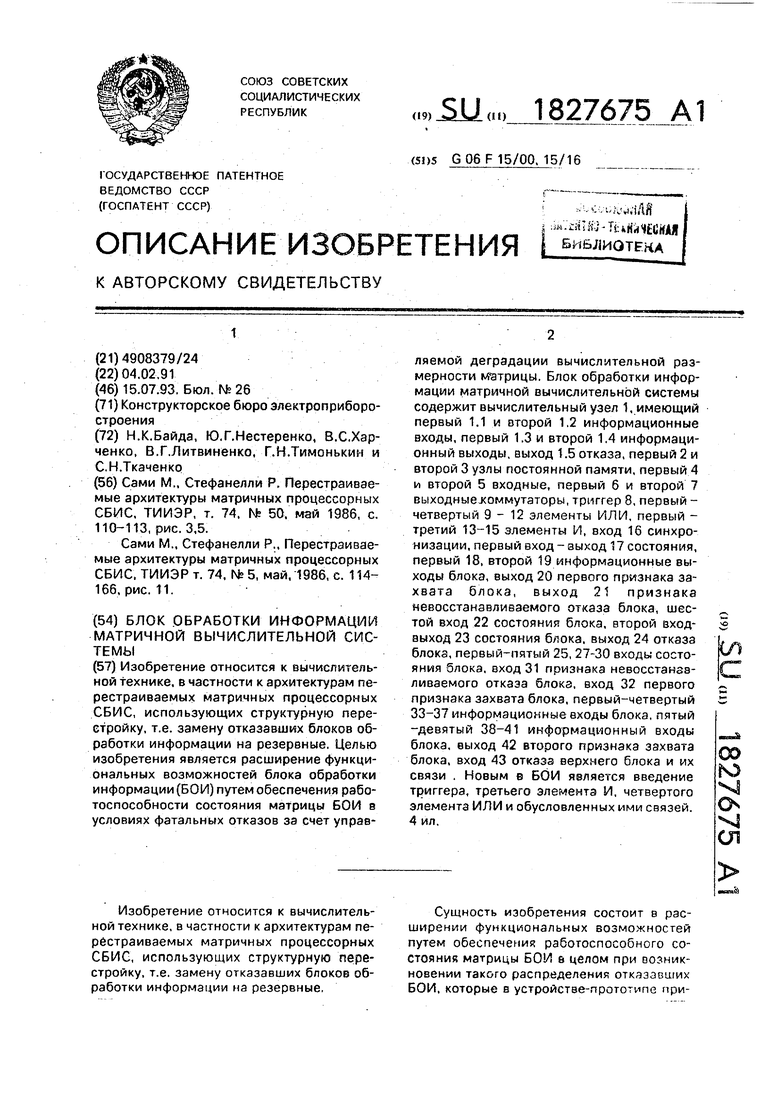

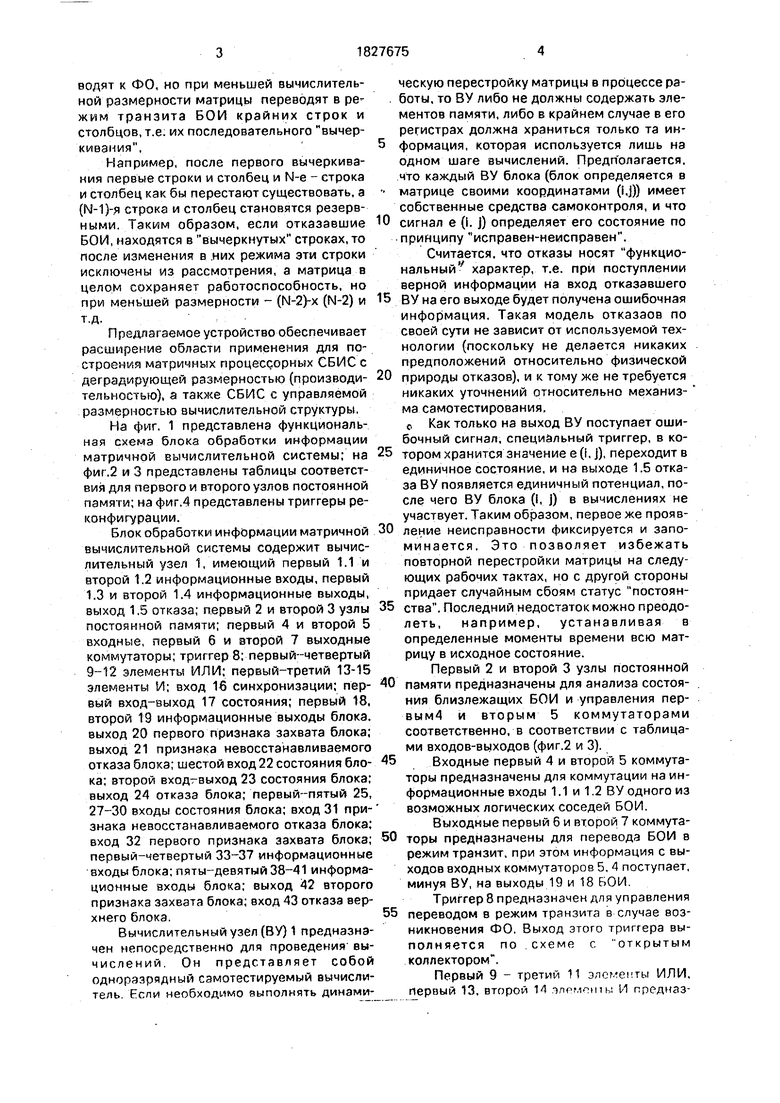

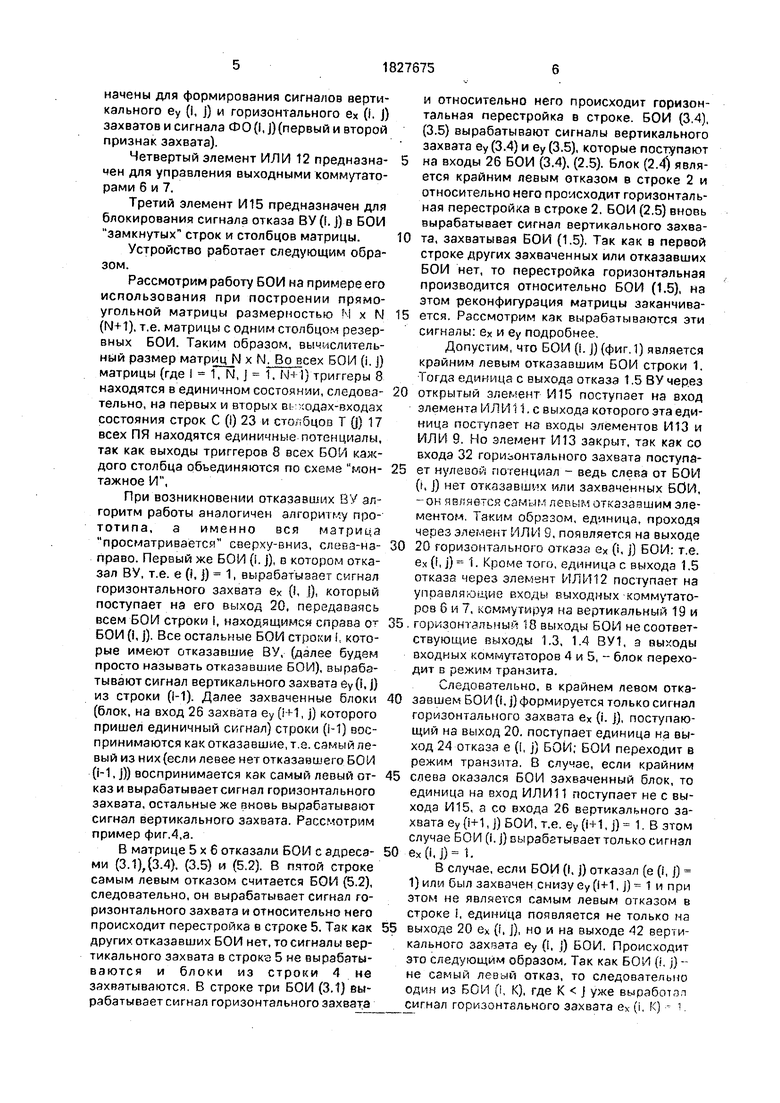

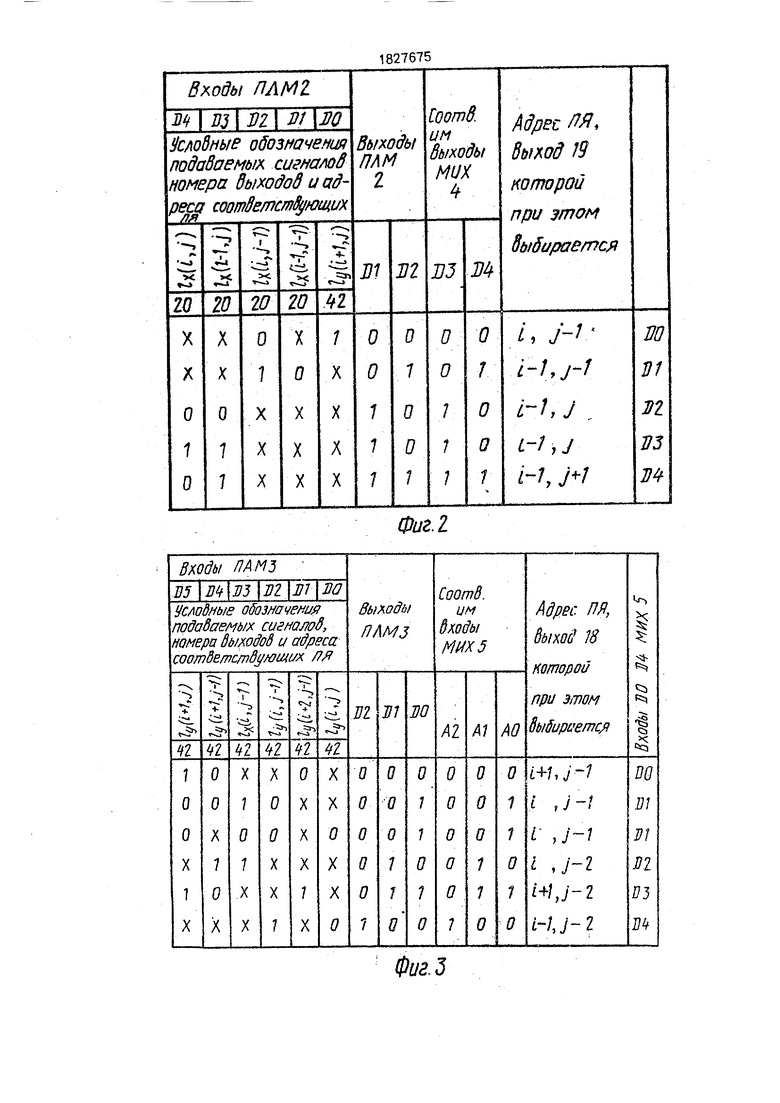

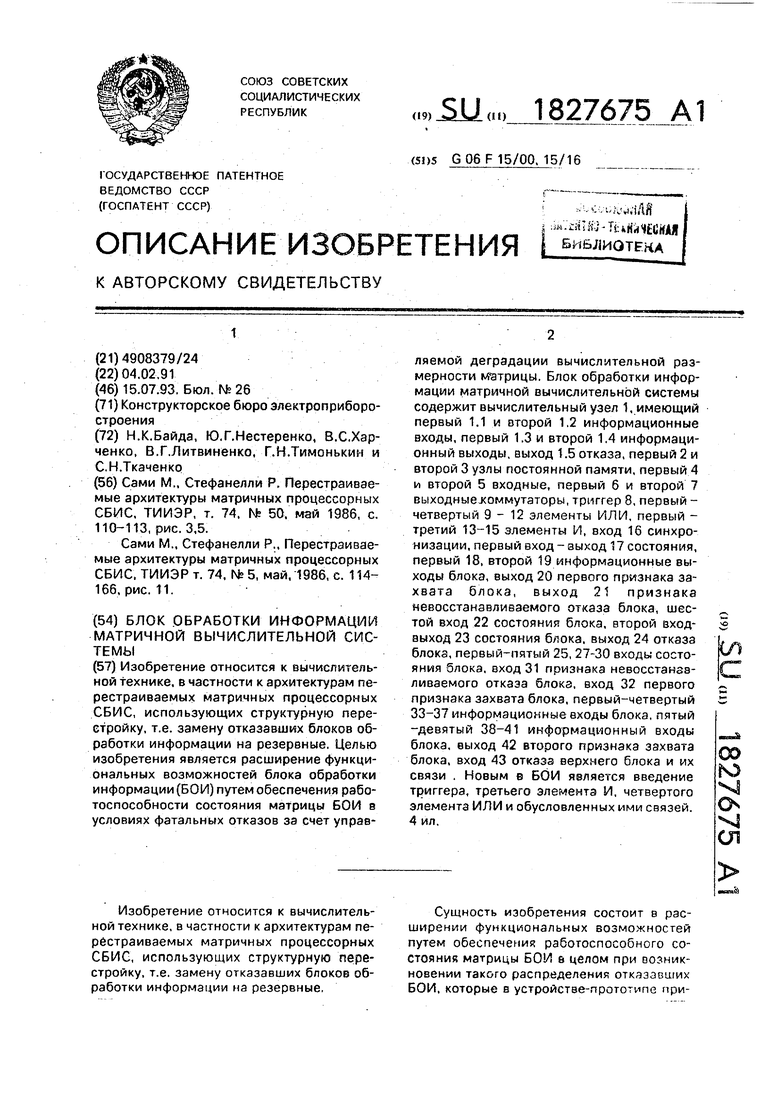

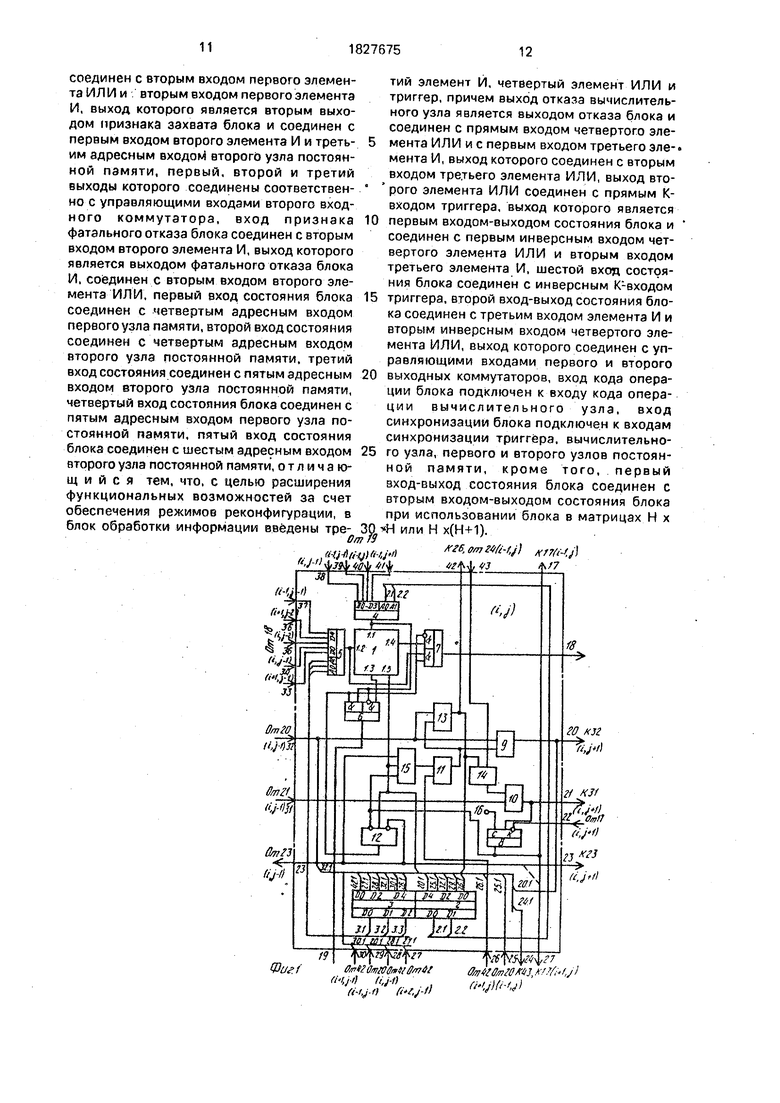

На фиг. 1 представлена функциональная схема блока обработки информации матричной вычислительной системы; на фиг.2 и 3 представлены таблицы соответствия для первого и второго узлов постоянной памяти; на фиг.4 представлены триггеры реконфигурации.

Блок обработки информации матричной вычислительной системы содержит вычислительный узел 1, имеющий первый 1.1 и второй 1,2 информационные входы, первый 1.3 и второй 1.4 информационные выходы, выход 1.5 отказа; первый 2 и второй 3 узлы постоянной памяти; первый 4 и второй 5 входные, первый 6 и второй 7 выходные коммутаторы; триггер 8; первый-четвертый 9-12 элементы ИЛИ; первый-третий 13-15 элементы И; вход 16 синхронизации; первый вход-выход 17 состояния; первый 18, второй 19 информационные выходы блока, выход 20 первого признака захвата блока; выход 21 признака невосстанавливаемого отказа блока; шестой вход 22 состояния блока; второй входгвыход 23 состояния блока; выход 24 отказа блока; первый-пятый 25, 27-30 входы состояния блока; вход 31 признака невосстанавливаемого отказа блока; вход 32 первого признака захвата блока; первый-четвертый 33-37 информационные входы блока; пяты-девятый 38-41 информационные входы блока; выход 42 второго признака захвата блока; вход 43 отказа верхнего блока.

Вычислительный узел (ВУ) 1 предназначен непосредственно для проведения вычислений. Он представляет собой одноразрядный самотестируемый вычислитель Рспи необходимо яыполнять динамическую перестройку матрицы в процессе работы, то ВУ либо не должны содержать элементов памяти, либо в крайнем случае в его регистрах должна храниться только та информация, которая используется лишь на одном шаге вычислений. Предполагается, что каждый ВУ блока (блок определяется в

матрице своими координатами (i,j)) имеет собственные средства самоконтроля, и что

0 сигнал е (i. j) определяет его состояние по принципу исправен-неисправен.

Считается, что отказы носят функциональный1 характер, т.е. при поступлении верной информации на вход отказавшего

5 ВУ на его выходе будет получена ошибочная информация. Такая модель отказаов по своей сути не зависит от используемой технологии (поскольку не делается никаких предположений относительно физической

0 природы отказов), и к тому же не требуется никаких уточнений относительно механизма самотестирования. о Как только на выход ВУ поступает ошибочный сигнал, специальный триггер, в ко5 тором хранится значение е (i, j), переходит в единичное состояние, и на выходе 1.5 отказа ВУ появляется единичный потенциал, после чего ВУ блока (i, j) в вычислениях не участвует. Таким образом, первое же прояв0 ление неисправности фиксируется и запоминается. Это позволяет избежать повторной перестройки матрицы на следующих рабочих тактах, но с другой стороны придает случайным сбоям статус постоян5 ства. Последний недостаток можно преодо- леть, например, устанавливая в определенные моменты времени всю матрицу в исходное состояние.

Первый 2 и второй 3 узлы постоянной

0 памяти предназначены для анализа состояния близлежащих БОИ и управления пер- вым4 и вторым 5 коммутаторами соответственно, в соответствии с таблицами входов-выходов (фиг.2 и 3).

5 Входные первый 4 и второй 5 коммутаторы предназначены для коммутации на информационные входы 1.1 и 1.2 ВУ одного из возможных логических соседей БОИ.

Выходные первый б и второй 7 коммута0 торы предназначены для перевода БОИ в режим транзит, при этом информация с выходов входных коммутаторов 5, 4 поступает, минуя ВУ, на выходы 19 и 18 ЬОИ.

Триггер 8 предназначен для управления

5 переводом в режим транзита в случае возникновения ФО, Выход этого триггера выполняется по схеме с открытым коллектором.

Первый 9 - третий 11 элсгегты ИЛИ, первый 13. второй 14 ТЛРМ.-ЧПЫ И предназначены для формирования СИГНЭУЮВ вертикального еу (i, j) и горизонтального ex (f. J) захватов и сигнала OO(IJ)(первый и второй признак захвата).

Четвертый элемент ИЛИ 12 предназна- чен для управления выходными коммутаторами 6 и 7.

Третий элемент И15 предназначен для блокирования сигнала отказа ВУ (i. j) в БОИ замкнутых строк и столбцов матрицы.

Устройство работает следующим образом.

Рассмотрим работу БОИ на примере его использования при построении прямоугольной матрицы размерностью N х N (N+1), т.е. матрицы с одним столбцом резервных БОИ. Таким образом, вычислительный размер матриц х NL Во всех БОИ (i. j) матрицы (где I 1. N, j - 1. N-H) триггеры 8 находятся в единичном состоянии, следова- тельно, на первых и вторых выходах-входах состояния строк С (1) 23 и столбцов Т (j) 17 всех ПЯ находятся единичные потенциалы, так как выходы триггеров 8 всех БОИ каждого столбца объединяются по схеме мон- тажное И,

При возникновении отказавших ВУ алгоритм работы аналогичен алгоритму прототипа, а именно вся матрица просматривается сверху-вниз, слева-на- право. Первый же БОИ (i. j), в котором отказал ВУ, т.е. е (, j) 1, вырабатызает сигнал горизонтального захватз ex (i, i), который поступает на его выход 20, передаваясь всем БОИ строки i, находящимся справа от БОИ (i, j). Все остальные БОИ строки i, которые имеют отказавшие ВУ, (далее будем просто называть отказавшие БОИ), вырабатывают сигнал вертикального захвата еу (i, j) из строки (1-1). Далее захваченные блоки (блок, на вход 26 захвата еу (+1, j) которого пришел единичный сигнал) строки (1-1) воспринимаются как отказавшие, т.е. самый левый из них (если левее нет отказавшего БОИ (М, j)) воспринимается как самый левый от- каз и вырабатывает сигнал горизонтального захвата, остальные же вновь вырабатывают сигнал вертикального захвата. Рассмотрим пример фиг.4,а.

В матрице 5x6 отказали БОИ с адреса- ми (3.1),(3.4), (3.5) и (5.2). В пятой строке самым левым отказом считается БОИ (5.2), следовательно, он вырабатывает сигнал горизонтального захвата и относительно него происходит перестройка в строке 5. Так как других отказавших БОИ нет, то сигналы вертикального захвата в строке 5 не вырабатываются и блоки из строки 4 не захватываются. В строке три БОИ (3.1) вырабатывает сигнал горизонтального захвата

и относительно него происходит горизонтальная перестройка в строке. БОИ (3.4), (3.5) вырабатывают сигналы вертикального захвата еу (3.4) и еу (3.5), которые поступают на входы 26 БОИ (3.4), (2.5). Блок (2.4) является крайним левым отказом в строке 2 и относительно него происходит горизонтальная перестройка в строке 2. БОИ (2.5) вновь вырабатывает сигнал вертикального захвата, захватывая БОИ (1.5), Так как в первой строке других захваченных или отказавших БОИ нет, то перестройка горизонтальная производится относительно БОИ (1.5), на этом реконфигурация матрицы заканчивается. Рассмотрим как вырабатываются эти сигналы: ех и еу подробнее.

Допустим, что БОИ (L )(фиг,1) является крайним левым отказавшим БОИ строки 1. Тогда единица с выхода отказа 1.5 ВУ через открытый элемент И15 поступает на вход элемента ИЛИ 11, с выхода которого эта единица поступает на входы элементов И13 и ИЛИ 9. Но элемент И13 закрыт, так как со входа 32 горизонтального захвата поступает нулевой потенциал - ведь слева от БОИ (t, j) нет отказавших мли захваченных БОИ, -он является самим левым отказавшим элементом. Таким обрззом, единица, проходя через элемент ИЛИ 9, появляется на выходе 20 горизонтального отказа ех (i, j) БОИ: т.е. ex(lij)1. Кроме того, единица с выхода 1,5 отказа через элемент ИЛИ12 поступает на управляющие входы выходных-коммутаторов 6 и 7, коммутируя на вертикальный 19 и . горизонтальный 18 выходы БОИ несоответствующие выходы 1.3, 1.4 ВУ1, з выходы входных коммутаторов 4 и 5, - блок переходит в режим транзита.

Следовательно, в крайнем левом отказавшем БОИ (i, j) формируется только сигнал горизонтального захвата ех (i. j), поступающий на выход 20. поступает единица на выход 24 отказа е (I, j) БОИ; БОИ переходит в режим транзита. В случае, если крайним слева оказался БОИ захваченный блок, то единица на вход ИЛИ11 поступает не с выхода И15, а со входа 26 вертикального захвата ey(i+1,j) БОИ, т.е. ey(i+1, j) 1. В этом случае БОИ (i. j) вырабатывает только сигнал ex(i,J)t.

В случае, если БОИ (I, j) отказал (е (f, j) 1) или был захвачен снизу еу (i+1, J) 1 и при этом не явлдется самым левым отказом в строке i. единица появляется не только на выходе 20 бх (f, j), но и на выходе 42 вертикального захгзата еу (I, .{) БОИ. Происходит это следующим образом. Так как БОИ (i. j) - не самый левый отказ, то следовательно один из БОИ (I, К), где К j уже выработал сигнал горизонтального захвата ех (i, К) - 1

Эта единица поступает на вход 32 горизонтального отказа ех (i. И) БОЙ, и, проходя через элемент 1ЛЛИ9, поступает на выход 20, т.е. ex (i, j) - 1. Эта же единица со входа 32 поступает на вход элемента И13, на дру- той вход которого поступает единица с выхода элемента ИЛИ 11, ведь БОИ (I, J) является отказавшим или захваченным. Т.о., на выходе И13 формируется единичный потенциал, который поступает на выход 42 вертикального захвата ex (i, j) БОИ. Следовательно, БОИ (i, j) сформировала сигналы ех (М)-1иуу(и)1.

Аналогичные действия происходят во всех БОИ матрицы, и каждый БОИ, анализи- руя сигналы ех и еу соседних БОИ решает, выход какого БОИ скоммутировак на вход своего ВУ. Анализ этот выполняется с помощью двух первого 2 и второю 3 узлов постоянной памяти, Таблицы входов-выхЪ- дов приведены на фиг.2 и 3. на этих же таблицах приведено какие сигналы (ех или еу) и с выходов каких БОИ (относительно БОИ (i. j)) коммутируются на их входы, а также информационные выходы каких БОИ прм том или ином сочетании сигналов выбираются с помощью выходных коммутаторов.Рассмотрим пример выполнения коммутации выходов БОИ на примере БОИ (2.4) фиг.4,а БОИ (2.4) является захвачен- ным, так как под ним расположен отказавший БОИ (3.4), не являющийся самым левым отказавшим БОИ строки 3. Следовательно, еу (1+1, j) у 1. Но БОИ (2.4) является самым левым захваченным БОИ строки 2, следова- тельно на его вход 32 поступает нуль, т.е. ех (l, j-1) 1. Обращаясь к фиг.2, видим, что такому состоянию соответствует первая строка таблицу, - на вертикальный вход 1.1 ВУ { БОИ (i, j) коммутируется информацией- ный вертикальный выход 19 БОЙ (I, -1)что и показано на фиг.4ба. Обращаясь к фиг.З и зная что еу (1+1, j) 1, видим, что нас будет интересовать первая и пятая строки таблицы, а в этих строках сигналы, поступающие на входы О 4 и D 1. Те. нас интересуют сигналы еу (1+1, j-1) и еу (I+2. J-1) или еу (3.3) и еу (4.3), ведь i 2, a j 4, Итак, обратившись к БОИ (3.3), видим, что он является исправным и незахваченным, следовательно, сиг- нал вертикального захвата он вырабатывать не может еу (3 3) 0. Рассмотрев БОИ (4.3), видим, что в строке 4 нет даже сигнала горизонтального захвата ни в одном из БОИ, так как строка 4 не содержит отказавших или захваченных БОИ, следовательно еу (4 3) О Т о., мы идентифицировали требуемую нам строку таблицы (фиг.З) - это строка один Следовательно, на горизонтальный информационный вход 1.2 ВУ БОИ ( 4) будет коммутироваться через выходной коммутатор 7 БОИ (3.3) и входной коммутатор 5 БОИ (2.4) выход 1.4 ВУ1 БОИ (3.3), что и показано на фиг,4,а.

Из всего вышесказанного следует следующее:

-на входы 32 БОИ (I, 1), где 1. N, должны подаваться нулевые потенциалы;

-на входы 26 БОИ (N. j), где j 1, N+1 или j 1, N (в случае столбца и строки резервных БОИ), должны также подаваться нулевые потенциалы;

-данный алгоритм не сможет произвести реконфигурацию в случае, когда будет захватываться отказавший БОИ (i. j), т.е. e(i, J) 1 иеу(1+1, j) 1,

Рассмотрим последний случай подробнее. Для выявления случаев, когда над отказавшим или захваченным БОИ (i. j), не являющимся крайним левым в строке i, находится отказавший БОИ (i-1, j), вводится элемент И14, на один из выходов которого уступает сигнал е (i-1, j). Таким образом, если формируется сигнал вертикального захвата ey(i,j), то единица с выхода И13 поступает и на вход И14, на выходе которого появится единичный потенциал, который, пройдя через элемент ИЛИ 10, появится на выходе 21 ФО (i, j). Контролируя выход 21 БОИ (i, N), можно определить в какой строке возник ФО. После возникновения сигнала ФО дальнейшая эксплуатация матрицы не- .возможна, так как реконфигурация не может быть выполнена. Так было в устройстве-прототипе, но в предлагаемых БОИ этот алгоритм дополнен следующим образом.

Известно, что в СБИС отказы концентрируются в силу особенностей технологии к краю кристалла. Следовательно, логично предположить, что сигнал ФО наиболее вероятно вызван отказами в крайних строках и столбцах БОИ. Поэтому предлагается при возникновении сигнала ФО переводить в режим транзита с блокировкой сигнала е (I, j). Крайние строки и столбцы, как бы снимая внешние БОИ, в надежде, что, исключив из рассмотрения отказавшие БОИ или их часть, удастся избежать ФО, пусть и ценой сокращения вычислительной размерности матрицы. Рассмотрим этот процесс подробнее.

На входы 43 отказа верхнего БОИ блоков верхней строки, т е БОИ (1, j), подаются единичные сигналы, ведь сверху блоков, а тем более исправных, нет вообще Т о , при распределении отказавших БОИ таком, как показано на фиг.4,6, возникает сигнал ФО в БОИ (1,6). Следовательно, на прямой К-вход триггера 8 БОИ (1,6) поступает единичный

потенциал, на инверсный К-вход поступает сигнал логического нуля, так как справа больше столбцов БОИ нет (т.е. на входы 22 всех БОИ (I. N или N+1) поступают сигналы логического нуля)). По очередному тактовому импульсу, поступающему со входа 16 синхронизации, триггер 8 перейдет в нулевое состояние, а так как все триггеры 8 БОИ столбца 6 и 1 строки 5 и 1 объединены с помощью перемычек (пунктир на фиг.1) по схеме монтажное И, то на всех входах-выходах состояния строки С () 23 и столбца Т (j) 24 будут равны нулю. Следовательно, эти нули, поступая на один из входов элемента ИЛИ 12, переведут БОИ этих строк и столбцов в режим транзит. После этого мы получим матрицу БОИ вычислительной размерностью 3 х 3 с одним столбцом резервных БОИ, сигнал ФО в БОИ (1,6) исчезнет, так как в вычеркнутые строки попали БОИ, вызывавшие его формирование. На фиг.Зв показан окончательный вид получаемой матрицы.

Перемычка, изображенная на фиг.1 пунктиром, выполняется не во всех БОИ матрицы, а лишь в БОИ (i, j) с одним столбцом резервных БОИ при i j (j N/2), при j N-1 + 1 (t N/2 + 1) и при j 1+ 1 (i N/2+1), в матрицах со строкой и столбцом резервных БОИ (который является самым верхним) перемычки выполняются в БОИ (i, j)npn j N-i+1.

В случае если сигнал ФО сформировался на в крайнем БОИ, как рассмотрено выше, то переключение триггера в этом БОИ(1, j) не происходит, так как следующий столбец 0+1) еще не переведен в режим транзита, т.е. Т (j+1) 1, и на вход 22 поступает единичный потенциал, - изменение состояния триггера 8 запрещается,

И еще, на входы 31 ФО БОИ (1,j) должны подаваться нулевые потенциалы.

Т.о., при возникновении таких множеств отказавших БОИ, которые в устройстве-прототипе приводили к ФО, в матрице, построенной из предлагаемых БОИ, будет приводить к сжатию матрицы к центру: квадратная матрица сжимается в точку, а прямоугольная - в линию. Контролировать, - какой размер вычислительной матрицы обеспечивается в данный момент, можно по сигналам с выходов состояния 17 или 23 крайних БОИ какой-либо строки (первой или последней) или столбца (первого или последнего). Кроме того, такая матрица допускает внешнее управление размерностью матрицы. Так, подавая на входы-выходы 17 или 23 БОИ крайних строк или столбцов сигналов логического нуля с выхода какоголибо элемента, выход которого выполнен по схеме с открытым коллектором, можно принудительно переводить в режим транзита любые строки и столбцы матрицы, ис5 пользующей данные БОИ. Все БОИ матрицы работают под управлением одного тактового генератора.

Формула изобретения

Блок обработки информации матрич0 ной вычислительной системы, содержащий вычислительный узел, первый входной и первый выходной коммутаторы, второй входной и второй выходной коммутаторы, первый и второй узлы постоянной памяти,

5 первый и второй элементы И, первый, второй и третий элементы ИЛИ, причем с первого по четвертый информационные входы блока соединены соответственно с информационными- входами первого входного

0 коммутатора, выход которого соединен с первым информационным входом вычислительного узла и с первым.информационным входом второго выходного коммутатора, выход которого является первым информаци5 онным выходом блока, с пятого по девятый информационныевходы блока соединены соответственно с информационными входами второго входного коммутатора, выход ко- торого соединен с вторым

0 информационным входом вычислительного узла и с первым информационным входом второго выходного коммутатора, выход которого является вторым информационным выходом блока, первый выход вычислитель5 ного узла соединен с вторым информацион- ным входом первого выходного коммутатора, второй выход вычислительного узла соединен с вторым информационным входом второго выходного

0 коммутатора, первый вход признака захвата блока соединен с. первыми адресными входами первого и второго узлов постоянной памяти, с первым входом первого элемента И и первым входом первого элемента

5 ИЛИ, выход которого является первым выходом признака захвата блока и соединен с вторым адресным входом первого узла постоянной памяти, первый и второй выходы которого соединены с первым и вторым уп0 равляющими входами первого входного коммутатора, вход признака невосстанавливаемого отказа блока соединен с первым входом второго элемента ИЛИ, выход которого является выходом признака невосста5 нэвливземого отказа блока, второй вход признака захвата блока соединен с вторым адресным входом второго узла постоянной памяти и третьим адресным входом первого узла постоянной памяти, с первым вхо- домтретьего элемента ИЛИ, выход которого

соединен с вторым входом первого элемента ИЛИ и вторым входом первого элемента И, выход которого является вторым выходом признака захвата блока и соединен с первым входом второго элемента И и треть- им адресным входом1 второго узла постоянной памяти, первый, второй и третий выходы которого соединены соответствен- но с управляющими входами второго входного коммутатора, вход признака фатального отказа блока соединен с вторым входом второго элемента И, выход которого является выходом фатального отказа блока И. соединен с вторым входом второго элемента ИЛИ, первый вход состояния блока соединен с четвертым адресным входом первого узла памяти, второй вход состояния соединен с четвертым адресным входом второго узла постоянной памяти, третий вход состояния соединен с пятым адресным входом второго узла постоянной памяти, четвертый вход состояния блока соединен с пятым адресным входом первого узла постоянной памяти, пятый вход состояния блока соединен с шестым адресным входом второго узла постоянной памяти, о т л и ч а го- ид и и с я тем, что, с целью расширения функциональных возможностей за счет

беспечения режимов реконфигурации, в

лок обработки информации введены тре- 30 -«Н или Н х(Н+1).

о/л /9.

,-А- ,/,-,)MS,0mZ4ft-t,j)

tt-tj-AffuWWl

«

тий элемент И, четве триггер, причем выхо ного узла является вы соединен с прямым в мента ИЛИ и с первы мента И, выход котор входом третьего элем рого элемента ИЛИ с входом триггера, вых первым входом-выход соединен с первым и вертого элемента ИЛ третьего элемента И ния блока соединен с триггера, второй вход ка соединен с третьим вторым инверсным в мента ИЛИ, выход ко равляющими входам выходных коммутато ции блока подключе ции вычислитель синхронизации блок синхронизации триг го узла, первого и вт ной памяти, кро вход-выход состояни вторым входом-выхо при использовании б

./,

J$.

Ц/7

p/rrt a/ zdfai i0m4t f ,j-f .

rt-V ft (l

тий элемент И, четвертый элемент ИЛИ и триггер, причем выход отказа вычислительного узла является выходом отказа блока и соединен с прямым входом четвертого элемента ИЛИ и с первым входом третьего эле- мента И, выход которого соединен с вторым входом третьего элемента ИЛИ, выход второго элемента ИЛИ соединен с прямым К- входом триггера, выход которого является первым входом-выходом состояния блока и соединен с первым инверсным входом четвертого элемента ИЛИ и вторым входом третьего элемента И, шестой вход состояния блока соединен с инверсным входом триггера, второй вход-выход состояния блока соединен с третьим входом элемента И и вторым инверсным входом четвертого элемента ИЛИ, выход которого соединен с управляющими входами первого и второго выходных коммутаторов, вход кода операции блока подключен к входу кода операции вычислительного узла, вход синхронизации блока подключен к входам синхронизации триггера, вычислительного узла, первого и второго узлов постоянной памяти, кроме того, первый вход-выход состояния блока соединен с вторым входом-выходом состояния блока при использовании блока в матрицах Н х

iftyfyt

Oatie/nZOM, ,jl Wjlft- j)

Фиг. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий между процессорами | 1989 |

|

SU1716514A2 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1998 |

|

RU2133054C1 |

| Ячейка однородной среды | 1989 |

|

SU1756898A1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2185656C2 |

| РАСПРЕДЕЛИТЕЛЬНАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 1997 |

|

RU2122229C1 |

| Устройство для сопряжения многопроцессорной вычислительной системы | 1983 |

|

SU1160423A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СРЕДЫ | 1995 |

|

RU2103724C1 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ | 2000 |

|

RU2198417C2 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| ОТКАЗОУСТОЙЧИВЫЙ МУЛЬТИМИКРОКОНТРОЛЛЕР | 1999 |

|

RU2156492C1 |

Изобретение относится к вычислительной технике, в частности к архитектурам перестраиваемых матричных процессорных СБИС, использующих структурную перестройку, т.е. замену отказавших блоков обработки информации на резервные. Целью изобретения является расширение функциональных возможностей блока обработки информации (БОИ) путем обеспечения работоспособности состояния матрицы БОИ в условиях фатальных отказов за счет управляемой деградации вычислительной размерности матрицы. Блок обработки информации матричной вычислительной системы содержит вычислительный узел 1, имеющий первый 1.1 и второй 1.2 информационные входы, первый 1.3 и второй 1.4 информационный выходы, выход 1.5 отказа, первый 2 и второй 3 узлы постоянной памяти, первый 4 и второй 5 входные, первый 6 и второй 7 выходные-коммутаторы, триггер 8, первый - четвертый 9-12 элементы ИЛИ, первый - третий 13-15 элементы И, вход 16 синхронизации, первый вход-выход 17 состояния, первый 18, второй 19 информационные выходы блока, выход 20 первого признака захвата блока, выход 21 признака невосстанавливаемого отказа блока, шестой вход 22 состояния блока, второй вход- выход 23 состояния блока, выход 24 отказа блока, первый-пятый 25, 27-30 входы состояния блока, вход 31 признака невосстанза- ливаемого отказа блока, вход 32 первого признака захвата блока, первый-четвертый 33-37 информационные входы блока, пятый -девятый 38-41 информационный входы блока, выход 42 второго признака захвата блока, вход 43 отказа верхнего блока и их связи . Новым в БОИ является введение триггера, третьего элемента И, четвертого элемента ИЛИ и обусловленных ими связей. 4 ил. 00 КЭ х| О СП

Фиг.З

а

1,234 5.6

i г j 4 56

ФигЛ

Авторы

Даты

1993-07-15—Публикация

1991-02-04—Подача