. -1 ; . Изобретение относится к вычислительной технике и может быть исполь эовано при построении высоконадежны и стабильных генераторов тактовых и пульсов и делителей частоты. Известен резервированный генератор тактовых импульсов, содержаздий ,в резервируемых генераторов, соединвнншс через блок переключения е вы нодными каскадами и через блоки кон троля с управляющими входами блока переключения l . Однако в этом формирователе возможно нарушение синфазного фомйрова иия последовательностей импульсов в момент отказа ведущего генератора и переключения на резервный генератор Известен также резервированный многоканальный формирователь тактовых импульсов, содержащий в каждом канале источник входных импульсов, соединённый через делитель частоты и элемент совпадения, триггер с мажоритарными элементами, выходед кото рых через узлы установки соединены с установочными входами делителя Г21« Недостаток у-стройства состоит в том, что во время отказа источника входных импульсов или делителя частоты на всех выходах устройства могут возникать импульсные сигнсшы, длительность которых имеет случайный характер. Наиболее близким к предлагаемому является резервированное многоканальное устройство для формирования тактовых импульсов, содержащее в каждом канале резервирования автогенератор, делитель частоты, дешифратор, тригpep памяти, триггер, обратной связи, мажоритарный элемент,триггеры признакд фазы и лО1;ические элементы З . Однако из-за разброса частот автогенераторов постоянно меняются фазовые соотной1ения между сигналами на входах делителей частоты, происходит рассогласование по фазе работы делителей и неодновременное срабатывание дешифраторов и треггеров памяти, что приводит к периодическому удлинению или укорочению периода выходных сигналов, так как мажоритарные элементы .срабатывают от разных пар триггеров памяти, в результате чего период выходньос сигналов устройства не является стабильным и зависит от частот и фазовых соотношений между сигналами всех автогенераторов. Цель изобретения - повышение стабильности генератора.

Поставленная цель достигается тем, что в резервированный генератор, сОдерх ащий в каждом канале последовательно соединенные задающий генератор делитель частоты, дешифратор и триггер памяти, дополнительно вводятся в каждый канал элементы И по числу каналов и. пороговый элемент, входы которого соединены с выходами триггеров памяти каждого канала, а- выход со входом установки в ноль триггера памяти и первыми входами элементов И данного канала, вторые входы которых соединены с выходами соответствуннцих дешифраторов других каналов, а выходы - с соответствующими установочными входами делителя частоты данного канала.

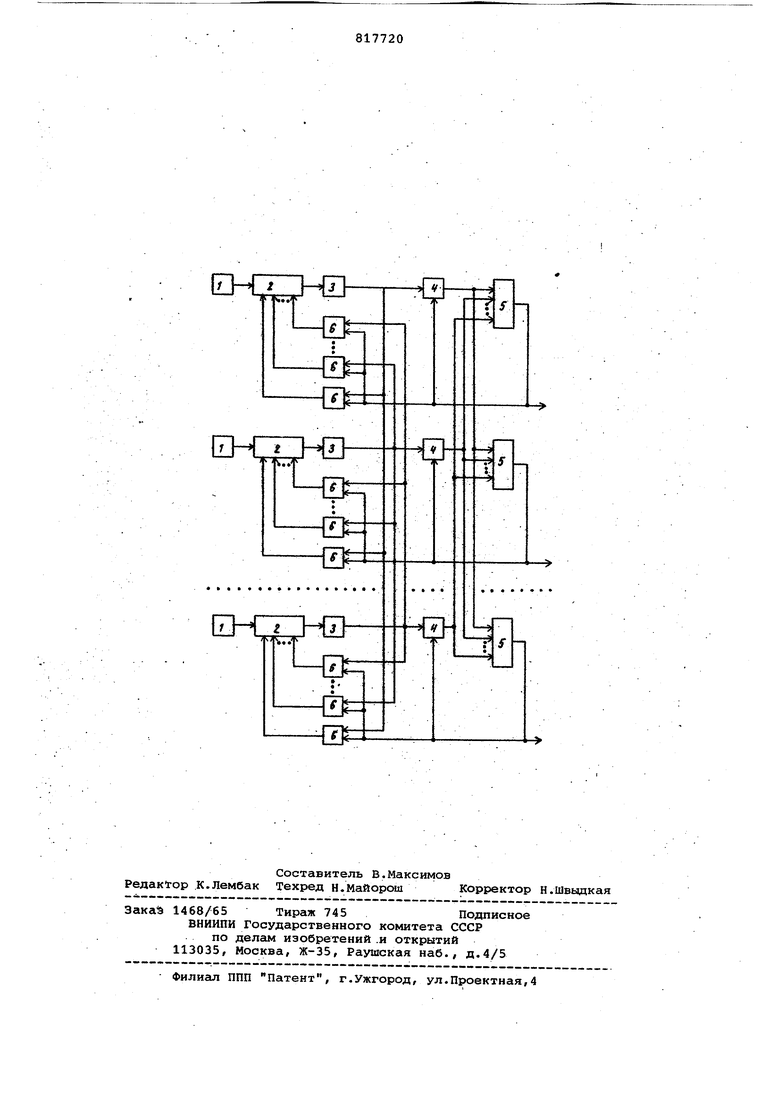

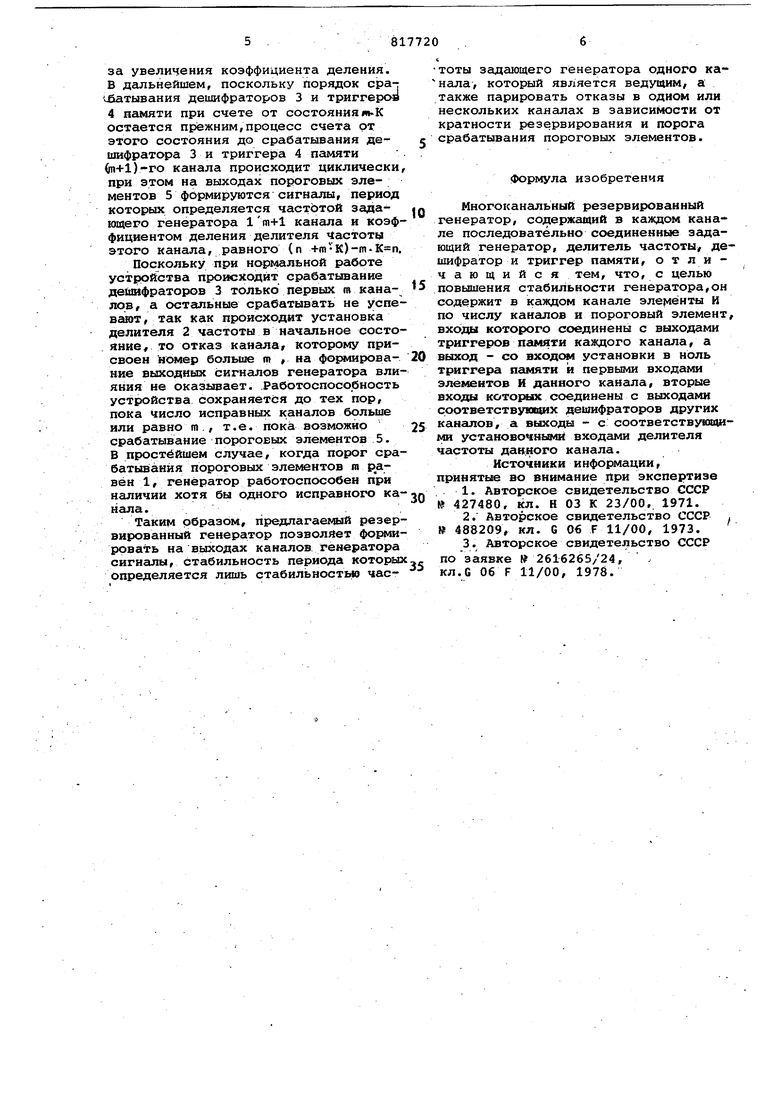

На чертеже изображена блок-схема предлагаемого резервированного генератора.

Генератор содержит в каждом канале последовательно соединенные задающий генератор 1, делитель 2 частоты, деашфратор 3, триггер 4 памяти и пороговый элемент 5, входы которого соединены с выходами триггеров 4 памяти каждого канала, а выход - со входом устансгвки и вдоль триггера 4 памяти данного канала и первыми входами элементов И б данного канала, вторые входы которых соединены с выходами соответствующих дешифраторов 3 каналов,а выходы - с соответствующими установочными входами делителя 2 частоты данного канала; Дешифраторы 3, каналов настроены на срабатывание при различных, состояниях Делителей 2 частоты, в зависимости от номера, присвоенного каналу. Дешифратор 3i-ro канала срабатывает при n+{i-l)«K состоянии делителя 2 частоты, где п - коэффициент деления частоты зада ющего генератора 1, а - целое число, конкретная величина которого определяется, исходя из стабильнсюти задаюашх генераторов 1 и требуемого времени переключения на резервный канал, при отказе вёдуи(его. Все делители 2 частоты имеют установочнью входы (по числу каналов резервирования для их установки в состояния О, К, 2К... {1-1)К...,(р-1)К.

Устройство работает следующим образом..

В каждом канале с задающих генераторов поступгиот снгнгшы на входы делителей 2 частоты, осуществляющие пересчет сигнешов. Когда на каком-либо из делителей 2 частоты устанавливается згшанное состояние, на выходе дешифратора 3 своего канала появляется .сигнал, запоминаемый на триггере 3 памяти. После включения питания сигНсшы на выходах дешифраторов 3 и, следовательно, на выходах триггеров 4 памяти появляются неупорядоченным образе. I. Сигнал на выходе пороговых элементов 5 (с порогом срабатывания,

равнь1м т)появится при срабатываний дешифратора 3 и триггера 4 памяти какого-то j-ro канала, сигнал с которого поступив на пороговые элементы т-ым по счету. При этом в каяадом канале ла входах одного из элементов И 6, выход которого соединен со входом установки делителя 2 частоты в состояние (j -1)К/ присутствуют сигналы с выхода порогового элемента 5 и выхода дешифратора 3 j-ro канала. На выходах элементов И б появляются сигналы, устанавливакяцие делители 2 частоты в состояние (j-l)K. Таким образом, все делители 2 частоты установлены в одно и то же состояние, от которого и продолжают счет выходных сигналов задающих генераторов 1, а триггеры 4 памяти - в нуль сигналами с выходов пороговых элементов 5. При исправности каналов, так как все дешифраторы 3 настроены на срабатывание при различных состояниях делителей частоты, порядок их срабатывания строго определенный. Первыми срабатывают дешифратор 3 и триггер 4 памяти первого канала, вторыми второго канала, т-ыми - т-го и т.д., т-ым по счету срабатывает дешифратор

3и триггер 4 памяти т-го канала.При этом происходит ср абатывание пороговых элементов 5 и появляются сигналы на выходах элементов И 6, соединенных со входами установки в.состояние (т-1)К делителей 2 частоты. Происходйт установка всех делителей 2 частоты в одно и то же состояние (m-l) К, от которого они продолжают счет выходных сигналов задающих генераторов 1, и обнуление триггеров.

4памяти сигналами с выходов пороговых элементов 5. Порядок срабатывания дешифраторов 3 и триггеров 4 памяти остается прежним и процесс от состояния (m-l)K до срабаты-вания дешифратора 3 и триггера 4 памяти т-го канала происходит циклически. При этом на выходах пороговых элементов 5 форишруются сигналы,, период которых зависит только от частЪты задающего генератора 1 т-го канала и коэффициента деления делителя

2частоты этого канала, равного

In + (m-J)K - (m-1)K « n При отказе канала, которому присвоен номер меньше Ш1И равный ш , т-ым по счету срабатывает дешифратор

3и триггер 4 памяти (т+1)-го канала и все делители 2 частоты установлены в начальное состояние тК. Т.ак как дешифратор 3 {m+l)-ro канала настроен на срабатывание при п + тК состоянии делителя 2 частоты, то коэффициент деления, йоторьм определяется величина первого формируемого после отказа, периода выходного сигнала, равен (п + т-К) - (т-1)К п+К, т.е. происходит однократное увеличение одного периода выходного сигнала изза увеличения коэффициента деления. В дальнейшем, поскольку порядок сраШатывания дешифраторов 3 и триггеров 4 памяти при счете от состояния остается прежним,процесс счета от этого состояния до срабатывания дешифратора 3 и триггера 4 памяти т+1)-го канала происходит циклически при этом на выходах пороговых элементов 5 формируются сигналы, период которых определяется частотой задающего генератора 1т+1 канала и коэф фициентом деления делителя частоты этого канала, равного (п )-m.. Поскольку при нормальной работе устройства происходит срабатывание дегиифраторов 3 только первых m каналов, а остальные срабатывать не успе вают , так как происходит установка делителя 2 частоты в начальное состояние « то отказ канала, которому присвоен номер больию m , на формирование выходных сигналов генератора влияния не оказывает. Работоспособность устройства сохраняется до тех пор, пока число исправных каналов больше или равно m., т.е. пока возможно срабатывание пороговых элементов 5. В простейшем случае, когда порог срабатывания пороговых элементов га рдвён 1, генератор работоспособен при наличии хотя бы одного исправного канала. Таким рбраэом, предлагаемый резервированный генератор позволяет форсшровать на выходах каналов генератора сигналы, стабильность периода которых определяется лишь стабильностыо частоты задающего генератора одного канала, который является ведущим, а также парировать отказы в одном или нескольких каналах в зависимости от кратности резервирования и порога срабатывания пороговых элементов. формула изобретения Многоканальный резервированный генератор, содержащий в каждом канале последовательно соединенные задающий генератор, делитель частоты, дешифратор и триггер памяти, отличающийся тем, что, с целью повышения стабильности генератора,он содержит в каждом канале элементы И по числу каналов и пороговый элемент, входы которого соединены с выходами триггеров памяти каждого канала, а выход - со входсж установки в ноль триггера памяти и первыми входами элементов И данного канала, вторые входы которых соединены с выходами cooTBeTCTByn ix дешифраторов других каналов, а выходы - с соответствующими установочными входами делителя частоты данного канала. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР К 427480, кл. Н 03 К 23/00, 1971. 2.Авторское свидетельство СССР , 488209, кл. 6 06 F 11/00, 1973. 3.Авторское свидетельство СССР по заявке 2616265/24, кл.С Об F 11/00, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный резервированный генератор | 1982 |

|

SU1072051A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

| Резервированный генератор синхроимпульсов | 1981 |

|

SU1008931A1 |

| Резервированный генератор импульсов | 1982 |

|

SU1102066A2 |

| Резервированнный генератор импульсов | 1978 |

|

SU866800A2 |

| Резервированное многоканальное устройство | 1981 |

|

SU1058098A1 |

| Резервированный делитель-формирователь | 1977 |

|

SU736382A1 |

| Многоканальное устройство синхронизации | 1987 |

|

SU1539759A1 |

| Резервированный генератор импульсов | 1978 |

|

SU743245A1 |

| Резервированный формирователь тактовых импульсов | 1977 |

|

SU632108A1 |

-J V

-Э

Авторы

Даты

1981-03-30—Публикация

1979-05-07—Подача