СП

W СО СЛ

СО

Изобретение относится к вычислительной технике и может быть использовано при создании системы синхронизации резервированных цифровых вычислительных устройство

Цель изобретения - повышение точности межканального фазирования.

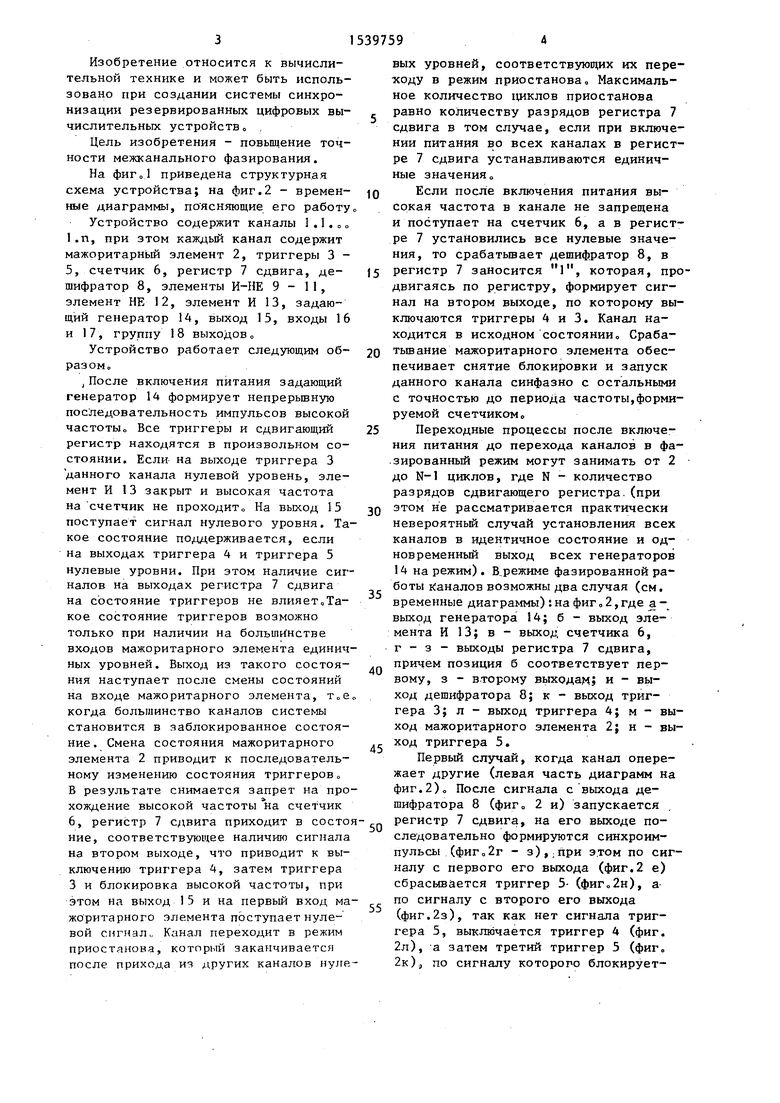

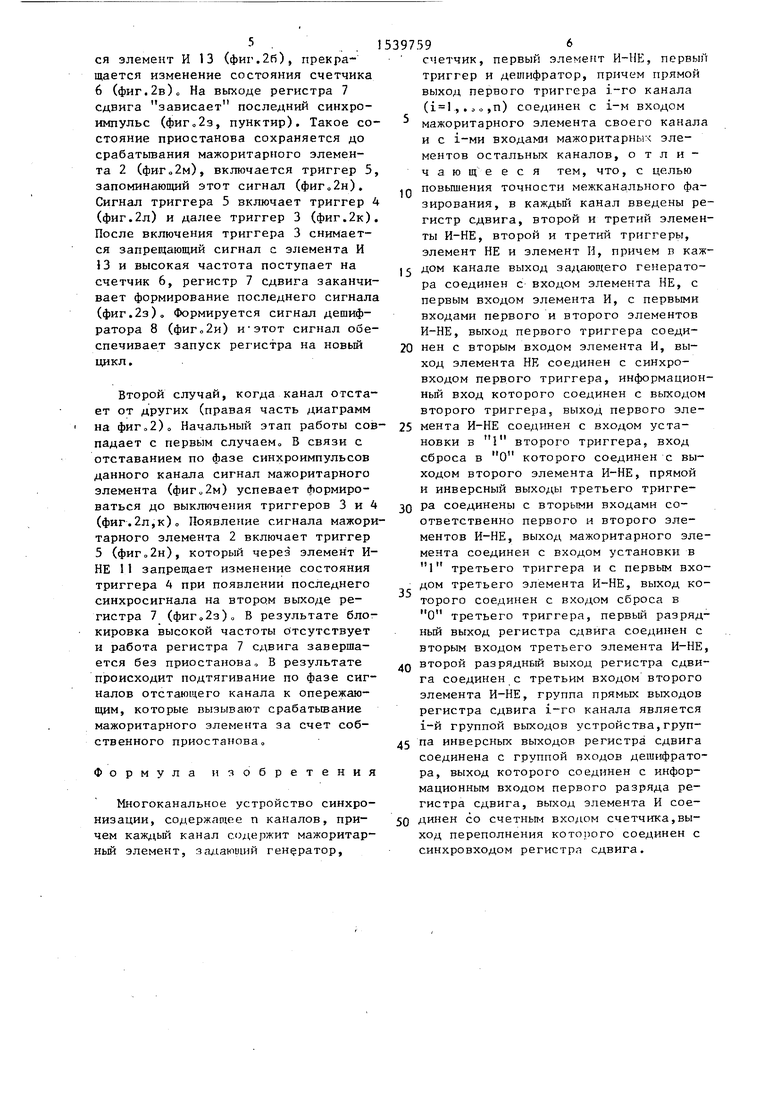

На фиг„1 приведена структурная схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу

Устройство содержит каналы 1 .1. „ 0 1,п, при этом каждый канал содержит мажоритарный элемент 2, триггеры 3 - 5, счетчик 6, регистр 7 сдвига, дешифратор 8, элементы И-НЕ 9-11, элемент НЕ 12, элемент И 13, задающий генератор 14, выход 15, входы 16 и 17, группу 18 выходов 0

Устройство работает следующим образом

, После включения питания задающий генератор 14 формирует непрерывную последовательность импульсов высокой частоты Все триггеры и сдвигающий регистр находятся в произвольном состоянии. Если на выходе триггера 3 данного канала нулевой уровень, элемент И 13 закрыт и высокая частота на счетчик не проходит На выход 15 поступает сигнал нулевого уровня. Такое состояние поддерживается, если на выходах триггера 4 и триггера 5 нулевые уровни. При этом наличие сигналов на выходах регистра 7 сдвига на состояние триггеров не влияет Та- кое состояние триггеров возможно только при наличии на большинстве входов мажоритарного элемента единичных уровней. Выход из такого состояния наступает после смены состояний на входе мажоритарного элемента, т„е когда большинство каналов системы становится в заблокированное состояние. Смена состояния мажоритарного элемента 2 приводит к последовательному изменению состояния триггеров В результате снимается запрет на прохождение высокой частоты на счетчик 6, регистр 7 сдвига приходит в состоние, соответствующее наличию сигнала на втором выходе, что приводит к выключению триггера 4, затем триггера 3 и блокировка высокой частоты, при этом на выход 15 и на первый вход мажоритарного элемента поступает нулевой сигнал. Канал переходит в режим приостанови, который заканчивается после прихода ия других каналов нуле

5

0

5

0

5

0

5

0

5

вых уровней, соответствующих их переходу в режим приостанова Максимальное количество циклов приостанова равно количеству разрядов регистра 7 сдвига в том случае, если при включении питания во всех каналах в регистре 7 сдвига устанавливаются единичные значения„

Если после включения питания высокая частота в канале не запрещена и поступает на счетчик 6, а в регистре 7 установились все нулевые значения, то срабатывает дешифратор 8, в регистр 7 заносится 1, которая, продвигаясь по регистру, формирует сигнал на втором выходе, по которому выключаются триггеры 4 и 3. Канал находится в исходном состоянии Срабатывание мажоритарного элемента обеспечивает снятие блокировки и запуск данного канала синфазно с остальными с точностью до периода частоты,формируемой счетчиком

Переходные процессы после включения питания до перехода каналов в фазированный режим могут занимать от 2 до N-1 циклов, где N - количество разрядов сдвигающего регистра (при этом не рассматривается практически невероятный случай установления всех каналов в идентичное состояние и одновременный выход всех генераторов 14 на режим). В режиме фазированной работы Каналов возможны два случая (см. временные диаграммы) : на фиг, 2, где a -t выход генератора 14; б - выход элемента И 13; в - выход счетчика 6, г - з - выходы регистра 7 сдвига, причем позиция б соответствует первому, з - второму выходам; и - выход дешифратора 8; к - выход триггера 3; л - выход триггера 4; м - выход мажоритарного элемента 2; н - выход триггера 5.

Первый случай, когда канал опережает другие (левая часть диаграмм на фиг.2)„ После сигнала с выхода дешифратора 8 (фиго 2 и) запускается регистр 7 сдвига, на его выходе последовательно формируются синхроимпульсы (фиг„2г - з),.при этом по сигналу с первого его выхода (фиг.2 е) сбрасывается триггер 5- (), а по сигналу с второго его выхода (фиг.2з), так как нет сигнала триггера 5, выключается триггер 4 (фиг. 2л), а затем третий триггер 5 (фиг. 2к)л по сигналу которого блокируется элемент И 13 (фиг.2б), прекращается изменение состояния счетчика 6 (фиг.2в)о На выходе регистра 7 сдвига зависает последний синхроимпульс (фиг„2э, пунктир). Такое состояние приостанова сохраняется до срабатывания мажоритарного элемента 2 (фиг„2м), включается триггер 5, запоминающий этот сигнал (фиг02н). Сигнал триггера 5 включает триггер 4 (фиг.2л) и далее триггер 3 (фиг.2к). После включения триггера 3 снимается запрещающий сигнал с элемента И J3 и высокая частота поступает на счетчик 6, регистр 7 сдвига заканчивает формирование последнего сигнала (фиг.2з)„ Формируется сигнал дешифратора 8 (фиг„2и) и этот сигнал обеспечивает запуск регистра на новый цикл.

Второй случай, когда канал отстает от других (правая часть диаграмм на фиг о 2)о Начальный этап работы совпадает с первым случаем В связи с отставанием по фазе синхроимпульсов данного канала сигнал мажоритарного элемента (фиг„2м) успевает Нормироваться до выключения триггеров 3 и 4 (фиг.2л,к)о Появление сигнала мажоритарного элемента 2 включает триггер 5 (фиг„2н), который через элемент PI- HE 11 запрещает изменение состояния триггера 4 при появлении последнего синхросигнала на втором выходе регистра 7 (фиг,2з)о В результате блокировка высокой частоты отсутствует и работа регистра 7 сдвига завершается без приостанова, В результате происходит подтягивание по фазе сигналов отстающего канала к опережающим, которые вызывают срабатывание мажоритарного элемента за счет собственного приостановао

Формула изобретения

Многоканальное устройство синхронизации, содержащее п каналов, причем каждый канал содержит мажоритарный элемент, задающий генератор,

5397596

счетчик, первый элемент И-НЕ, первый триггер и дешифратор, причем прямой выход первого триггера i-ro канала (,.о,п) соединен с i-м входом мажоритарного элемента своего канала и с 1-ми входами мажоритарны элементов остальных каналов, отличающееся тем, что, с целью повышения точности межканального фа15

20

30

10

зирования, в каждый канал введены регистр сдвига, второй и третий элементы И-НЕ, второй и третий триггеры, элемент НЕ и элемент И, причем в каждом канале выход задающего генератора соединен с входом элемента НЕ, с первым входом элемента И, с первыми входами первого и второго элементов И-НЕ, выход первого триггера соединен с вторым входом элемента И, выход элемента НЕ соединен с синхро- входом первого триггера, информационный вход которого соединен с выходом второго триггера, выход первого эле25 мента И-НЕ соединен с входом установки в 1 второго триггера, вход сброса в О которого соединен с выходом второго элемента И-НЕ, прямой и инверсный выходы третьего триггера соединены с вторыми входами соответственно первого и второго элементов И-НЕ, выход мажоритарного элемента соединен с входом установки в 1 третьего триггера и с первым входом третьего элемента И-НЕ, выход которого соединен с входом сброса в О третьего триггера, первый разрядный выход регистра сдвига соединен с вторым входом третьего элемента И-НЕ, второй разрядный выход регистра сдвига соединен с третьим входом второго элемента И-НЕ, группа прямых выходов регистра сдвига 1-го канала является i-й группой выходов устройства,группа инверсных выходов регистра сдвига соединена с группой входов дешифратора, выход которого соединен с информационным входом первого разряда регистра сдвига, выход элемента И соединен со счетным входом счетчика,выход переполнения которого соединен с синхровходом регистра сдвига.

35

40

45

50

J 1ПШ1Л1МПП1ШШШ11ШШ11Ш11Ш

r iniUUinim J

1ЛЛМЛ..ЛЛЛПЯШШШ

г ппП

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство синхронизации | 1988 |

|

SU1642473A1 |

| Устройство для формирования импульсов | 1983 |

|

SU1223218A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК ДЛЯ ФОРМИРОВАНИЯ МЕТОК ВРЕМЕНИ | 2008 |

|

RU2379829C1 |

| Резервированное трехканальное устройство приоритета | 1982 |

|

SU1091369A1 |

| Резервированный делитель частоты | 1983 |

|

SU1163473A1 |

| Устройство для приема информации | 1988 |

|

SU1552216A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Устройство для синхронизации сигналов | 1980 |

|

SU868735A2 |

Изобретение относится к вычислительной технике и может быть использовано при создании систем синхронизации резервированных цифровых вычислительных устройств. Отличительной особенностью устройства является то, что в нем не мажоритируются выходные сигналы каналов, что исключает внесение дополнительной ошибки фазирования из-за несинхронности срабатывания мажоритарных элементов в разных каналах. Целью изобретения является повышение точности межканального фазирования. Поставленная цель достигается за счет введения в каждый канал регистра 7 сдвига, элементов И-НЕ 9, 11, элемента НЕ 12, элемента И 13. 2 ил.

| Устройство для синхронизации сигналов | 1978 |

|

SU860042A1 |

| f | |||

Авторы

Даты

1990-01-30—Публикация

1987-07-06—Подача