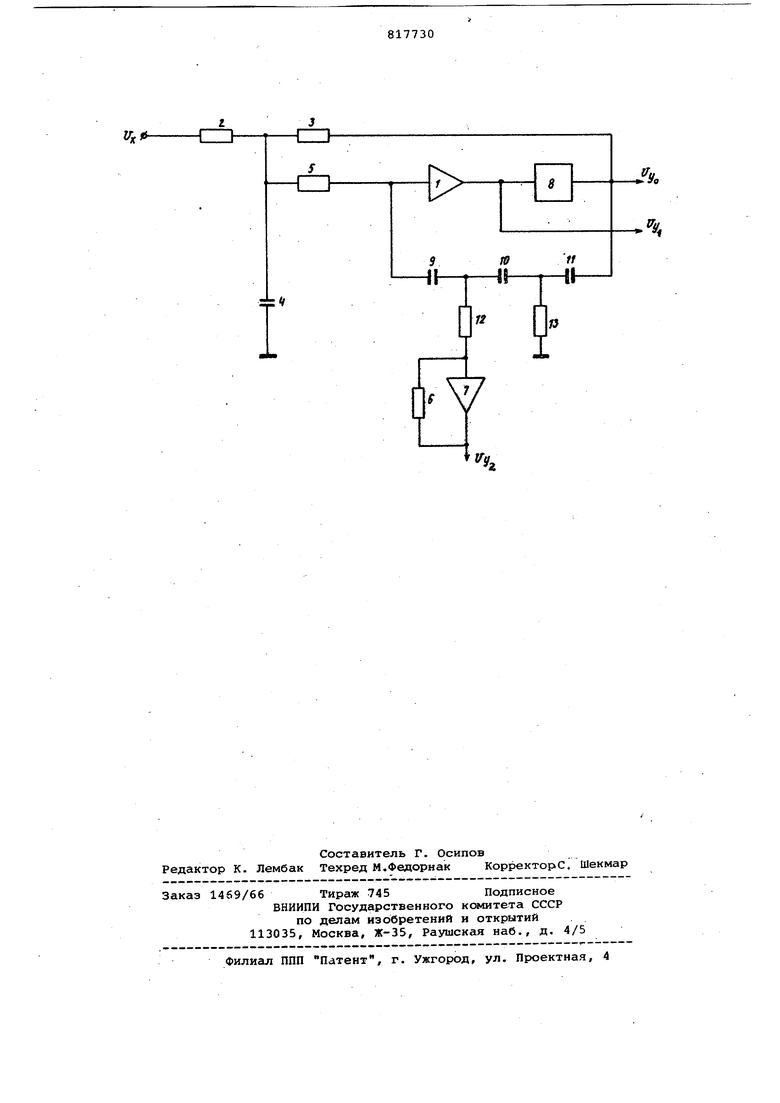

/ Изобретение относится к аналоговой вычнслительной технике н может OtKb использовано для совместного по лучения сглемсенного сигнала н од ной нли двух его производных. Известен операционный усилитель, вхоя через первый масштабирующий резистор соеди н со входом устройства, а цеПь .обратной связи об раэована вторьзм масштабирующим резне тором н шунтирующей его цепочкой из 3-х последовательно соединенных зарядных конденсаторов, обтие обкладки которых через разрядаше реэисторы подкдшчены ко входам операционных усилителей, охваченных резнстивtKJti обратной связью 13« Однако в данном устройстве невысокая степень сглаживания (крутизна спада логарифладческой алшлитудно-час тотной характеристики (ЛА%С) не превышает 20 дБ/декаду) и наличие системафических выход1«ых о&тоок дифференцирования, поскольку в каналах образования производных используются пассивные днфференцирукздие цепи. Наиболе.е близким к предлагаетлому является днфференцирующе-сг; лживаюцее устройство, содержащее операцион ные усилители,интегрирукнцую входную КС-цепь, резисторы и конденсаторы Г23. Недостаток устройства - налнчие недемпфированного дифференцирующего звена в контуре обратной , обуславливаюцего повышенную чувствительность к псявехам, а также сложность устройства. Цель изобретения - повышенне помехозащищенности и упрощение устройства,г Поставленная цель достигается тем, что дифференцирующе-сглаживающее устройство, содержащее первый операцнонщфй усилитель, вход которого связан с входе устройства через первой н второй последовательно соединенные масштабнрующие резисторы, общий, вывод которых соединен с шиной нулевого потенциала через ннтегрирующий конденсатор, и второй операцион{шй усилитель, в цепь обратной связи которого включен третий масштабирующий резистор, вход второго операционного уснлителя. через входной резистор соедннен с выводом двух последовательно соединенных зарядных конденсаторов, свободная обкладка первого из них подключена к входу первого операционного усилителя, содержит интегратор, третий зарядный конденсатор, разрядный резистор Si четвертый масштабирующий р зистор, соединяющий выход интеграто ра с общим выводом первого и второг масштабирующих резисторов, выход пе вого операционного усилителя соедин с входом интегратора, свободная обкладка второго зарядного конденсате ра связана с шиной нулевого потенциала через разрядный резистор, а с выходом интегратора - через третий зарядный конденсатор, выходы интегратора и операционных усилителей яв ляются соответствующими выходами устройства. На чертеже представлена схема предлагаемого устройства. Устройство содержит операционный усилитель 1, масштабирующие резисторы 2 и 3, интегрирующий конден сатор 4, масштабирующие резисторы 5 и 6, операционный усилитель 7, интегратор 8, зарядные конденсаторы 9-11, входной резистор 12, разрядный резистор 13. Устройство работает следующим образом. Структура устройства обеспечивает равенство коэффициентов при один ковых степенях полиномов числителя и знаменателя 1+а| p+agp «,0 Р)R 1+а p+ajp +agpi+a p . .«;:cS::gc° Aq.( P ,,15,зТг ,p4ajpata pi a где p - аргумент преобразования Лапласа; - передаточная функция интегратора 8. а, Rn Ко +С„ )+R,2 ( ); ,2 RIJ (С,о С СрС +С9 С о ) ; (1+ + ); Ср,.нпIN/II . К Г чЧо 41 а с €9 Су, RjRjRfa s Сопротивления R резисторов и емкости С конденсаторов индексированы согласно обозначениям в схеме. Структурная компенсация обесп ечи вает отсутствие соответствующих составляющих систематической ошибки на выходах устройства. Интегратор 8 может быть выполнен на стандартном инвертирующем операционном усилителе, шунтированном конденсатором С. Учитывая инверсию знака в интеграторе, с целью сохранения, отрицательной обратной связи в качестве усилителя 1 используется стандартный дифференциальный операционный усилитель, инвертирующий вход которого соединяется с шиной нулевого потенциала, а неинвертирующий вход является входом усилителя. Технико-экономический эффект от использования предлагаемого устройства обусловлен улучшением фильтрующих свойств при одновременной экономии элементной базы. Формула изобретения Дифференцирующе-сглаживающее устройство, содержащее первый операционный усилитель, вход которого связан с входом устройства через первый и второй последовательно соединенные масштабирующие резисторы, общий вывод которых соединен с шиной нулевого потенциала через интегрирующий конденсатор, и второй операционный усилитель, в цепь обратной связи которого включен третий масштабирующий резистор, вход второго операционного усилителя через взводной резистор соединен с общим выводом двух последовательно соединенных зарядных конденсаторов, свободная обкладка первого из них подключена к входу первого операционного усилителя, отличающееся тем, что , с целью повышения помехозащищенности и упрощения, устройство содержит интегратор, третий зарядный конденсатор, разрядный резистор и четвертый масштабирующий резистор, соединяющий выход интегратора с общим выводом первого и второго масштабирующих резисторов, выход первого операционного усилителя соединен с входом интегратора, свободная обкладка второго зарядного конденсатора связана с шиной нулевого потенциала через разрядный резистор, а с выходом интегратора - через третий зарядный конденсатор, выходы интегратора и операционных усилителей являются соответствующими выходами устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 552618, кл. G Об G 7/18, 1975. 2.Автоматизация проектирования. Труды МЭИ. Вып. 343, 1977, с.80-84 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговый решающий узел | 1979 |

|

SU849244A1 |

| Операционный усилитель | 1983 |

|

SU1156093A1 |

| Время-импульсное вычислительное устройство | 1983 |

|

SU1123038A1 |

| Интегрирующий реверсивный привод | 1979 |

|

SU811287A1 |

| Множительно-делительное устройство широтно-модулированных сигналов | 1983 |

|

SU1095196A1 |

| Релейный преобразователь сигналов | 1975 |

|

SU547787A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Операционный усилитель с компенсацией дрейфа нулевого уровня | 1977 |

|

SU739549A1 |

| Операционный усилитель с периодической компенсацией смещения нуля | 1982 |

|

SU1024938A1 |

Авторы

Даты

1981-03-30—Публикация

1979-05-29—Подача