(54) УСТЮЙСТВО ДЛЯ ЗАДЕРЖКИ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1980 |

|

SU921067A1 |

| Устройство для задержки импульсов | 1978 |

|

SU739722A1 |

| Двоично-десятичный счетчик вКОдЕ 8-4-2-1 | 1979 |

|

SU849498A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| Д- @ триггер | 1982 |

|

SU1022299A1 |

| Устройство для выделения и вычитания первого импульса из последовательности импульсов | 1984 |

|

SU1223228A1 |

| Устройство пересчета на три | 1980 |

|

SU869067A2 |

| Устройство для выделения одиночного импульса | 1989 |

|

SU1621147A1 |

| Селектор импульсов по длительности | 1979 |

|

SU805485A1 |

| Устройство для выделения первогоиМпульСА и ВычиТАНия пЕРВОгОиМпульСА из пОСлЕдОВАТЕльНОСТииМпульСОВ | 1979 |

|

SU817708A1 |

I

Изобретение относится к автоматике и вычислительной технике и может быть применено в вычислительных устройствах различного назначения, где необходимо получение задержк последовательностей импульсов.

Известно устройство для задержки импульсов, содержащее входную шину, которая подключена ко входу первого элемента задержки и через инвертор ко входу второго элемента задержки, триггер на двух ; элементах И-НЕ, единичный вход триггера соединен с выходом второго элемента задержки через последователно соединенные дифференцирующую цепочку и инвертор, а нулевой вход триггера соединен с выходом первого элемента задержки через последовательно соединенные дифференцирующую цепочку и инвертор 1.

Наличие в устройстве дифференцирующих цепей, приводит к низкой помехозащищенности, а также усложняет гибридно-пленочную технологию изготовления:

Известно устройство для задержки импульсов, содержащее инвертор, два триггера, два элемента И-НЕ, причем единичный выход первого триггера подключен к первому входу пер вого элемента И-НЕ, выход которого -соединен нулевым входом второго триггера, а единичный выход второго триггера подключен к выходу второго элемента И-НЕ, первый вход которого соединен с нулевым выходом первого триггера, .инвертор соединен с входной шиной, а выход инвертора подключен к первому элементу задержки. Кроме того, содержит второй элемент задержки, вход которого соеди0нен с входной ишной, а выход подключен к нулевому входу первого триггера, единичный вход которого подключен к выходу первого элемента задержки 2.

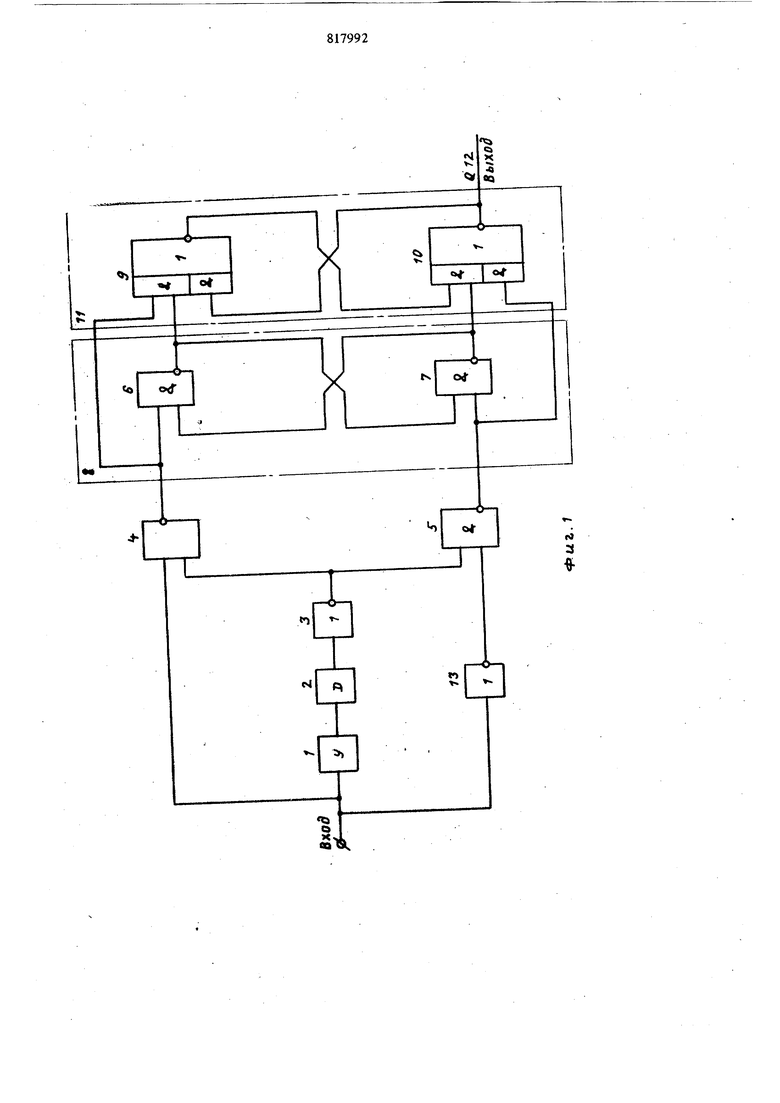

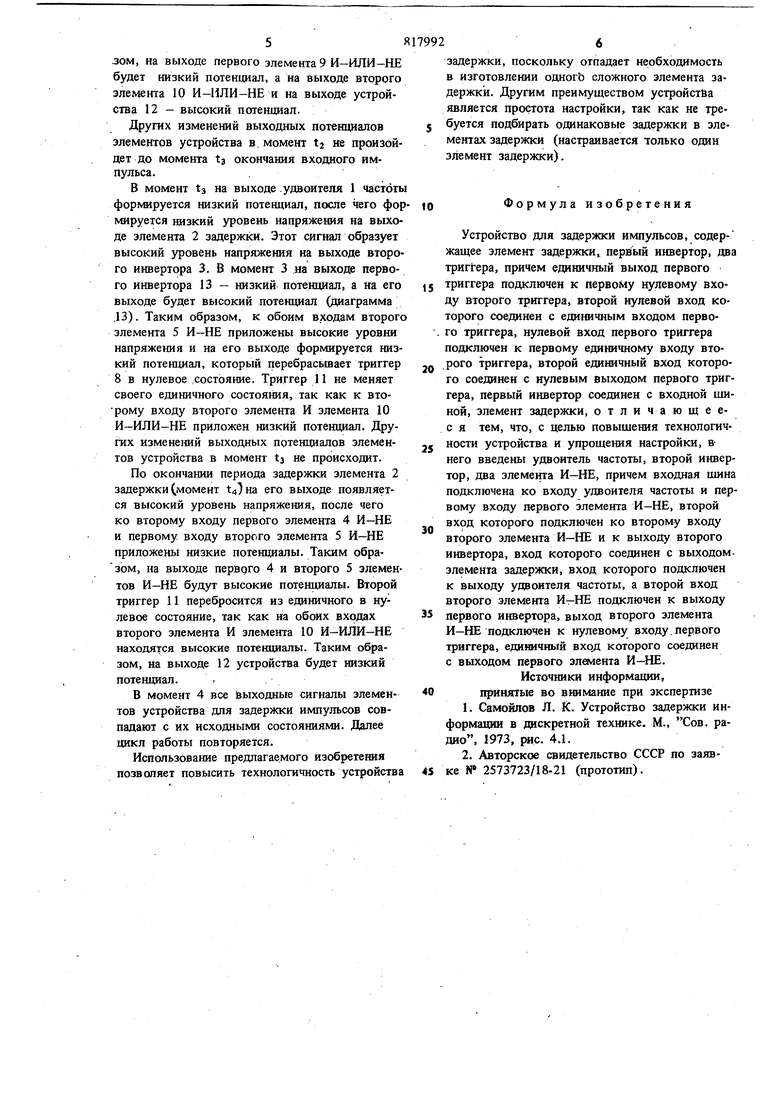

Наряду с положительными качествами (маsлым числом элементов, достаточно широкими функциональными возможностями, высокой помехозащищенностью) это у лройство имеет серьезные недостатки. Оно содержит два элемента задержки, которые могут бь1ть выполнены в виде одновибраТОра и являются нетехнологичными для гибридно-пленочной технологии, так как содержат конденсаторы. Другим недостатком известного технического ре3шения Шляется сложная настройка устройства так как для одинаковой задержки переднего и заднего фронтов входного сигнала требуется вьтолнить условие 11зад. ззад. (Д 1)зад. - время задернски первого элемента задержки, а ti3aA, время второго элемента задержки). Шстройка первото и второго элемента задержки на одинаковое время задержки является очень трудоемкой операцией: она занимает 83% времени настройки всего устройства для задержки импульсов. Цель изобретения - повышение технологичности устройства и упрощение его настройки. Поставленная цель достигается тем, что в устройство для задержки импульсов, содержащее элемент задержки, первый инвертор, два триггера, причем единичный выход первого триггера подключен к первому нулевому входу второго триггера, второй нулевой вход которого соеданен с единичным входом первого триггера, нулевой вход первого триггера подключен к первому единичному входу второго триггера, второй единичный вход которого соединен с нулевым выяодом первого триггера, первый инвертор соединен с входной шиной, элемент задержки, введены удвоитель частоты, второй инвертор, два элемента И-НЕ причем входная шина подключена ко входу ; удвоителя частоты и первому входу первого элемента И-НЕ, второй вход которого подключен ко второму входу второго элемента И-НЕ и к выходу второго инвертора, вход к торого соединен с выходом элемента задержки, вход которого подключен к выходу удво ителя частоты, а второй вход второго элемента И-НЕ подключен к выходу первого инвертора, выход второго элемента И-НЕ подкл чен к нулевому входу первого триггера, -единичный вход которого соединен с выходом первого элемента И-НЕ. На фиг. 1 представлена функциональная схе ма устройства для задержки импульсов; на фиг. 2 - временные диаграммы его работы. Устройство для задержки импульсов содержит удвоитель 1 частоты, выход которого подключен к элементу 2 задержки и через второй инвертор 3. к первому элементу 4 И-НЕ и второму элементу 5 И-НЕ, элементы 6 И-НЕ и 7 И-НЕ образуют триггер 8, элементы 9 и 10 И-ИЛИ-НЕ образуют триггер 11, выход которого соединен с выходом 12 устройства для задержки импульсов, первый инвертор 13. Работа устройства осуществляется следующим образом. Перед подачей положительных импульсов н вход устройства на выходе удвоителя 1 частоты присутствуют единичный высокий потен циал ( фиг. 2, диаграмма 1). На выходе .элемента 2 задержки присутствут высокий уровень напряжения, а на выходе торого инвертора 3 - низкий потенциал (диаграммы 2 и 3). Низкий потенциал с выода второго инвертора 3 приводит к образоа1шю высоких потенциалов на выходах перого 4 и второго 5 элементов -И-НЕ (диаграмы 4 и 5). Допустим, что перед подачей импульсов оба триггера находятся в состоянии О. При этом на выходе элемента 6 И-НЕ находится шзкий потенциал (диаграмма 6), а на выходе элемента 7 И-НЕ находится высокий потенциал (диаграмма 7}. На обоих нулевых входах первого элемента И схемы 9 И-ИЛИ-НЕ (диаграмма 9) присутствуют высокие потенциалы, следовательно, на его выходе будет низкий потенциал, а на выходе элемента 10 И-ИЛИ-НЕ (диаграмма 10) будет высокий потенциал, так как на втором единичном входе первого элемента И элемента 10 И-ИЛИ-НЕнизкий потенциал и на входе второго элемента И элемента 10 И-ИЛИ-НЕ - низкий потенциал. Таким образом, триггер 11 в нулевом состоянии. Высокий потенциал с выхода элемента 10 И-ИЛИ-НЕ поступает на вход второго элемента И элемента 9 И-ИЛИ-НЕ и подтверждает низкий потенциал на выходе 12 устройства. В момент tj появления первого входного импульса на выходе удвоителя 1 частоты формируется низкий потенциал, после чего формируется низкий уровень напряжения на вь1ходе элемента 2 задержки. Этот-сигнал образует высокий уровень напряжения на выходе второго инвертора 3, после этого к обоим входам элемента 4 И-НЕ приложены высокие уровни напряжения и на его выходе формируется низкий потенциал, который перебрасьшает триггер 8 в единичное состояние. На выходе элемента 6 И-НЕ - высокий потенциал, а на выходе элемента 7 И-НЕ - низкий потенциал. Триггер 11 не меняет своего нулевого состояния, так как к первому входу первого элемента И элемента 9 И-ИЛИг-НЕ приложен низкий потенциал. Других изменений выходных потенциалов, элементов устройства в момент t| не происходит. По окончании периода задержки элемента 2 задержки( момент его выходе появляется высокий уровень напряжения, после чего к второму входу первого элемента 4 И-НЕ и к первому входу второго элемента 5 И-НЕ приложены низкие п.отенциалы с инвертора 3, управляемого схемой задержания. Таким образом, на выходе первого 4 и второго 5 элементов И-НЕ будут высокие потенциалы. Второй триггер 11 перебросится из нулевого в единичное состояние, так как на обсях входах первого элемента И элемента 9 И-ИЛИ-НЕ находится высокий потенциалы. Таким обра- i .зом, на выходе первого элемента 9 И-ИЛИ-НЕ будет низкий потенциал, а на выходе второго элемента 10 И-ИЛИ-НЕ и на выходе устройства 12 - высокий потенциал. Других изменений выходных потенциалов элементов устройства в момент tj не произойдет до момента ta окончания входного импульса.. В момент ts на выходе удвоителя 1 частоты формируется низкий потенциал, после чего фор мируется низкий уровень напряжения на выходе элемента 2 задержки. Этот сигнал образует высокий уровень напряжения на выходе второ го инвертора 3. В момент 3 на выходе первого инвертора 13 - низкий потенциал, а на его выходе будет высокий потенциал (диаграмма .13). Таким образом, к обоим входам второг элемента 5 И-НЕ приложены высокие уровни напряжения и на его выходе формируется низкий потенциал, который перебрасьтает триггер 8 в нулевое .состояние. Триггер 11 не меняет своего единичного состояния, так как к второму входу второго элемента И элемента 10 И-ИЛИ-НЕ приложен низкий потенциал. Других изменений выходных потенциалов элементов устройства в момент tj не происходит. По окончании периода задержки элемента 2 задержки (момент t4)Ha его выходе появляется высокий уровень напряжения, после чего ко второму входу первого элемента 4 И-НЕ и первому входу второго элемента 5 И-НЕ приложены низкие потенциалы. Таким образом, на выходе первдго 4 и второго 5 элементов И-НЕ будут высокие потенциалы. Второй триггер 11 перебросится из единичного в нулевое состояние, так как на обоих входах второго элемента И элемента 10 И-ИЛИ-НЕ находятся высокие потенциалы. Таким образом, на выходе 12 устройства будет низкий потенциал. В момент 4 все выходные сигналы элементов устройства для задержки импульсов совпадают с их исходными состояниями. Далее цикл работы повторяется. Использование предлагаемого изобретения позволяет повысить технологичность устройства 6 задержки, поскольку отпадает необходимость в изготовлении одногЬ сложного элемента задержки. Другим преимуществом устройстйа является простота настройки, так как не требуется подбирать одинаковые задержки в элементах задержки (настраивается только один элемент задержки). Формула изобретения Устройство для задержки импульсов, содержащее элемент задержки, инвертор, два триггера, причем единичный выход первого триггера подключен к первому нулевому входу второго триггера, второй нулевой вход которого соединен с единичным входом первого триггера, нулевой вход первого триггера подключен к первому единичному входу второго триггера, второй единичный вход которого соединен с нулевым выходом первого триггера, первый инвертор соединен с входной шиной, элемент задержки, отличающеес я тем, что, с целью повышения технологичности устройства и упрощения настройки, в него введены удвоитель частоты, второй инвертор, два элемента , причем входная шина подключена ко входу удвоителя частоты и первому входу первого элемента И-НЕ, второй вход которого подключен ко второму входу второго элемента И-НЕ и к выходу второго инвертора, вход которого соединен с выходомзлемента задержки, вход которого подключен к выходу удвоителя частоты, а второй вход второго элемента И-НЕ подключен к выходу первого инвертора, выход второго элемента И-НЕ подключен к нулевому входу первого триггера, единичный вход которого соединен с выходом первого элемента И-НЕ. Источники информации, принятые во внимание при экспертизе 1.Самойлов Л. К. Устройство задержки информации в даскретной технике. М., Сов. радио, 1973, рис. 4.1. 2.Авторское свидетельство СССР по заявке N 2573723/18-21 (прототип).

I о

ггт

о о

::;

«t

1

3

1 с

3 с

п

п г

о

9 9D J

1Г

55

§

(о tx

Авторы

Даты

1981-03-30—Публикация

1979-05-21—Подача