1

Изобретение относится к автоматике и вычислительной технике, может быть применено, в частности, в электронных устройствах различного назначения, где необходимо получение задержки последовательн()стей импульсов.

Известно устройство для задержки импульсов, содержащее входную шину, резисторноемкостное интегрирующее звено, связанное со входами двух сигнализаторов предельного значения с различными уровнями срабатывания, один логический одновходовой элемент, вход которого соединен с выходом одного из сигнализаторов предельного значения, а выход - с одним из входов трехвходового логического элемента; два других его входа соединены соответственно с выходом второго сигнализатора предельного значения и со входной шиной 1.

Устройство вырабатывает только импульсы фиксированной длительности, идущие с частотой не свыше некоторой :5аданной, и поэтому его невозможно применять для задержки произвольных импульсных последовательностей. |Это ограничивает функциональные возможности устройства и область его применения. Кроме того, применение сигнализаторов предельного значения усложняет схему.

Известно устройство для задержки импульсов, содержащее входную шину, которая подключена ко входу первого элемента задержки, и через инвертор - к входу второго, асинхронный RS-триггер на двух элементах И-НЕ 2.

Наряду с положительными качествами 10малое число элементов, достаточно широкие функщюнальные возможности и область применения, простота связей между элементами, это устройство для задержки импульсов имеет серьезные недостатки: содержит дифферен15цирующие цепи, что приводит к низкой помехозащищенности, а также усложняет технологию изготовления в гибридно-пленочном исполнении.

Цель изобретения - повышение надежности и технологичности устройства.

20

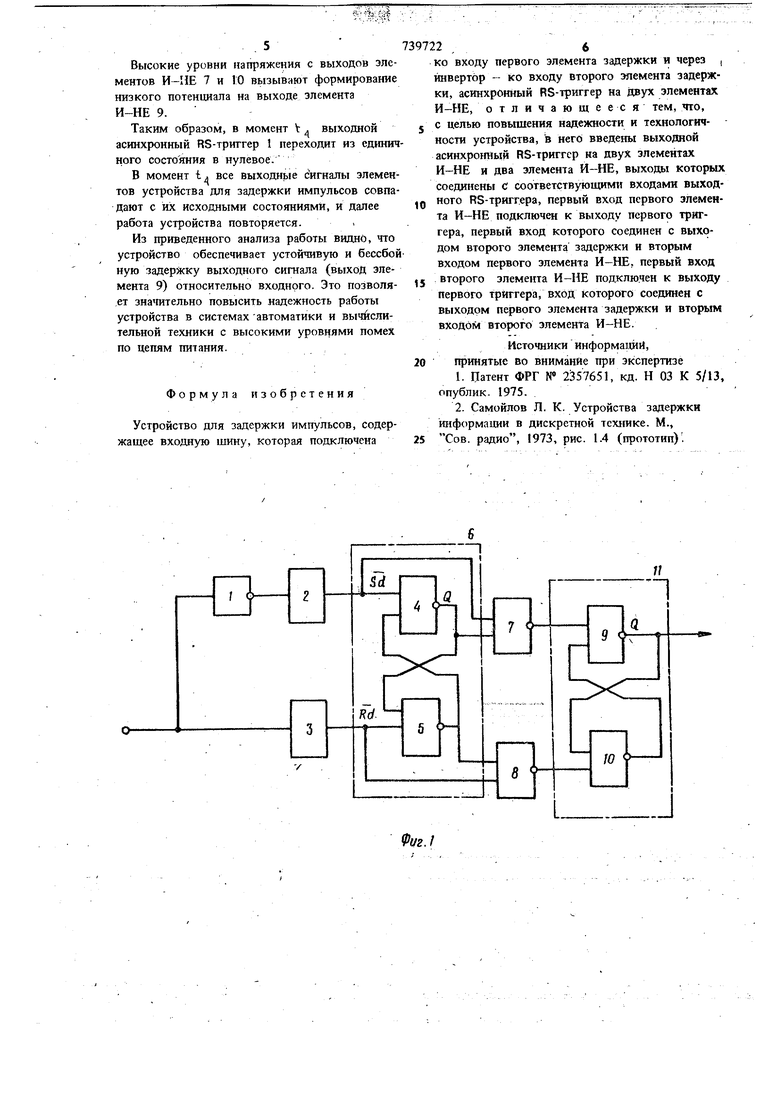

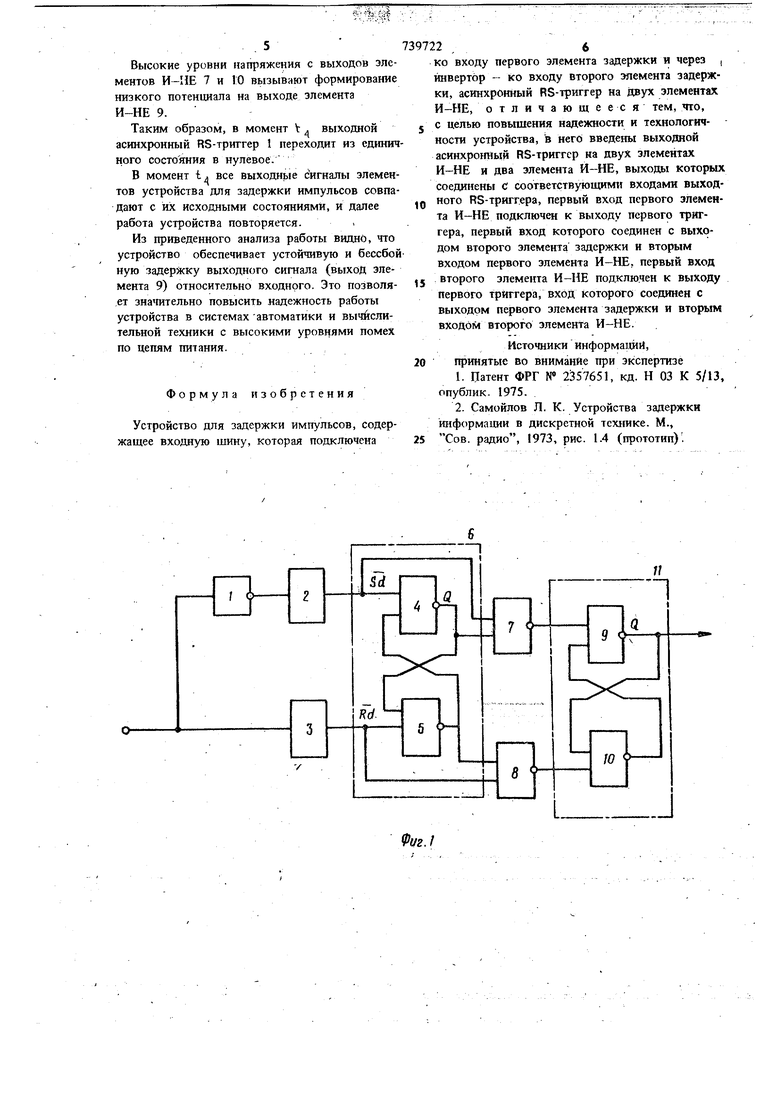

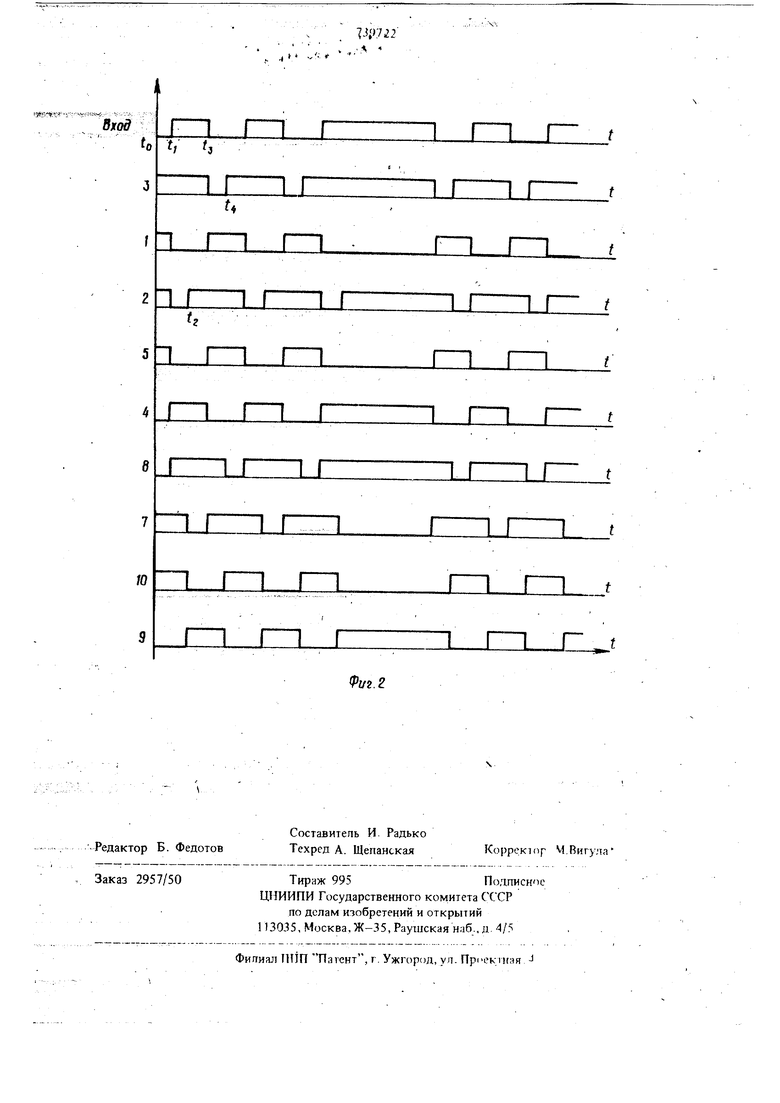

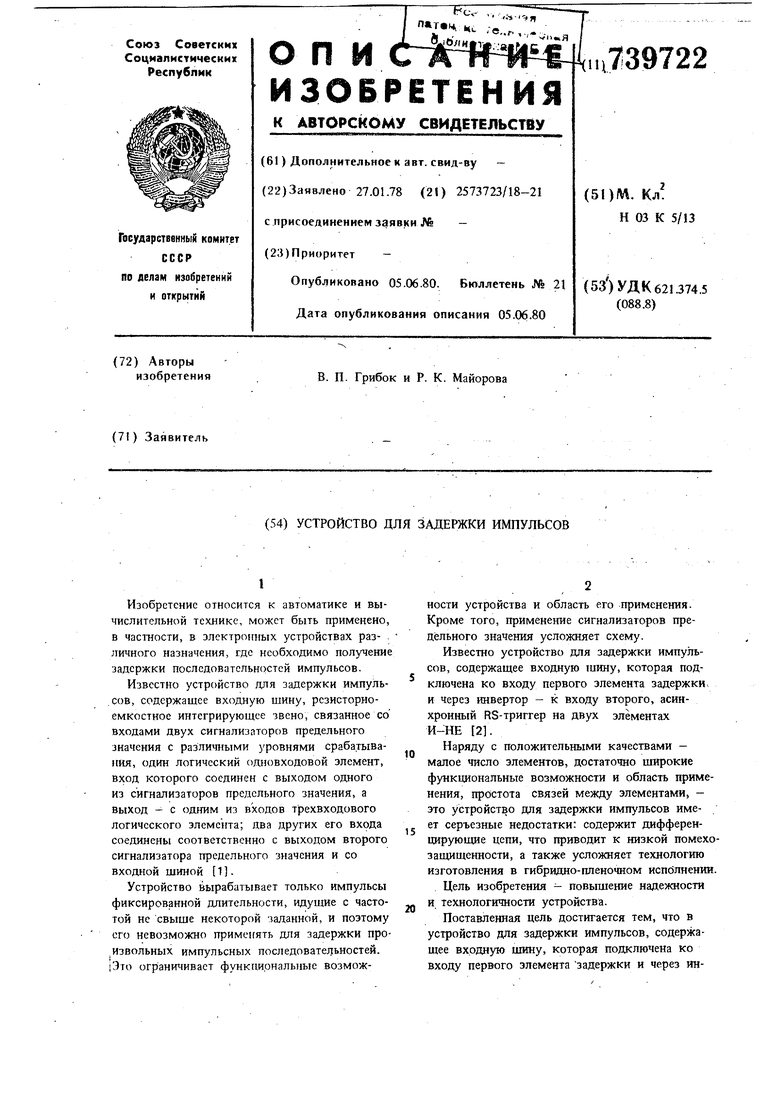

Поставленная цель достигается тем, что в устройство для задержки импульсов, содержащее входную шину, которая подключена ко входу первого элемента задержки и через инвертор - ко/входу второго элемента задержки, асинхронный RS-триггер на двух элементах И-НЕ, введены выходной асинхронный RS-триг гер и два элемента И-НБ, выходы которых соединень с соответствующими входами выходного RS-триггера, первый вход первого элемента И-НЕ подключен к выходу первого триггера, первый вход которого соединен с. выходом второю элемента задержки и вторым входом первого элемента И-НЕ, первый вход второго элемента И-ЙЕ подключен к выходу первого триггера,вход которого соединен с выходом первого элемента задержки и вторым входом второго элемента И-НЕ. На фиг. 1 представлена функдиональная схема предлагаемого устройства для задержки импульсов; на фи1. 2 - временные диаграммы его работы. Устройство для задержки импульсов содержит входную шину, соединенную со входом инвертора 1, выход кс1торого подключен Ко входу элемента задержки 2; элемент задержки 3, элементы И-НЕ 4 и 5, образующие асинхрон|{ый RS-триггер 6, выход Q и вход Sd которого соединены со входами первого элемента И-НЕ 7; второй элемент И-НЕ 8; элементы И-НЕ 9 и 10, образующие выходиой асинхронный RS-,TpHrrep 11, выход Q которого соединен с выходом устройства для задер5кки импульсов. Работает предлагаемое устройство следующим образом. Перед подачейположительньтх импульсов на вход устройства на выходе инвертора 1 (диаграмма 1 на фиг. 2) присутствует единичный высокий потенциал. На выходах злементов задержек 2 и 3 (диа граммы 2 и 3, фиг. 2) присутствуют высокие уровни нанряжения. Элементы задержки могут быть выполнены в виде одновибратора. Допустим, что перед -подачей импульсов оба триггера находятся в состоянии О. При этом на выходе элемента И-НЕ 4 находится низкий уровень напряжения (диаграмма 4, фиг. 2 а на выходе элемента И-НЕ 5 - высокий (диаграмма 5, фиг. 2), что означает состояние О асинхронного триггера 6. Низкий потенциал на выходе 4 приводит к появлению высокого уровня напряжения на выходе первого элемента И-НЕ 7 (диаграмма 7,фиг. 2). На обоих входах второго элемента И-НЕ 8 присутствую единичные сигналы, и на его выходе образуетс нулевой сигнал (диаграмма 8, фиг. 2). На выходах элементов И-НЕ 9 и 10, образующих выходной асинхронный RS-триггер И перед подачей импульсов присутствуют соответственно низкий и высокий уровни напряжения (диаграммы 9 и 10, фиг. 2), что означает состояние О триггера П. 24 В момент t появления первого входного импульса на выходе инвертора 1 формируется низкий потенциал, после чего формируется низкий уровень напряжения на вь1ходе элемента задержки 2. Этот сигнал сохраняет высокий уровень напряжения на выходе первого элемента И-НЕ 7 и устанавливает высокий потенциал на выходе И--НЕ 4. После этого к обоим входам элемента И-НЕ 5 прикладываются высокие уровни напряжения, и на его выходе формируется низкий потенциал. Это означает переброс асинхронно RS-триггера 6 из нулевого в единичное состояние. Низкий потенциал с выхода элемента И-НЕ 5 приводит к появлению высокого сигнала на выходе элемента И-НЕ 8. Других изменений выходных потенциалов элементов устройства в момент t не происходит. По окончании периода задержки элемента задержки 2 (момент t ) на его выходе появляется высокий уровень напряжения, после чего к обоим входам элемента И --НЕ 7 прикладываются высокие уровни напряжения. Это приводит к формированию нулевого потенциала на его выходе, после чего на выходе элемента И НЕ 9 появляется высокий потенциал. Высокие уровни напряжения с выходов злементов И-НЕ 8 и 9 вызывают формирование низкого потеншала на выходе элемента i Й-НЕ 10. Таким о.бразом, в момент t выходной асинхронный RS-триггер 11 переходит из нулевого состояния в единичное. Других изменений выходных потенциалов элементов устройства в момент i. не происходит до момента t окончания входного импульса. В момент t на выходе инвертора 1 образуется единичный сигнал, а на выходе элемента задержки 3 - нулевой. Он подтверждает единичный уровень напряжения на выходе элемента И-НЕ 8 и вызывает формирование высокого потенциала из выхода элемента И-НЕ 5. Таким образом, на обоих входах элемента И-НЕ 4 формируются единичные сишалы, и на его выходе образуется нулевой сигнал. Это означает, что асинхронный ,RS-триггер 6 перешел в состояние I. Других изменений выходных потенциалов элементов устройства в Момент tn не происходит. .. По окончании периода задержки элемента задержки 3 (момент Ц ) на его выходе появляется высокий уровень напряжения, после чего к обоим входам элемента И-НЕ 8 прикладываются высокие уровни напряжения. Это приводит к формированию на его выходе низкого потенциала, после чего на выходе элемента И-НЕ Ш. появляется высокий потенциал. Высокие уровни напряжения с выходов элементов И-ИЕ 7 и 10 вызывают формирование низкого потенциала на выходе элемента И-НЕ 9. Таким образом, в момент V . выходной асинхронный RS-триггер 1 переходит из сд1шич ного состо5шия в нулевое. В момент t. все выходные Сигналы элементов устройства для задержки импульсов совпадают с их исходными состояниями, и далее работа устройства повторяется. Из приведенного анализа работы видно, что устройство обеспечивает устойчивую и бессбой ную задержку выходного сигнала (выход элемента 9) относительно входного. Это позволя,ет значительно повысить надежность работы устройства в системах автоматики и вычислительной техники с высокими уровнями помех но цепям питания. Формула изобретения Устройство для задержки импульсов, содержащее входную шину, которая подключена 2 ,6 ко входу первого элемента задержки и через , инвертор ко входу второго элемента задержки, асинхронный RS-триггер на Двух элементах И-НЕ, отличающееся тем, тго, с целью повышення надежности и технологичности устройства, в него введены выходной асинхронный RS-триггср на двух элементах И-НЕ и два элемента И-НЕ, выходы которых соединены С соответствующими входами выходного RS-тригг.ера, первый вход первого элемента И-НЕ подключен к выходу первого триггера, первый вход которого соединен с выходом второго элемента задержки и вторым входом первого элемента И-НЕ. первый вход второго элемента И-НЕ подключен к выходу первого триггера, вход которого соединен с выходом первого элемента задержки и вторым входом второго элемента И-НЕ. Источники информации, принятые во внимание при экспертизе 1.Патент ФРГ N 2357651, кд. Н 03 К 5/13, опублик. 1975. 2.Самойлов Л. К. Устройства задержки информации в дискретной технике. М., Сов. радио, 1973, рис. 1.4 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задержки импульсов | 1980 |

|

SU921067A1 |

| Устройство для выделения одиночного импульса | 1989 |

|

SU1621147A1 |

| Устройство для задержки импульсов | 1979 |

|

SU817992A1 |

| Троичное счетное устройство | 1986 |

|

SU1338013A1 |

| Распределитель сигналов на десять каналов | 1986 |

|

SU1325683A1 |

| Формирователь импульсов | 1984 |

|

SU1231590A1 |

| Двоично-десятичный счетчик в коде 8-4-2-1 | 1987 |

|

SU1462474A1 |

| Устройство для выделения одиночного импульса | 1978 |

|

SU744935A1 |

| Троичное счетное устройство | 1975 |

|

SU579690A1 |

| Устройство для синхронизации импульсных последовательностей | 1979 |

|

SU864521A1 |

Авторы

Даты

1980-06-05—Публикация

1978-01-27—Подача