(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СЛОЖНЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU842829A1 |

| Устройство для преобразования по функциям Уолша | 1986 |

|

SU1383393A1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР ЕРМАКОВА-КАЖДАНА СПЕКТРА КУСОЧНО-ПОСТОЯННЫХ ФУНКЦИЙ (ВАРИАНТЫ) | 2001 |

|

RU2213996C2 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ СЕЙСМИЧЕСКИХ ИССЛЕДОВАНИЙ | 2020 |

|

RU2722462C1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛА В МОБИЛЬНОЙ СИСТЕМЕ СВЯЗИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ | 2004 |

|

RU2262201C1 |

| Устройство для вычисления спектра уолша функций синуса и косинуса | 1979 |

|

SU864291A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1137479A1 |

| ГЕНЕРАТОР ПРОИЗВОДНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2007 |

|

RU2327200C1 |

1

Изобретение относится к радиотехнике и может быть использовано в радиолокации, радионавигации и системах передачи информации.

Известно устройство для формирования четверичных последовательностей, содержащее генератор тактовых импульсов, связанный с двоичным счетчиком, причем выходы разрядов двоичного счетчика соединены через дешифратор и коммутатор со входами анализатора .четности 1.

Однако такое устройство формирует сложный сигнал, имеющий больщой уровень боковы лепестков автокорреляционных функций.

Наиболее близким к предлагаемому является устройство для генерирования сложных сигналов, содержащее последовательно соеданенные генератор тактовых импульсов, двоичный счетчик и логический блок, содержащий логические элемента И, ИЛИ, НЕ, а также резистр адреса, выходы которого подключены к другим входам логического блока 2.

Недостатком устройства является то, что оно также генерирует сигналы, корреляционные

функции которых имеют большой уровень боковых лепестков.

Цель изобретения - уменьшение уровня боковых лепестков автокорреляционной функции формируемого сигнала.

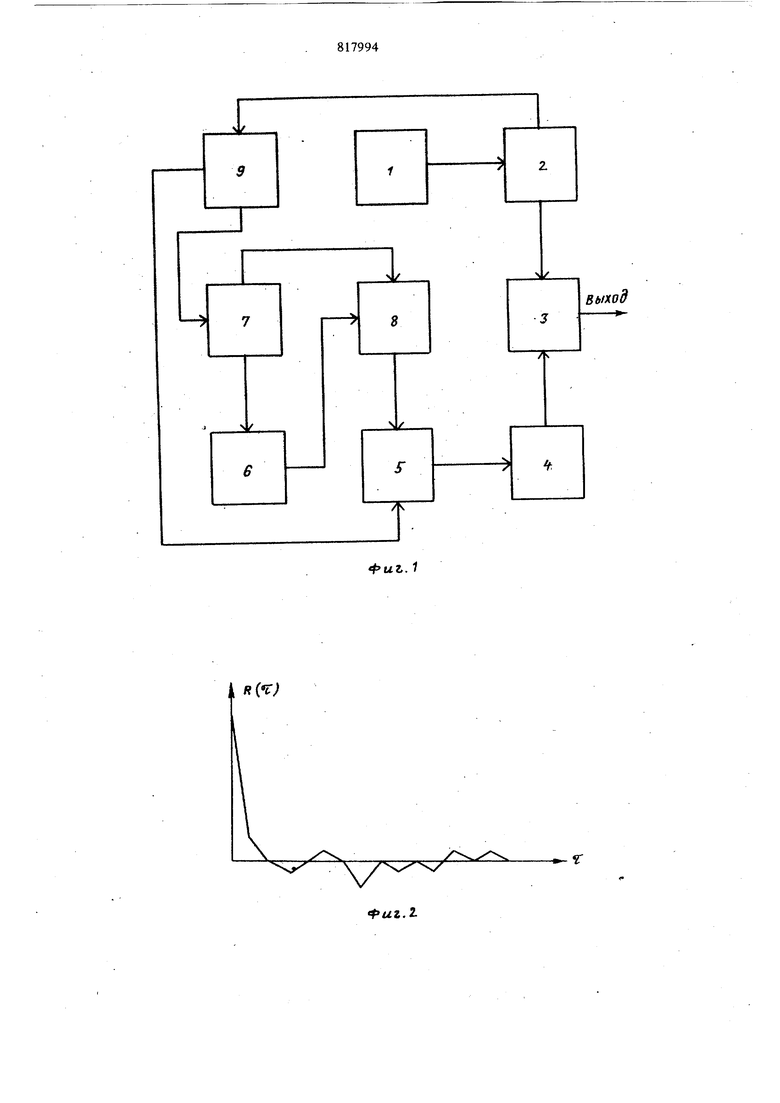

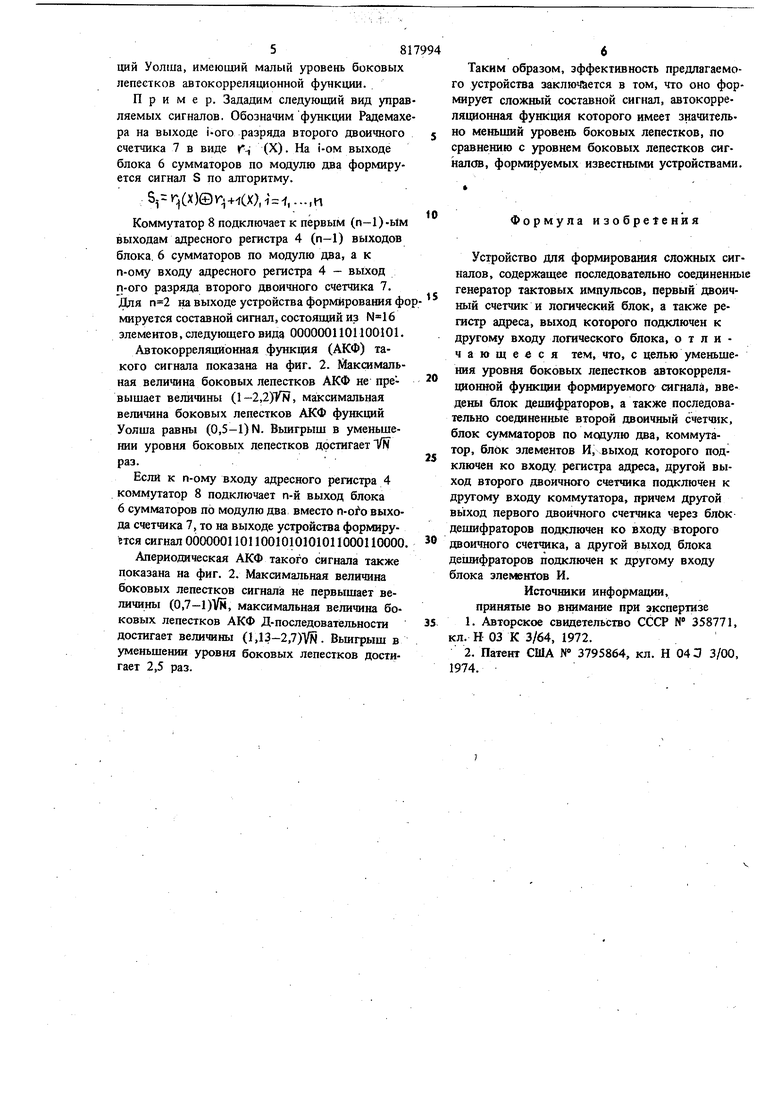

Поставленная цель достигается тем, что в устройство, содержащее последовательно соединенные генератор тактовых импульсов, первый двоичный счетчик и логический блок, а также регистр адреса, выход которого подключен к дрзоому входу логического блока, до,полнительно введены блок дешифраторов, а также последовательно соединенные второй двоичный счетчик, блок сумматоров по мрдулю два, коммутатор, блок элементов И, выход которого подключен ко входу регистра адреса, другой выход второго двоичного счетчика - к другому входу коммутатора,, причем другой выход первого двоичного счетчика через блок дешифраторов подключен к входу второго двоичного счетчика, а другой выход блока дешифраторов - к другому входу блока элементов И. На фиг. 1 представлена структурная схема предлагаемого устройства для формирования сложных сигналов; на фиг. 2 и 3 - апериодические автокорреЛядаонные функщш формируемых сигналов. Устройство содержит генератор 1 тактовых импульсов, первый двоичный счетчик 2, логический блок 3, регистр 4 адреса, блок 5 элементов И, блок 6 сумматоров по модулю два, второй двоичный счетчик 7, коммутатор 8, блок 9 дешифраторов. В устройстве последовательно соединены генератор 1 тактовых импульсов, двоичный счетчик 2 и логический блок 3, выход регистра 4 адреса подключен к другому входу логического блока 3j последовательно соединены второй двоичный счетчик 7, блок 6 сумматоров по модулю два, коммутатор 8 и блок 5 элементов И, выход которого подключен ко входу регистра 4 адреса, другой выход второго двоичного счетчика 7 подключён к другому входу коммутатора 8, другой выход первого двоичного счетчика 2 через блок 9 дешифрато ров - ко входу второго двоичного счетчика 7, а другой выход блока 9 дешифраторов к другому входу блока 5 элементов И. Блоки устройства выполняют следующие функции. Генератор 1 тактовых импульсов форл-шрует тактовые импульсы заданной частоты. Двоичны счетчики 2 и 7, регистр 4 адреса, блок 6 сумматоров по модулю два выполняют стандартные функции. Логический блок 3 содержит логические элементы И, ИЛИ, НЕ, которые формируют из меандровых фушс1Ц1Й с выхода двоичного счетчика 2 в соответствии с адресом функции Уолша по известному алгоритму. Коммутатор 8 коммутирует К входных сигналов на п выходов (). Блок 9 дешифраторов содержит два дешифратора, одан из которых настроен на одно логическое состояние, а другой - на другое логическое состояние разрядов двоичного счетчика 2. Методы практического выполнения перечисленных стру турных компонентов .не отличаются от известных. Устройство работает следующим образом. Генератор тактовых импульсов формирует тактовые импульсы с заданной частотой, которые поступают на вход первого двоичного счетчика 2, содержащий п разрядов, подключенных ко входу логического блока 3. Первый двоичный счетчнк 2 формирует п фу1псций Радемахер из которых логический блок 3 формирует 2 функций Уолша по известному алгоритму. Номер формируемой функции Уолша задается сигналадш управления,. формируемыми в параллельном коде на выходах адресного регистра 4. Выходы первого двоичного счетчи са 2 под44ключены ко входам блока 9 дешифраторов, содержащего два дешифратора. Выход первого дешифратора подключен ко входу блока .5 элементов И, а выход второго дешифратора к счетному входу второго двоичного счетчика 7.Первый дешифратор блока 9 дешифраторов настроен на нулевые логические состояния разрядов первого двоичного счетчика 2 (состояния Все нули) и импульс на выходе первого дешифратора появляется в момент формирования первого элемента функций Уолша, второй дешифратор блока 9 деишфраторов настроен на нулевые логические состояния первых (п-1)-ых разрядов первого двоичного счетчика 2 и на единичное логическое состояние .п-ого, последнего, разряда двоичного счетчика 2. Импульс на выходе второго де1иифратора появляется в момент формирования 2 (серединного) элемента функций Уолша. Импульс с выхода второго дешифратора блока 9 деишфраторов поступает на счетный вход второго двоичного счетчика 7, который формирует функции Радемахера, длительность элемента которых равна периоду функций Уолша. Функции Радемахера с выхода второго двоичного счетчика 7 поступают на блок 6 сумматоров по модулю два и на вход коммутатора 8.Блок 6 сумматоров по модулю Два содержит п сумматоров по модулю два, на входы которых поступают функции Радемахера. Сумматоры по модулю два производят суммирование друг с другом элементов функций Радемахера, сочетания которых выбирается по определенному закону. На выходах 6 сумматоров по модулю два и второго двоичного счетчика 7 формируется множество из К сиг.налов, которые поступают на входы коммутатора 8, который KOMMjrrapyeT К входов на п выходов, по заданному закону. На входы блока 5 элементов И поступают п выбранных сигналов управления, на другой вход блока 5 - стробирующий импульс с выхода первого дешифратора блока 9 дешифраторов. Элементы п выбранных сигналов в параллельном коде задают номер формируемой функции Уолша и поступают на вход адресного регистра 4 через блок 5 элементов И в момент формирования первого элемента функции Уолша, определяемый стробирующим импульсом. Разнесение во времени импульсов на выходах блока 9 дешифраторов обеспечивает двухтактный режим работы устройства, что исключает совпадение во времени процессов формирования элементов сигнала управления вторым счётчиком 7, блоком 6 сумматоров по модулю два, процесса занесения логических значений этих элементов и разряды адресного регистра 4. Формируемое множество сигналов управления позволяет сформировать составной сигнал функ58ЦИЙ Уолша, имеющий малый уровень боковых лепеетков автокорреляционной функции. Пример. Зададим следующий вид управ ляемых сигналов. Обознашм функции Радемахе ра на выходе разряда второго двоичного счетчика 7 в виде ,- (X). На i-ом выходе блока 6 сумматоров по модулю два формируется сигнал S по алгоритму. 2гГ|(х)(,,...,и Коммутатор 8 подключает к первым (п-1)-Ым выходам адресного регистра 4 (п-1) выходов блока. 6 сумматоров по модулю два, а к п-ому входу адресного регистра 4 - выход п-ого разряда второго двоичного счетчика 7. Для на выходе устройства формирования фо мируется составной сигнал, состоящий из элементов, следующего вида 0000001101100101. Автокорреляционная функция (АКФ) такого сигнала показана на фиг. 2. Максимальная величина боковых лепестков АКФ не превыщает величины (1-2,2)Уы, максимальная величина боковых лепестков АКФ функций Уолща равны (0,5-1) N. Вьшгрыш в уменьщении уровня боковых лепестков достигает 1 раз. Если к п-ому входу адресного регистра 4 коммутатор 8 подключает п-й выход блока 6 сумматоров по модулю два вместо n-ofo выхода счетчика 7, то на выходе устройства формируется сигнал 00000011011001010101011000110000. Апериодическая АКФ такого сигнала также показана на фиг. 2. Максимальная величина боковых лепестков сигнал;а не первышает величины (0,7-1)1/М, максимальная величина боковых лепестков АКФ Д-последоват1ельности достигает величины (1,13-2,7)V . Вьшгрыш в уменьшении уровня боковых лепестков достигает 2,5 раз. Таким образом, эффективность предлагаемого устройства заключается в том, что оно формирует сложный составной сигнал, автокорреляционная функция которого имеет значительно меньший уровень боковых лепестков, по сравнению с уровнем боковых лепестков сигналов, формируемых известными устройствами. Формула изобре1ения Устройство для формирования сложных сигналов, содержащее последовательно соединенные генератор тактовых импульсов, первый двоичный счетчик и логический блок, а также регистр адреса, выход которого подключен к другому входу логического блока, отличающееся тем, что, с целью уменьшения уровня боковых лепестков автокорреляционной функции формируемога сигнала, введены блок дешифраторов, а также последовательно соединенные второй двоичный счетчик, блок сумматоров по модулю два, коммутатор, блок злементов И, выход которого подключен ко входу регистра адреса, другой выход второго двоичнсяо счетчика подключен к другому входу коммутатора, причем другой выход первого двоичного счетчика через блок дешифраторов подключен ко входу второго двоичного счетчика, а другой вь1ход блока дешифраторов подключен к другому входу блока элементов И. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 358771, кл. Н 03 К 3/64, 1972. 2.Патент США № 3795864, кл. Н 043 3/00, 1974.

/

Puz,i

Авторы

Даты

1981-03-30—Публикация

1979-05-21—Подача