1

Изобретение относится к области вычислите/1ьной техники и предназначеив .для использования в нриборах и системах управления различными объектами.

Известно устройство для дифференцирования 1, содержащее генератор опорной частоты, пять счетчиков, делитель, счетчик результата, триггер, четыре группы схем запрета (элементов И) н одну схему запрета (элемент И). Это устройство предназначено для вычисления производной обратной величины от входного кода. При добавлении одного дополнительного счетчика результата и повторении цикла преобразования устройство может быть использовано для дифференцирования входного сигнала.

Однако функциональные возможности устройства ограничены, так как оно не позволяет вычислять вторую производную. Низкое быстрее действие устройства обусловлено необходимостьо двухкратного преобразования кода во временной интервал (для каждого отсчета входной последовательности), а ннзкая точность - тем, что дифференцирование осуществляется без сглаживания случайных ошибок.

Известно цифровое сглаживающее устройство 2, содержащее два накапливающих сумматора по разрядов каждый (пит разрядность входной информации н постоянных множителей соответственно) и п-разрядный регистр.

Недостатками данного устройства являются: ограниченные функциональные возможности, так как оно предназначено только для сглаживания случайных помех во входном сигнале и не вычисляет первую н вторую производные от входного сигнала, и низкая точность вычисления, из-за отсутствия компенсаций по первой и второй производных при сигналах, полезная составляющая которых описывается полиномом первой и второй степеней в функции времени.

Из известных устройств наиболее блнзким по технической сущности к изобретению является дифференцирующе-сглаживающее устройство |3J, предназначенное для вычисления сглаженных значений первой производной изме ряемого сигнала с наложенной а.ддитивной некоррелированной случайной помехой.

Это устройство содержит блок оперативной памяти, блок вычисления спектральных коэффициентов Фурье - Радемахера, сдвиговый регистр, сумматор и блок управления. Вход устройства подсоединен к первому информационному входу блока оператнвной памяти, выход которого подключен к первому входу блока

вычисления спектральных коэффициеитоЕ Фурье Радемахера, первый выход которого подключен к первому входу слвщ-ового регистра. Выход сдвигового регистра подсс единен к первому входу сумматора, выход которого подключен к первому выходу устройства, выходы блока управления с первого по пятый подключены соответственно к вторым входам сумматора, сдвигового регистра и ко второму, третьему и четвертому входам блока вычисления спектральных коэффициентов Фурье - Радемахера.

Однако с помоцью этого устройства можно определить сглаженное значение первой производной входного сигнала без динамической ошибки только для случая, когда полезная составляющая описывается полиномом первой степени. Устройство не предназначено для вычисления текущих сглаженных значений входного сигнала и его второй производной.

Кроме того, в устройстве каждому рабочему циклу вычисления производной предшествует этап обновления выборки входного сигнала. заключающийся в последовательном сдвиге информации Б блоке оперативной памяти (ОП) на одну ячейку, что приводит к 2 N-кратному выполнению операций обрапгения к ОМ (N -объем входной выборки, объем ОП) и понижению быстродействия устройства.

В таком устройстве точность вычислений понижена за счет отсутствия компенсации по второй производной при сигнале, полезная составляющая которого описывается полиномом второй степени.

Целью изобретения является расширение функционгмьных возможностей устройства, повышение быстродействия и точности его работы

Поставленная цель достигается тем, что в предложенное дифференцирующе-сглаживающее устройство введены блоки суммирования по модулю два, формирования адресов, коммутации, две схемы сравнения. Выходы блока управления с шестого по десятый подключены соответственно к пяти входам блока формирования адресов, два выхода которого подключены соответственно к двум управляющим входам блока оперативной памяти, второй информационный вход которого подсоединен к выходу сумматора, а выход - к второму выходу устройства. Одиннадцатый выход блока управления но.дключен к пятому входу блока вычисления спектральных коэффициентов Фурье-Радемахера, второй выход которого через блок суммирования по модулю два подключен к первому входу блока коммутации, прямой и инверсный выходы которого подключены соответственно к шестому и седьмому входам блока вычисления спектральных коэффициентов Фурье - Радемахера. Второй вход блока коммутации подключен к двенадцатому выходу блока управления, три входа которого подключены соответственно к выходам двух схем сравнения и третьему выходу блока вычисления спектральных коэффициентов Фурье - Радемахера первый выход которого подключен к входам двух схем сравнения.

Кроме того, в устройстве блок суммирования по модулю два содержит (п - 1) групп

сумматоров по модулю два, причем первы( входы сумматоров по модулю два каждой группы объединены и подключены соответственно к одному из первых (п - 1) разрядов п-разрядного входа блока. Вторые входы сумматоров по модулю два каждой группы подключены соответственно к одному из разрядов п-разрядиого входа блока, начиная с разряда, номер которого на единицу превышает номер группы. Выход каждого сумматора по модулю два подключен к одному из m разрядов выхода блока.

Блок коммутации устройства содержит m элементов И, элементы ИЛИ, НЕ. Первые входы элементов И подключены к m разрядам первого входа блока коммутации. Вторые входы элементов И подключены к m разрядам второго входа блока, выход каждого элемента и соединен с соответствующим входом элемента ИЛИ, выход которого подключен соответственно к прямому выходу блока и входу элемента НЕ, выход которого подключен к инверсному выходу блока.

Блок формирования адресов в устройстве содержит счетчик, реверсивный счетчик, дешифратор и триггер. Счетный вход счетчика, счетный и управляющий входы реверсивного счетчика, единичный и нулевой входы триггера подключены соответственно к пяти входам блока. Выходы счетчика и реверсивного счетчика подключены соответственно к первому и второму входам дешифратора. Единичный выход триггера и выход дешифратора подключены соответственно к первому и второму выходам блока формирования адресов.

Блок вычисления спектральных коэффициентов Фурье - Радемахера содержит сумматор-вычитатель, генератор функций Радемахера, коммутатор, элементы И, элементы ИЛИ, один из которых подключен между прямым выходом коммутатора и первым входом, первого элемента И, второй элемент ИЛИ - между инверсным выходом коммутатора и первым входом второго элемента И. Вторые входы элементов И соединены с третьим входом блока, выходы подключены соответственно к первому и второму входам сумматора-вычитателя, третий и четвертый входы которого подключены соответственно к первому и пятому входам блока, первый и второй выходы - соответственно к первому и третьему выходам блока. Четвертый вход блока соединен со входом генератора функций Радемахера, выход которого подключен ко второму выходу блока и первому входу коммутатора, второй вход коммутатора соединен со вторым входом блока, шестой и седьмой входы которого подключены соответственно ко вторым входам первого и второго элементов ИЛИ.

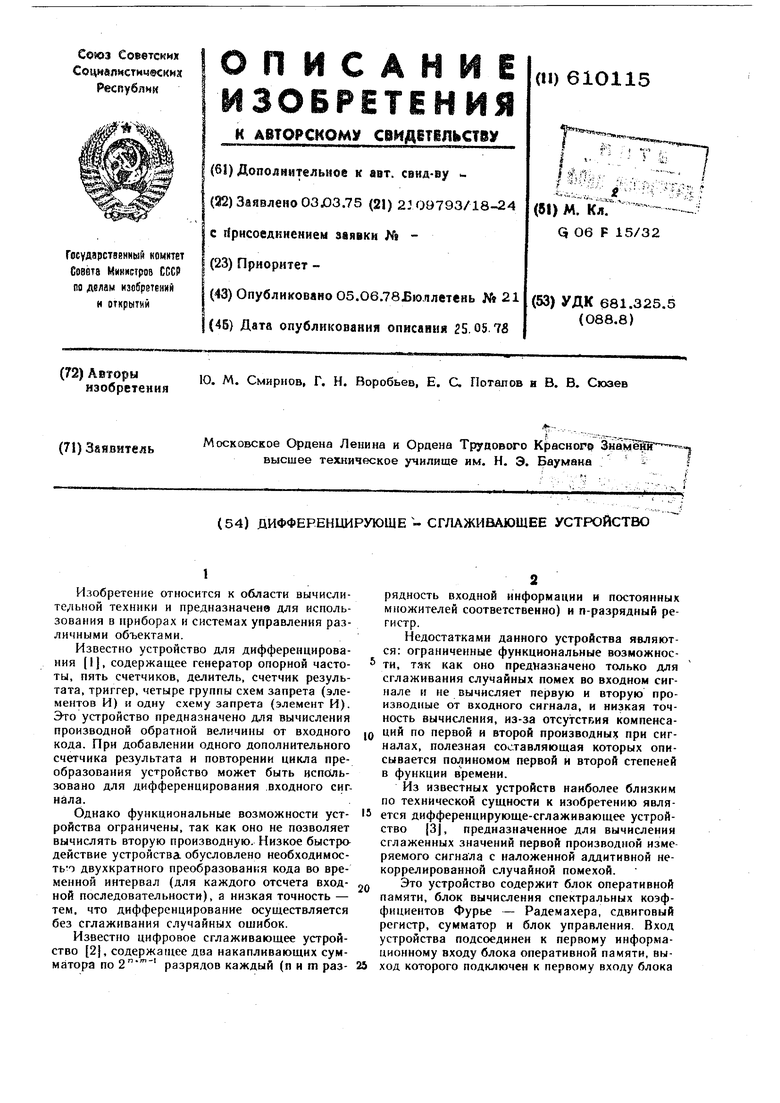

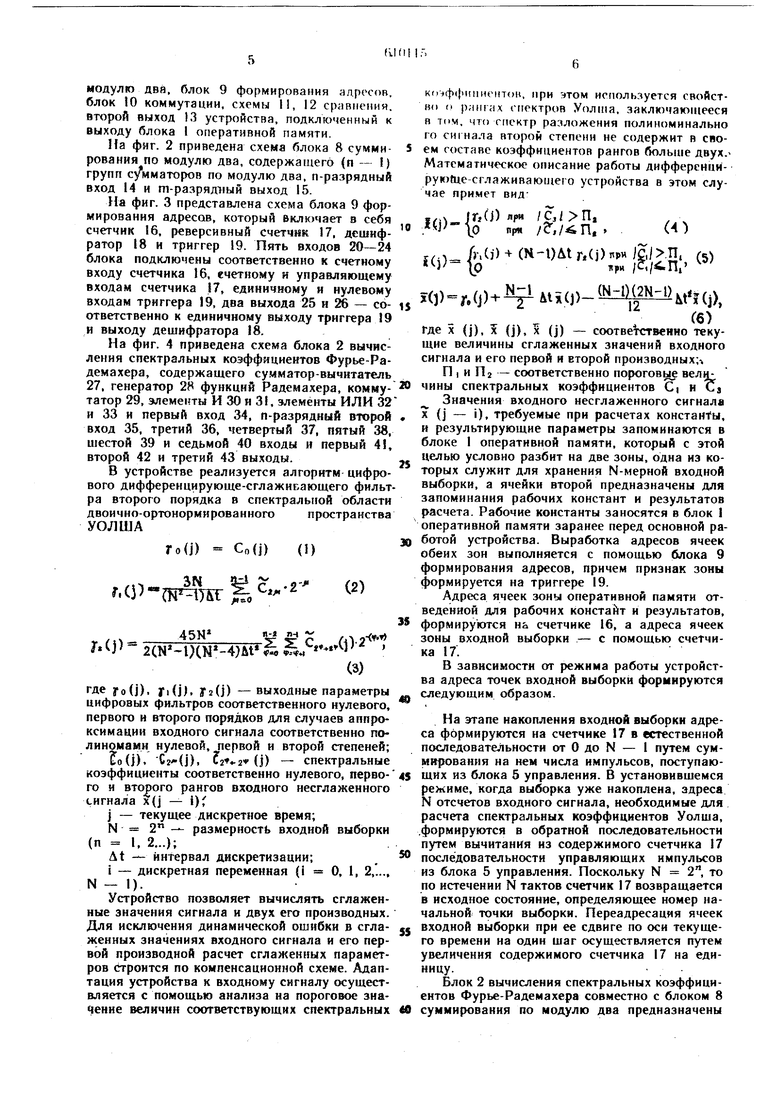

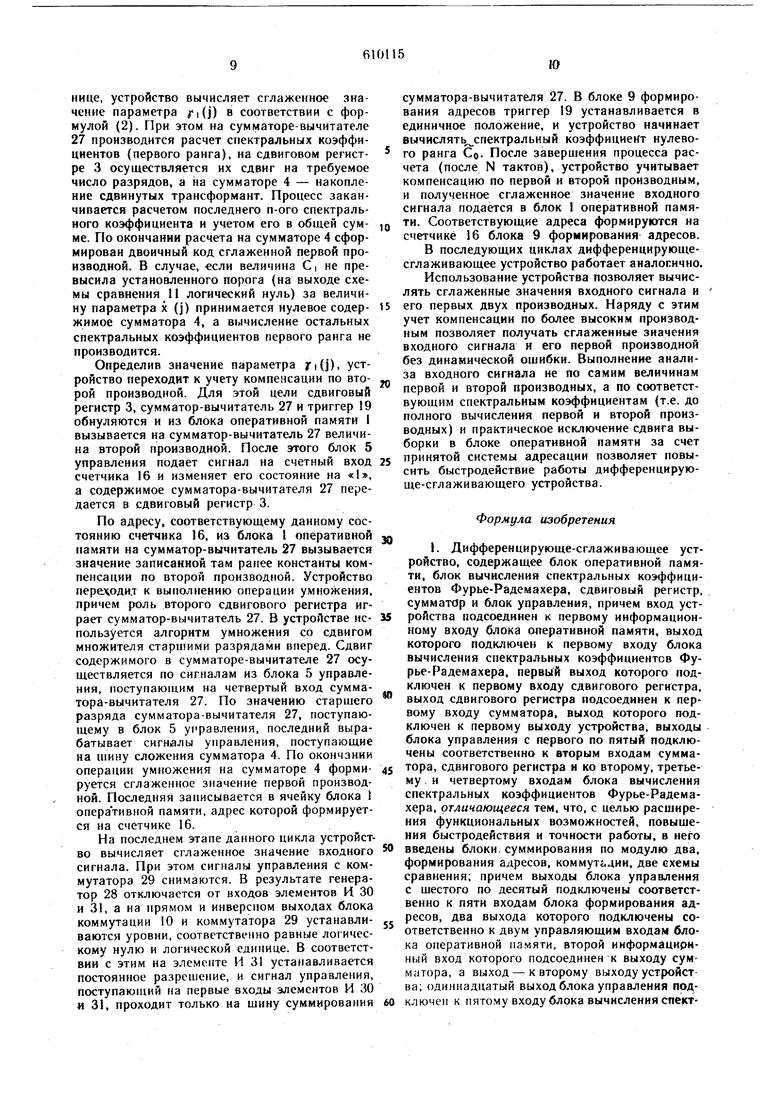

На фиг. 1 представлена структурная схема диффереицирующе-сглаживающего устройства, содержащего блок 1 оперативной памяти, блок 2 вычисления спектральных коэффициентов Фурье-Радемахера сдвиговый регистр 3, сумматор 4i блок 5 управления. Вход 6 устройства подключен к первому информационному входу блока 1 оперативной памяти, первый выход 7 - к выходу сумматора 4. Кроме того, устройство содержит блок 8 суммирования по модулю два. блок 9 формирования алросов, блок 10 коммутации, схемы 1, 12 сравнения. второй выход 13 устройства, подключенный к выходу блока I оперативной памяти. На фяг. 2 приведена схема блока 8 суммирования по модулю два, содержащего (п - 1) групп сумматоров по модулю два, п-разрядиы вход 14 и т-разряд11ый выход 15. На фиг. 3 представлена схема блока 9 формирования адресов, который включает в себя счетчик 16, реверсивный счетчик 17, дешифратор 18 и триггер 19. Пять входов 20-24 блока подключены соответственно к счетному входу счетчика 16, ечетному и управляющему входам счетчика 17, единичному и нулевому входам триггера 19, два выхода 25 и 26 - соответственно к единичному выходу триггера 19 н выходу дешифратора 18. На фиг. 4 приведена схема блока 2 вычисления спектральных коэффициентов Фурье-Радемахера, содержащего сумматор-вычитатель 27, генератор 28 функций Радемахера, коммутатор 29, элементы И 30 н 31, элементы ИЛИ 32 н 33 н первый вход 34, п-разрядный второй вход 35, третий 36, четвертый 37, пятый 38, шестой 39 и седьмой 40 входы и первый 41, второй 42 и третий 43 вы.ходы. В устройстве реализуется алгоритм цифрового дифференцирующе-сглажиьающего фильтра второго порядка в спектральной области двоично-ортонормнрованного пространства УОЛША Го() Co(j) (1) г. и-« n-t . tJJ4- /,л j4«f.w О 2(N-l) где fo(j). JTiCj). ifsCj) -выходные параметры цифровых фильтров соответственного нулевого, первого и второго порядков для случаев аппроксимации входного сигнала соответственно полнномами нулевой, первой н второй степеней; o(j), Сг(). .2 (j) - спектральные коэффициенты соответственно нулевого, первого и второго рангов входного несглаженного снгнала x(j - I) j - текущее дискретное время; N 2 - размерность входной выборки (п 1, 2...); At - интервал дискретизации; I - днскретная переменная { О, 1, 2,..., N - 1). Устройство позволяет вычислять сглаженные значения сигнала и двух его пронзводных. Для нсключення динамической ошибки в сглаженных значениях входного сигнала н его первой производной расчет сглаженных параметров (1троится по компенсацнонной схеме. Адаптация устройства к входному сигналу осуществляется с помощью аналнза на пороговое значение величин соответствующих спектральных кочффимиенток, нри этом испо.пьзуется свойство о рангах спектров Уолта, заключающееся в том. что гпсктр разложения полиноминальио го сигнала второй степени не содержит в своем составе коэффициентов рангов больше двух. Математическое описание работы дифференнируюйхе-сглаживающею устройства в этом случае при.мет внд...ч 1Г,0) лр« /С, . пр« /,, i(, ) (H-OAt r,(j) Р« fi( П. (5) IPпри NjlMi(p(Nzl)Md)Mir(i), (J)y.(j) где X (J), X (j), X (j) - соответственно текущне величины сглаженных значений входного сигнала и его первой и второй производных П 1 и П2 - соответственно noporoBbie велнчины спектральных коэффициентов С| н efj Значения входного несглаженного сигнала )t (j - i), требуемые прн расчетах константы, и результирующие параметры запоминаются в блоке I оперативной памятн, который с этой целью условно разбит на две зоны, одна из которых служит для хранения N-мерной входной выборки, а ячейки второй предназначены для запоминания рабочих констант н результатов расчета. Рабочие коистаиты заносятся в блок I оперативной памяти заранее перед основной работой устройства. Выработка адресов ячеек обеих зон выполняется с помощью блока 9 формнрования адресов, причем признак зоны формируется на триггере 19. Адреса ячеек зоны оперативной памяти отведенной для рабочнх констайт и результатов, формируются на счетчнке 16, а адреса ячеек зоны входной выборки - с помощью счетчика 17. В зависимости от режима работы устройства адреса точек входной выборки формируются следующим образом. На этапе накоплення входной выборки адреса формнруются на счетчике 17 в естественной последовательности от О до N - 1 путем суммкровання на нем чнсла импульсов, поступаюших из блока 5 управления. В установивщемся режиме, когда выборка уже накоплена, адреса N отсчетов входного снгнала, необходнмые для расчета спектральных коэффициентов Уолща, .формируются в обратной последовательностн путем вычитания из содержнмого счетчика 17 последовательности управляющих импульсов из блока 5 управления. Поскольку N 2, то по истечении N тактов счетчик 17 возвращается в исходное состоянне, определяющее номер начальной точкн выборки. Переадресация ячеек входной выборки при ее сдвиге по оси текущего времени на один шаг осуществляется путем увеличения содержнмого счетчика 17 на еднннцу. Блок 2 вычисления спектральных коэффициентов Фурье-Радемахера совместно с блоком 8 суммнровання по модулю два предназначены

для вычисления спектральных коэффициентов Уолша нулевого, первого и BTopoio рангов, причем значение функций Уолша иервою ранга (функций Радемахера) вырабатывается с помощью генератора 28 функций Радемахера, а значение функций Уолша второго ранга - с помощью блока 8 суммирования по модулю два.

Дифференцирующе-сглаживающее устройство работает следующим образом.

Блок 5 управления вырабатывает сигнал начальной установки, который обнуляет содержимое генератора 28, сумматора-вычитателя 27, сдвигового регистра 3, сумматора 4 и счетчиков 16 и 17 шнны обнуления на чертежах не показаны). По выполнении начальных установок устройство переходит к режиму накопления входной выборки. В этом режиме сигналом из блока 5 управления триггер 19 устанавливается в единичное состояние и в ячейки блока I оперативной памяти, адреса которых формируются в счетчике 17 блока 9 формирования адресов, заносятся текущие координаты входного сигнала, поступающие на вход 6 устройства. Указанная последовательность действий повторяется N раз, после чего устройство переходит к установивщемуся режиму.

В начале каждаго цикла установивщегося режима (за исключением первого) сигнал из блока 5 управления, поступающий на счетный вход счетчика 17 блока 9 формирования адресов, устанавливает в счетчике адрес начальной точки сдвинутой выборки. По этому адресу в блок 1 оперативной памяти заносится поступающее на его первый вход текущее значение входного сигнала. При этом новая выборка сформирована (эта операция на первом цикле не выполняется, так как выборка для первого цикла подготавливается на этапе накопления выборки). После этого устройство переходит к расчету спектральных коэффициентов. На этом этапе блок 5 управления выдает управляющие сигналы на г.торой вход блока 10 коммутации и с его помощью подключает первый выход (выход функции Уолша второго ранга Wj) блока 8 суммирования по модулю два через элементы ИЛИ 32 и 33 к первым входам элементов И 30 и 31. Затем блок 5 управления начинает синхронно подавать сигналы управления соответственно на счетный вход счетчика 17, установленного предварительно в режим вычитания, на вход генератора 28 и на вторые входы элементов И 31, 30. При этом выходной сигнал триггера 19 и содержимое счетчика 17 через дешифратор 18 поступают на первый и второй управляющие входы блока I оперативной памяти в виде адреса ячейки.

Информация из блока 1 оперативной памяти подается на третий вход сумматора-вычитателя 27. Если значение функции Уолша «-J-J (что соответствует логической единице на инверсном выходе блока 10 коммутации), то импульс управления проходит через открытый элемент И 31 на второй вход сумматора-вы. читателя 27 и поступающая информация суммируется с содержимым сумматора-вычитателя 27. Если значение функции Уолща-I, открыт элемент И 30 и на сумматоре-вычитателе 27 выполняется операция вычитания. По истечении N тактов на сумматоре-вычитателе 27 сформирован спектральный коэффициент Сз, ко. торый поступает на входы схем сравнения 11

и 12. В случае если на выходе схемы сравнения 12 сформирована логическая единица (т.е. величина спектрального коэффициента (Гз больше порога П2), устройство продолжает расчет второй производной в соответствии с

уравнением (3). При этом содержимое сумматора-вычитателя 27 передается в сдвиговый регистр 3, сам сумматор-вычитатель 27 обнуляется, а по сигналу с блока 5 управления к входам элементов «И 30 и 31 подключается с помощью блока 10 коммутации следующий разряд т-разрядного выхода блока 8 суммирования по модулю два (выход следующей функции Уолша второго раига). На сумматоре-вычитателе 27 формируется следующий спектральный коэффициент второго ранга Cs. Параллельио с этим на сдвиговом регистре 3 получают величину Сз2, которая суммируется с содержимым сумматора 4. В дальнейшем на сумматоре-вычитателе 27 формируется очередной спектральный коэффициент, а на сдвиговом регистре 3 и сумматоре 4 накапливается сумма

5 сдвинутых на соответствующее число разрядов (формула (3)) величин трансформант второго ранга. После завершения расчета в соответствии с формулой (3) на сумматоре 4 будет сформирован двоичный код числа с точностью до постоянного коэффициента (который может

быть учтен путем масштабирования) равного сглаженному значению второй производной входного сигнала. После того как расчет второй производной заканчивается, блок 5 управления выдает сигнал на нулевой вход триггера

5 и устанавливает его в нулевое состояние, тем самым включая в работу зону памяти, отведениую для хранения конечных результатов. Содержимое сумматора 4 записывается в ячейку блока 1 оперативной памяти с адресом, сформированным из нулевого состояния триггера 19

0 и нулевого содержимого счетчика 16.

В случае если на выходе с.хемы сравнения 12 появляется логический нуль (т.е. вторая производная равна нулю), устройство сразу переходит к процедуре записи нулевого содержимого сумматора 4 в блок оперативной памяти 1. После записи результата сумматор 4, сдвиговый регистр 3 и сумматор-вычитатель 27 обнуляются, в триггер 19 заносится единица, и устройство переходит к вычислению первой производной. При этом блок 5 управления выдает

0 сигналы на второй вход коммутатора 29 и с его помощью через элементы ИЛИ 32 и 33 подключает выходы соответствующих функций Уолша первого раига (функций Радемахера) ко входам элементов И 30 и 31. Расчет начинается со спектрального коэффициента C|. В блоке 5 управления в этом случае анализируется выход схемы сравнения 11, и по его состоянию определяется дальнейшая последовательиость действий.

При появлении на выходе схемы сравнения

0 II сигнала, соответствующего логической едннице, устройство вычисляет сглаженное значение параметра (j) в соответствии с формулой (2). Прн этом на сумматоре-вычитателе 27 производится расчет спектральных коэффициентов (первого ранга), на сдвиговом регнстре 3 осуществляется нх сдвнг на требуемое число разрядов, а на сумматоре 4 - накопление сдвинутых трансформант. Процесс заканчивается расчетом последнего п-ого спектрального коэффициента и учетом его в общей сумме. По окончании расчета на сумматоре 4 сформирован двоичный код сглаженной первой производной. В случае, «ели величина C| не превысила установленного порога (на выходе схемы сравнения 11 логический нуль) за величину параметра х (j) принимается нулевое содержимое сумматора 4, а вычисление остальных спектральных коэффициентов первого ранга не производится.

Определив значение параметра т(), устройство переходит к учету компенсации по второй производной. Для этой цели сдвиговый регистр 3, сумматор-вычитатель 27 и триггер 19 обнуляются и из блока оперативной памяти 1 вызывается на сумматор-вычитатель 27 величина второй производной. После этого блок 5 управления подает сигнал на счетный вход счетчика 16 и изменяет его состояние на «1, а содержимое сумматора-вычитателя 27 передается в сдвиговый регистр 3.

По адресу, соответствующему данному состоянию счетчика 16, из блока 1 оперативной памяти на сумматор-вычитатель 27 вызывается значение записанной там ранее константы компенсации по второй производной. Устройство перечоди.т к выполнению операции умножения, причем роль второго сдвигового регистра играет сумматор-вычитатель 27. В устройстве используется алгоритм умножения со сдвигом множителя старшими разрядами вперед. Сдвиг содержимого в сумматоре-вычитателе 27 осуществляется по сигналам из блока 5 управления, поступающим на четвертый вход сумматора-вычитателя 27. По значению старщего разряда сумматора-вычитателя 27, поступающему в блок 5 у1фавления, последний вырабатывает сигналы управления, поступающие на щину сложения сумматора 4. По окончании операции умножения на сумматоре 4 формируется сглаженное значение первой производной. Последняя записывается в ячейку блока t оперативной памяти, адрес которой формируется на счетчике 16.

На последнем этапе данного цикла устройство вычисляет сглаженное значение входного сигнала. При этом сигналы управления с коммутатора 29 снимаются. В результате генератор 28 отключается от входов элементов И 30 и 31, а на прямом и инверсном выходах блока коммутации 10 и коммутатора 29 устанавливаются уровни, соответственно равные логическому нулю и логической единице. В соответствии с этим на элементе И 31 устанавливается постоянное разрешение, и сигнал управления, поступающий на первые входы элементов И 30 и 31, проходит только на щину суммирования

сумматора-вычитателя 27. В блоке 9 формирования адресов триггер 19 устанавливается в единичное положение, и устройство начинает вычислять спектральный коэффнциент нулевого ранга GO. После заверщения процесса расчета (после N тактов), устройство учитывает компенсацию по первой и второй производным, и полученное сглаженное значение входного сигнала подается в блок 1 оперативной памяти. Соответствующие адреса формируются на счетчике 16 блока 9 формирования адресов.

В последующих циклах дифференцнрующесглаживающее устройство работает аналогично.

Использование устройства позволяет вычислять сглаженные значения входного сигнала и его первых двух производных. Наряду с этим учет компенсации по более высоким производным позволяет получать сглаженные значения входного сигнала и его первой производной без динамической ощибки. Выполиение анализа входного сигнала не по самим величииам первой и второй производных, а по соответствующим спектральиым коэффициентам (т.е. до полного вычисления первой и второй производных) и практическое исключение сдвига выборки в блоке оперативной памяти за счет принятой системы адресации позволяет повысить быстродействие работы дифференцирующе-сглаживающего устройства.

Формула изобретения

I. Дифференцирующе-сглаживающее устройство, содержащее блок оперативной памяти, блок вычисления спектральных коэффициентов Фурье-Радемахера, сдвиговый регистр, сумматор и блок управления, причем вход устройства подсоединен к первому информационному входу блока оперативной памяти, выход которого подключен к первому входу блока вычисления спектральных коэффициентов Фурье-Радемахера, первый выход которого подключен к первому входу сдвигового регистра, выход сдвигового регистра подсоединен к первому входу сумматора, выход которого подключен к первому выходу устройства, выходы блока управления с первого по пятый подключены соответственно к вторым входам сумматора, сдвигового регистра и ко второму, третьему и четвертому входам блока вычисления спектральных коэффициентов Фурье-Радемахера, отличающееся тем, что, с целью расширения функциональных возможностей, повышения быстродействия и точности работы, в него введены блоки, суммирования по модулю два, формирования адресов, коммутации, две схемы сравнения; причем выходы блока управления с шестого по десятый подключены соответственно к пяти входам блока формирования адресов, два выхода которого подключены соответственно к двум управляющим входам блока оперативной памяти, второй информацирнный вход которого подсоединен к выходу сумматора, а выход - к второму выходу устройства; одиннадцатый выход блока управления подключен к пятому входу блока вычисления спектральных коэффициентов. Фурье-Ралимахора, второй выход которого через блок суммиропания по модулю два подключен к первому входу блока коммутации, прямой и инверсный выходы которого подключены соответственно к шестому и седьмому входам блока вычисления спектральных коэффициентов Фурье-Радемахера; второй вход блока коммутации подключен к двенадцатому выходу блока управления, три входа которого подключены соответственно к выходам двух схем сравнения и третьему выходу блока вычисления спектральных коэффициентов Фурье-Радемахера, первый выход которого подключен к входам двух схем сраанения. 2.Устройство поя. I, отличающееся тем, что блок суммирования по модулю два содержит (п - I) групп сумматоров по модулю два; причем первые входы сумматоров по модулю два каждой группы объединены и подключены соответственио к одному из первых (п - 1) разрядов п-разрядного входа блока, вторые входы сумматоров по модулю два каждой группы подключены соответственно к одному из разрядов п-разрядного входа блока, начиная с разряда, номер которого на единицу превышает номер группы; выход каждого сумматора по модулю два подключен к одному из m разрядов выхода блока. 3.Устройство по п. 1, отличающееся тем, что блок коммутации содержит m элементов И, элементы ИЛИ, НЕ; первые входы элементов И подключены к ш разрядам первого входа блока коммутации; вторые входы элементов И подключены к m разрядам второго входа блока; выход каждогоэлемента И соединен с соответствующим входом элемента ИЛИ, выход которого подключен соответственно к прямому выходу блока и входу элемента НЕ, выход которого подключен к инверсному выходу блока. 4.Устройство по п. I, отличающееся тем, что блок формирования адресов содержит счетчик, реверсивный счетчик, дешифратор и триг4тр; причем счетный вход счетчика, счетный и управляюп1ий входы реверсипного счетчика, единичный и нулевой входы триггера подключены соответственно к пяти входам блока; йыходы счетчика и реверсивного счетчика подключены соответственно к первому и второму входам дешифратора; единичный выход триггера и выход дешифратора подключены соответственио к первому и второму выходам блока формирования адресов, 5. Устройство по п. 1, отлинеиощееся тем, чп) блок вычисления спектральных коэффициентов Фурье-Радемахера содержит сумматор-вычитатель, генератор функций Радемахера, коммутатор, элементы И, элементы ИЛИ, один нз которых подключен между прямым выходом коммутатора и первым входом первого элемента И, второй элемент ИЛИ - между инверсным выходом коммутатора и первым-входом второго элемента И; вторые входы элементов И соединены с третьим входом блока, выходы подключены соответственно к первому и второму входам сумматора-вычитателя, третий и четвертый входы которого подключены соответственно к первому и пятому входам блока, чтервый и второй выходы - соответственно к первому н т.ретьему выходам блока, четвертый вход которЬгб соединен со входом генератора функцнЙ Радемахера, выход которого подключен ко второму выходу блока н первому входу коммутатора, второй вход которого соединен со вторым входом блока, шестой н седьмой входы которого подключены соответственно ко вторым входам первого и второго элейентов ИЛИ. Источники ннформации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 355618, М.кл. G 06 f 7/38, 16.03.71. 2.Авторское свидетельство СССР № 377785, М.кл. G 06 f 15/32, 05.08.70. 3.Заявка 2007207/24, М кл. G 06 f 15/32, 20.03.74, по которой вынесено решение о выдаче авторского свидетельства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференцирующе-сглаживающее устройство | 1976 |

|

SU636615A1 |

| Дифференцирующе-сглаживающее устройство | 1974 |

|

SU714404A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU577531A1 |

| Устройство для ортогонального преобразования цифровых сигналов по Фурье-Чебышеву | 1983 |

|

SU1136181A1 |

| Анализатор спектров | 1982 |

|

SU1023341A1 |

| Генератор функций | 1979 |

|

SU842765A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Ранговый обнаружитель сигналов | 1981 |

|

SU970291A1 |

| Процессор для корреляционного анализа | 1978 |

|

SU744601A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1983 |

|

SU1159031A2 |

-44

3f

Авторы

Даты

1978-06-05—Публикация

1975-03-03—Подача