54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СПЕКТРА

1

Изобретение отиоситсн к цифровой вычислительнф те снике и может быть использовано-при построении специализированных процессоров для преобразований спекфальных характеристик в различньох базисных системах функций, , цифровых многоканальных систем связи, систем автоматизированного синтеза сложных структурных злементов цифрой©й..техники методом спектральных отобр ажёний, аппаратуры распозн- вания и имитации образов, а также при создании диагностической аппаратуры,для систем и устройств, работающих . в базисе функций Уолша. Известнф устройство для спектрального аналифа, содержащее три блока памяти, ко1Ймутатор, блок задания тригонометрических функций, операционный блок, выполненный в виде сумматоров и умножителей, блок инверсной перестановки и соответствующие связи. Устройство реализует наиболее эффективный метод вычислений быстрое преобразование Фурье 1.

.Наиболее близким по технической сущности к изобретению является устройство, содержащее блок определения корреляционной функции, три переключателя, два блока памяти. ФУНКЦИЙ УОЛША

блок умножения, регистр, цифроаналоговый преобразователь, интегратор, блок задания констант и блок адресации, в совокупности адекватные по, функциональному назначению блоку определения весового коэффициента, шифратор, блок сравнения, три счетчика, элемент И, ключевой элемент, адекватный по функциональному назна10чению триггеру, делитель, сумматор, дешифратор, преобразователь кода, блок управления и соответствующие связи. Устройство позволяет вычис.лить спектры сигналов и процессов, в том числе и функций Уолша 2.

15

Недостатки известных устройств заключаются в низком быстродействии, а при решении ряда задач - полной непригодности для спектрального анализа функций Уолша и образующих их функций.

Цель изобретения - повышение быстродействия и расширение функцирнальных возможностей за счет определения спектра-функций Уолша и Радемахера только по их номерам, без генерации во времени этих функций.

Поставленная цель достигается тем, что в устройство, содержащее

30 счетчик, блок адресации, блок эадания констант, блок умножения, сумматор, переключатель, блок сравнения триггер, формирователь номера цикла, элемент И и блок управления, первый выход которого- подключен к первому входу триггера, первый выход которого подключен к первому входу элемента И, выход которого подключен к первому входу блока управления, а второй вход элемента И соединен с первым выходом формирователя номера цикла, вход которого подключен к выходу сумматора, а второй выход формирователя номера цикла является первым выходом устройства и. соединен с первыми входами переключателя и блока сравнения, выход которого подключен к второму триггера, второй выход которого подключен к второму входу переключателя, выход которого подключен к первому входу блока адресации, выход которого подключен к входу блока задания констант, выход которого подключен к первому входу блока умножения, выход которого является вторым выходом устройства, вход счетчика является первым входом устройства, вход регистра является вторым входом устройства, выход регистра соединен с вторь1М входом блока сравнения, введены группа элементов И, генератор кода Грея, регистр сдвига, циклический регистр сдвига и блок формирования знака, выход которого подключен к второму входу блока умножения, а вход блока формирования знака соединен с первым входом регистра сдвига и первым выходом генератора кода Грея, второй и- третий выходы которого подключены соответственно к первому и второму входам сумматора, а вход генератора кода Грея соединен с выходом счетчика, второй вход блока адресации объединён с вторым входом блока управления и подключен к выходам группы элементов И, входы которых подключены к первому выходу регистра сдвига, второй выход которого подключен к третьему входу блока адресации четвертый вход которого соединен с выходом циклического регистра сдвига первый вход которого подключен к второму входу регистра сдвига и второму выходу блока управления, а второй вход циклического регистра сдвига соединен с третьим выходом блока управления..

Кроме того, блок управления содержит четьаре элемента И, делитель частоты, генератор импульсов, регист сдвига и одновибратор., выходы которого соединены с первыми входами трех элементов И и -тактовым входом регистра сдвига, первый и второй выходы которого .соединены с вторыми входами соответственно первого и второго элементов И, выходы которы с являются соответственно первым и третьим

выходами блока управления, первый и второй входы четвертого элемента И являются соответственно первым и вторым входами блока управления, а выход четвертого элемента И соединен с вторым входом третьего элемента И, выход которого подключен к входу делителя частоты, выход которого является вторым выходом блока управления а входы регистра сдвига и одновибратора объединены и являются управляющим входом устройства.

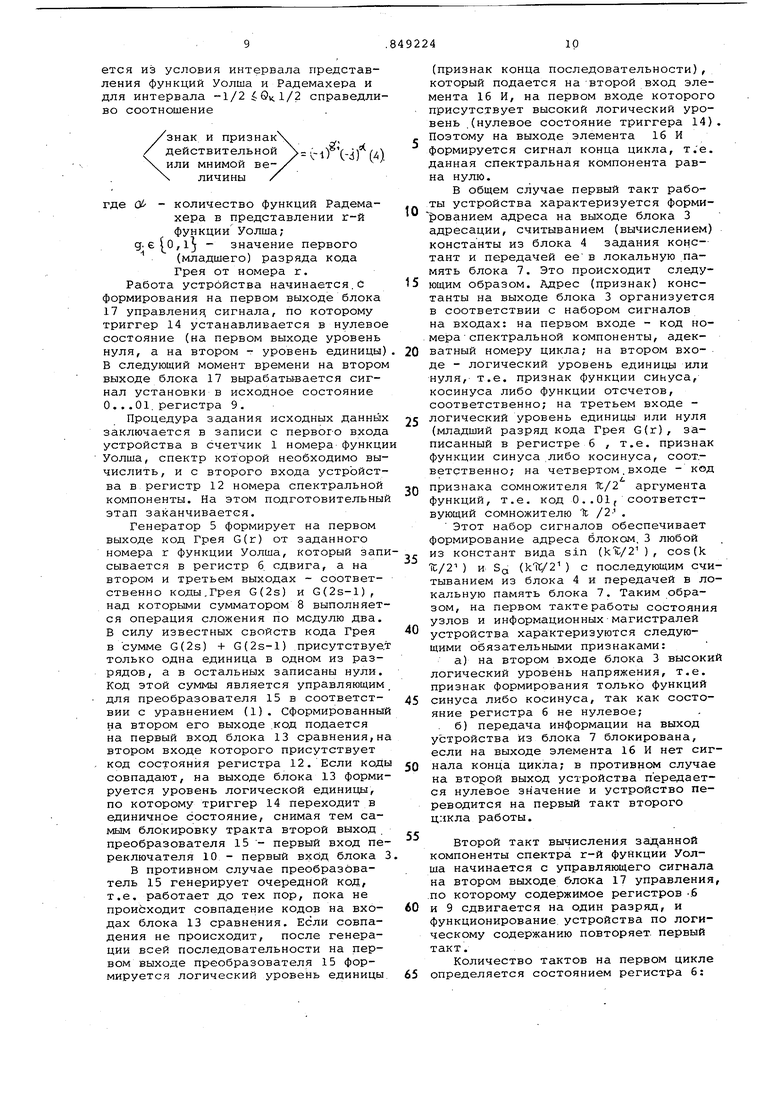

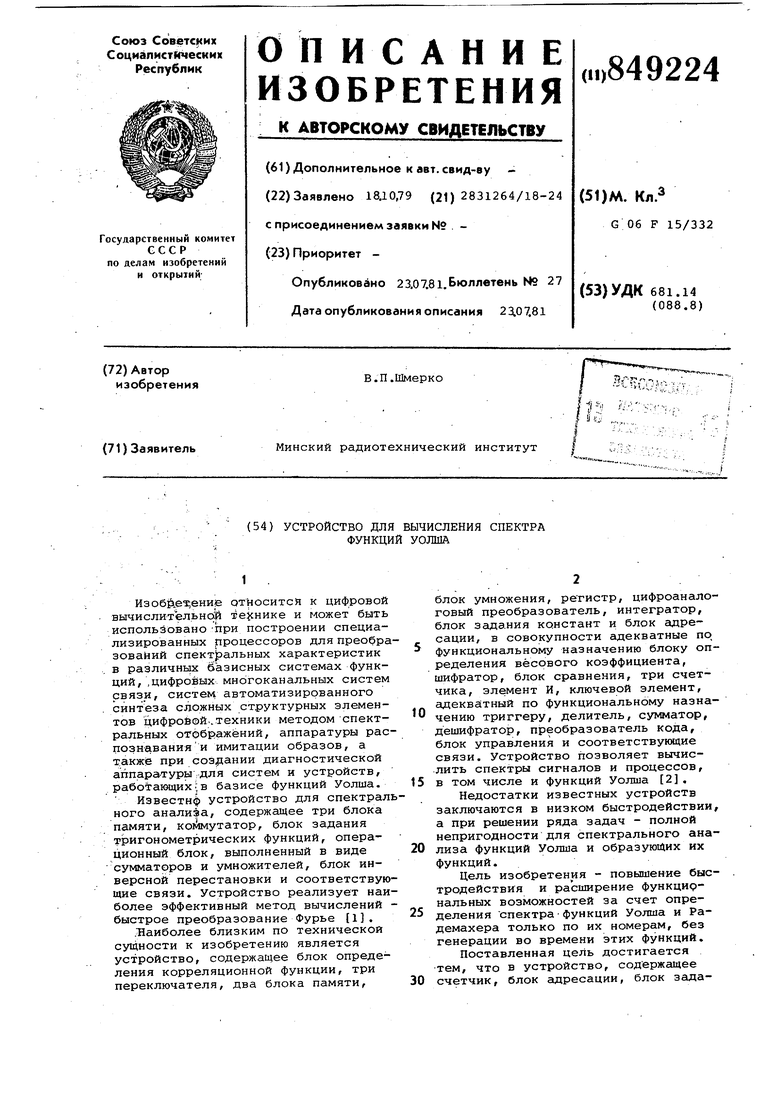

На фигЛ представлена структурная схема устройства; на фиг.2 - структурная схема блока управления.

Устройство содержит счетчик 1, группу 2 элементов И, блок 3 адресации, блок 4 задания констант, генератор 5 кода Грея, регистр б сдвига, блок 7 умножения, сумматор 8, циклический регистр-9 сдвига, переключатель 10, логический блок 11, регистр 12, блок 13 сравнения, триггер 14, преобразователь 15 кода элемент 16 И и блок 17 управления.

Счетчик 1 предназначен для приема с первого входа устройства начального номера ,2,. .. ,N-1 функции Уолша, спектр которой необходимо вычислить, и наращивания этого номера в естественном порядке (вычисление спектра для тривиального случая wal(0,x) в устройстве не предусмотрено).

Группа 2 элементов И предназначена для анализа на нуль состояния регистра б сдвига и формирования тем самым признака функции синуса, косинуса .(логический уровень единицы) или функции отсчетов (sin х)/х (логический уровень нуля).

Блок 3 адресации предназначен для формирования адреса (в общем случаепризнака) требуемой в процессе вычислений константы (значения функции) . На первый его вход подается код , 2,. .. ,N-1 номера спектральной компоненты, адекватного номеру цикла работы-устройства. На второй вход подается одноразрядный признак функции синуса, косинуса (логический уровень единицы) или функции отсчетов (логическк й уровень нуля) . На третий вход подается одноразрядный признак функции синуса (логический уровень единицы) или косинуса (логический уровень нуля). На четвертый вход подаемся код признака сомножителя Те/2 аргумента функций, где ie l, 2,..., ,j N} , причем кодировка осуществляется по принципу . 0..., 0...010-fK/4, 0...0100- ЙС/8 и т.д.

Блок 4 задания констант предназначен для хранения или формирования (в зависимости от конструкции) значений функций sin(kTC/2 ) , cos (k1ir/2 ) , (81пЧ-Л (з1п kTC/s )/(kV2i )Sa(k.it/2) , ,2,.. .m, .N.

Генератор 5 кода Грея предназначен для формирования на первом ,выходе кода Грея G(r) от числа г; на втором выходе-кода Грея G(2s) от числа 2; на третьем выходе - G(2s-1) для г-четных, - для г- нечетных чисел.

На вход генератора 5 кода Грея пЬдается двоичный кЗД г б (l, 2,.. ,. ,N-1 номера функции Уолша. Конструктивно генератор может быть выполнен по любому из известных методов преобразования двоичного кода в код -Грея.

Блок 7 умножения предназначен для выполнения последовательного перемножения операндов, поступающих на первый вход. Знак полученного произйедения корректируется (присваивается) в соответствиис сигналом на втором входе. Результат на выходе может сопровождаться одноразрядным признаком действительной кли мнимой величины.

Сумматор 8 предназначен для йыполнения операции сложения по модулю два операндов,. поступающих на первый и второй входы, т.е. G(2S)+G(2S-1) , и управления работой преобразователя 15 кода.

Циклический регистр.9 сдвига предназначен для задания сомножителя iC/2 аргумента функций в соответстви с тактом работы устройства путем циклического сдвига единицы. На первый вход регистра подается сигнал сдвига в сторону старших разрядов. По второму входу организована начальная установка кода 0...01, а с выхода снимается параллельный код состояния.

Переключатель 10 обеспечивает передачу информации с первого входа на выход при разрешающем уровне напряжения на втором входе (логический уровень единицы) и блокирует этот тракт при низком логическом уровне напряжения на втором входе.

Блок 11 предназначен для формирования знака и признака действительной или мнимой величины (в общем. случае двухразрядный код на выходе) путем анализа количества функций Радемахера, образующих данную функцию Уолша. Логическая функция, выполняемая блоком, зависит от интервала представления функции Уолша..

Регистр 12 предназначен для приема с второго входа устройства номера ke 1,2,.. . ,N-1 вычисляемой спектральной компоненты соответствующей функции Уолша.

Блок 13 сравнения предназначен для формирования сигнала совпадения (логический уровень единицы) или несовпадения (логический уровень нуля) кодов, поступающих на первый и второй его входы.

Триггер 14 предназначен для формирования управляющих сигналов для переключателя 10 и элемента 16 И,

соответственно на втором и первом выходах. По первому входу триггер 14 устанавливается в исходное нулевое состояние (высокий логический уровень напряжения на первом выходе), а второй вход является установочным.

Формирователь 15 предназначен для

формирования кода номера цикла ke{l,

2,...,N-1 работы устройства и имеет

особенности функционирования и конструктивных решений.

0

Элемент 16 И предназначен для формирования сигнала йрерывания вычислений в случае, если на его входах присутствуют высокие логические уровни -напряжения, т.е. вычисления

5 прерываются на данном цикле, если спектральная компонента с номером, равным номеру цикла, равна нулю.

Блок 17 управления предназначен

для синхронизации во времени струн-

0 турных элементов .устройства. По..входу, являющемуся управляющим, задается признак конца вычислений (высокий логический уровень напряжения),т.е. прерывание работы устройства на дан5ном цикле и переход на следующий цикл. Первый, второй и третий выходы являются импульсными, по которым организуется передача одиночных или групп импульсов в соответствии с законами функционирования структурных

0 элементов .устройства. Одиночные импульсные сигналы с первого и третьего выходов предшествуют началу каждого цикла работы устройства, обеспечивая установку исходных состояний

5 триггера 14 и циклического регистра 9 сдвига. На второй выход блока 17 управления, выдаются тактирующие импульсныесигналы, соответствующие тактам работы устройства с номерами

0 в естественном-порядке.

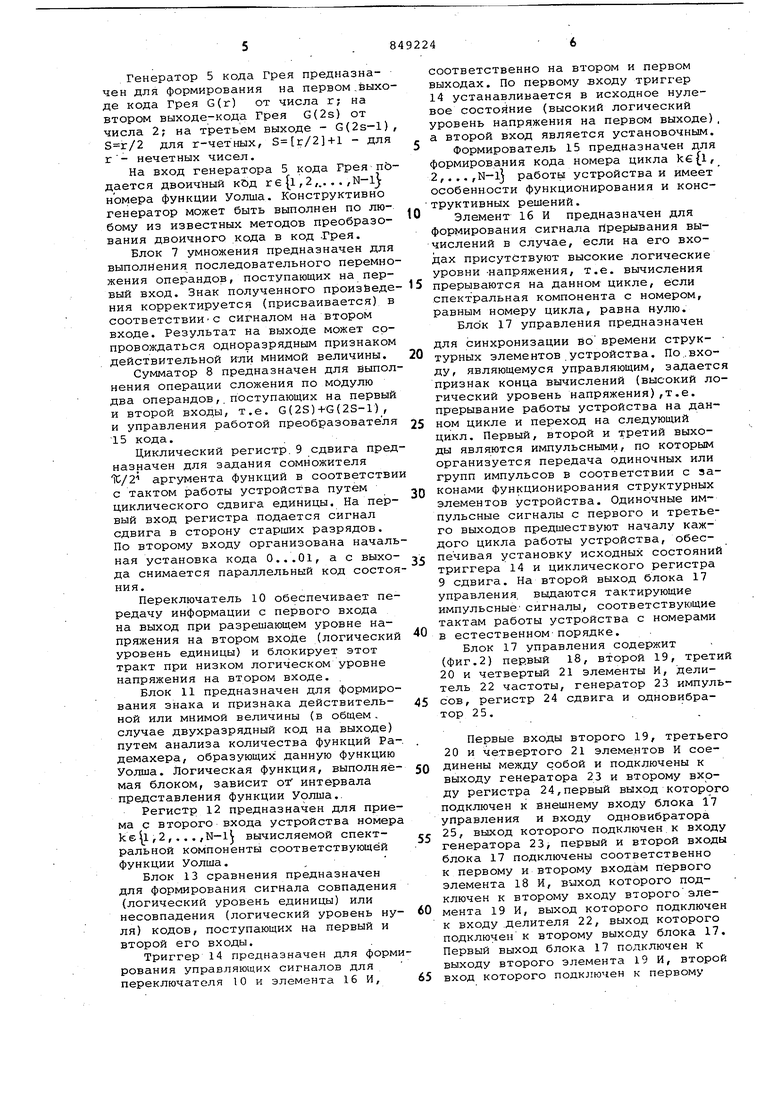

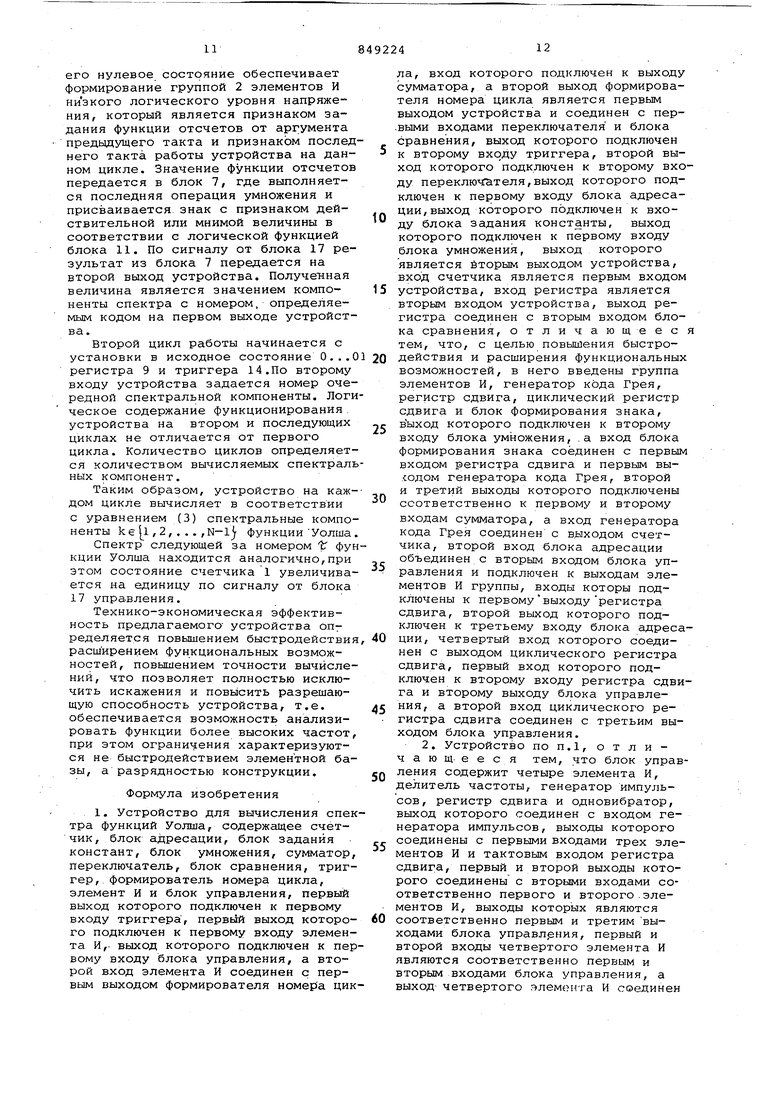

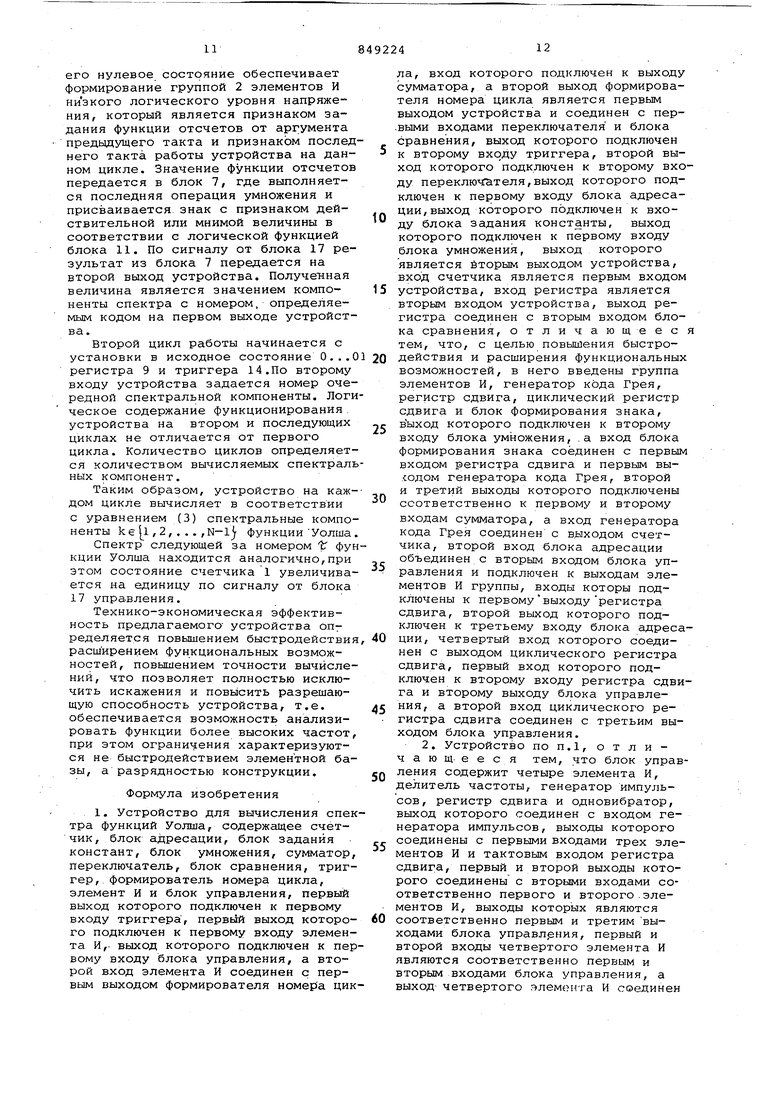

Блок 17 управления содержит (фиг.2) первый 18, второй 19, третий 20 и четвертый 21 элементы И, делитель 22 частоты, генер.атор 23 импульсов, регистр 24 сдвига и одновибра5тор 25.

Первые входы второго 19, третьего 20 и четвертого 21 элементов И соединены между собой и подключены к

0 выходу генератора 23 и второму входу регистра 24,первый выход которого подключен к внешнему входу блока 17 управления и входу одновибратора 25, выход которого подключен к входу

5 генератора 23, первый и второй входы блока 17 подключены соответственно к первому и второму входам первого элемента 18 И, виход которого подключен к второму входу второго эле0мента 19 И, выход которого подключен к входу делителя 22, выход которого подключен к второму выходу блока 17. Первый выход блока 17 подключен к выходу второго элемента 19 И, второй

5 вход которого подключен к первому

выходу регистра 24, второй выход которого подключен к второму входу третьего элемента 20 И, выход которого подключен к третьему входу блока 17 .

Первый элемент 18 И предназначен для формирования сигнала прерывания работы блока 17 управления путем осуществления операции конъюнкции над сигналами прерывания вычислений и конца цикла. Второй элемент 19 И предназначен для управления передачей импульсных сигналов на второй выход блока 17. Третий 20 и четвертый 21 элементы И предназначены для формирования одиночных сигналов на первом и третьем выходах блока 17.

Делитель 22 частоты предназначен для формирования последовательности импульсов с периодом, равным времени выполнения операций блоками устройства в течение одного такта.

Генератор 23 импульсов обеспечивает формирование последовательности импульсных сигналов.

Регистр 24 сдвига предназначен для управления работой третьего 20 и четвертого 21 элементов И. По первому входу осуществляется запись единицы в младший разряд, а по второму входу - сдвиг информации в регистре.

Одновибратор 25 предназначен для задержки внешнего пускового сигнала при запуске генератора 23 импульсов

Блок управления работает следующим образом.

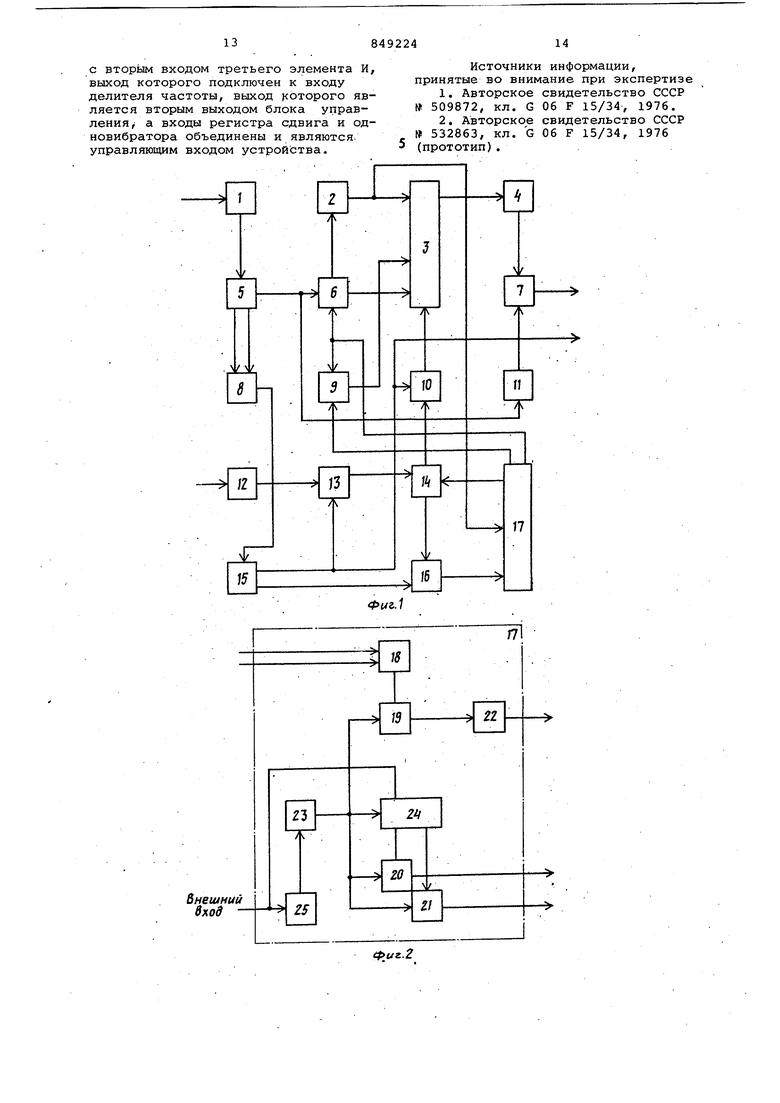

По внешнему пусковому сигналу в момент времени t (фиг.З) в младший разряд регистра 24 сдвига записывается единица и через время At одновибратор 25 запускает генератор 23 импульсов. Первый импульс с выхода генератора 23 передается на первь1й выход блока 17 управления (t/j) , так как на первом выходе регистра 24 присутствует логический уровень единицы, а на втором выходе - логический .уровень нуля. Этот же импульсный сигнал сдвигает единицу на один разряд в регистре 24. Следующий, импульс формируемый генератором 23, передается на третий выход блока 17 (t) и освобождает регистр 24 от информации При наличии разрешающих уровней напряжения на первом и втором входах блока 17 тракт передачи сигналов с выхода генератора 23 на второй выход блока 17 открыт, а делитель 22 частоты обеспечивает требуемую частоту формирования на втором выходе сигналов () .

Блокировка передачи сигналов на второй выход может быть осуществлена по любому из низких уровней напряжения на первом или втором входах бло|ка 17 (t,tg). Очередной цикл работй блока 17 выполняется аналогично (t-j,

tg ) .

Преобразователь 15 кода содержит m() схем преобразования, каждая из которых обеспечивает формирование последовательности кодов на выходе несоответствии с формулой

(2Z-1) ,2,... , jef.2,3,... m+l},(1)

где j - номер разряда входного двоичного кода, адекватный номеру- схемы в преобразователе, в котором записана единица.

Выбор схемы преобразования осуществляется т-разрядным управляющим кодом на входе.

После формирования всей последовательности на первый выход выдается сигнал конца последовательности (высокий логический уровень).

Преобразователь 15 может быть выполнен в виде комбинационных схем, синтезированных по известным методам конечных автоматов или в виде вычислительных устройств, микропрограмма которых реализует уравнение (1) .

ч в,основу работы устройства положены следующие-математические соот.ношения. Любую функцию Уолша wal(r, х) можно, представить в виде произведения функций Радемахера

waL(r,x),n R. (x)g , где R; (х) cos- C- , - функция Радемахет -1

ра ;

д --i-ый разряд кода Грея от номера г функции Уолша. Спектр S-й функции Радемахера равен ,2,. .. ,т .

F { R, Сх)} -3 sin II S, II П cosf ,

-- (2) 0 где ,2,...,N-1;

Sg - символ функции отсчетов (sin К)/2.

Выражение (2) имеет особый случай 5 при , для которого знак произведения изменяется на противоположный. Спектр г-й функции Уолша определяется как свертка спектров соответствующий функций Радемахера на основа0 НИИ (2)

/знак и признаку

.еср,ч) ( действительной ).

ИЛИ мнимой ве-/

-(3) личины /.-,

SmH

ICltVSm-l иЦ ).|П GOS Т-г-1|П sm-:-)

: /V;.s 2V

где S - максимальный номер функции Радемахера в структуре данной функции yojnua;

S - разность Z-S множества ,2,.. . ,ml и номеров S функций Радемахера из структуры г-й функции Уолша.

Знак и признак действительной или мнимой величины в (3) определяется из условия интервала представления функций Уолша и Радемахера и для интервала .l/2 справедливо соотношение

знак и признакХ

-Д

действительной -i) (-J) //,) или мнимой ве-./ личины /

где 0 - количество функций Радемахера в представлении г-й функции Уолша;

д. ,1 - значение первого (младшего) разряда кода Грея от номера г. Работа устройства начинается.С формирования на первом выходе блока 17 управления; сигнала, по которому триггер 14 устанавливается в нулевое состояние (на первом выходе уровень нуля, а на втором - уровень единицы) В следующий момент времени на втором выходе блока 17 вырабатн-вается сигнал установки в исходное состояние 0. ..01. регистра 9.

Процедура задания исходных данных заключается в записи с первого входа устройства в счетчик 1 номера функци Уолша, спектр которой необходимо вычислить, и с второго входа устройства в регистр 12 номера спектральной компоненты. На этом подготовительный этап заканчивается.

Генератор 5 формирует на первом выходе код Грея G(r) от заданного номера г функции Уолша, Который записывается в регистр 6 сдвига, а на втором и третьем выходах - соответственно коды.Грея G(2s) и G(2s-l), над которыми сумматором 8 выполняется операция сложения по модулю два. В силу известных свойств кода Грея в сумме G(2s) + G(2s-l) присутствует только одна единица в одном из разрядов, а в остальных записаны нули. Код этой суммы является управляющим для преобразователя 15 в соответствии с уравнением (1). Сформированный на втором его выходе .код подается на первый вход блока 13 сравнения,на втором входе которого присутствует код состояния регистра 12. Если коды совпадают, на выходе блока 13 формируется уровень логической единицы, по которому триггер 14 переходит в единичное состояние, снимая тем самьом блокировку тракта второй выход преобразователя 15 - первый вход переключателя 10 - первый вход блока 3

В противном случае преобразователь 15 генерирует очередной код, т.е. работает др тех пор, пока не происходит совпадение кодов на входах блока 13 сравнения. Если совпадения не происходит, после генерации всей последовательности на первом выходе преобразователя 15 формируется логический уровень единицы.

(признак конца последовательности), который подается на второй вход элемента 16 И, на первом входе которого присутствует высокий логический уровень .(нулевое состояние триггера 14). Поэтому на выходе элемента 16 И формируется сигнал конца цикла, т.е. данная спектральная компонента равна нулю.

В общем случае первый такт работы устройства характеризуется форми0рованием адреса на выходе блока 3 адресации, считыванием (вычислением) константы из блока 4 задания констант и передачей еев локальную память блока 7. Это происходит следу5ющим образом. Адрес (признак) константы на выходе блока 3 организуется в соответствии с набором сигналов на входах: на первом входе - код номера спектральной компоненты, адек0ватный номеру цикла; на втором входе - логический уровень единицы или нуля, т.е. признак функции синуса, косинуса либо функции отсчетов, соответственно; на третьем входе логический уровень единицы или нуля

5 (младший разряд кода Грея G(r), записанный в регистре 6 , т.е. признак функции синуса либо косинуса, соответственно; на четвертом.входе - код признака сомножителя 1С/2 аргумента

0 функций, т.е. код О .. 01, соответствующий сомножителю 1с /2- .

Этот набор сигналов обеспечивает формирование адреса блоком, 3 любой из констант вида sin (kiC/2 ), cos(k

5 iC/2 ) и Sg (kTt/2 ) с последующим считыванием из блока 4 и передачей в локальную память блока 7. Таким образом, на первом такте работы состояния узлов и информационных магистралей

0 устройства характеризуются следующими обязательными признаками:

а)на втором входе блока 3 высокий логический уровень напряжения, т.е. признак формирования только функций синуса либо косинуса, так как состо5яние регистра б не нулевое;

б)передача информации на выход устройства из блока 7 блокирована, если на выходе элемента 16 И нет сиг0нала конца цикла; в противном случае на второй выход устройства передается нулевое значение и устройство переводится на первый такт второго цикла работы.

5

Второй такт вычисления задранной компоненты спектра г-й функции Уолша начинается с управляющего сигнала на втором выходе блока 17 управления, по которому содержимое регистров -,6

0 и 9 сдвигается на один разряд, и функционирование устройства по логическому содержанию повторяет первый такт.

Количество тактов на первом цикле определяется состоянием регистра 6:

5 его нулевое состояние обеспечивает формирование группой 2 элементов И низкого логического уровня напряжения, который является признаком задания функции отсчетов от аргумента предыдущего такта и признаком послед него такта работы устройства на данном цикле. Значение функции отсчетов передается в блок 7, где выполняется последняя операция умножения и присваивается знак с признаком действительной или мнимой величины в соответствии с логической функцией блока 11. По сигналу от блока 17 результат из блока 7 передается на второй выход устройства. Полученная величина является значением компоненты спектра с номером, определяемым кодом на первом выходе устройства. Второй цикл работы начинается с установки в исходное состояние О... регистра 9 и триггера 14.По второму входу устройства задается номер очередной спектральной компоненты. Логи ческое содержание функционирования устройства на втором и последующих циклах не отличается от первого цикла. Количество циклов определяется количеством вычисляемых спектраль ных компонент. Таким образом, устройство на каждом цикле вычисляет в соответствии с уравнением (3) спектральные компо ненты ,2, . .. ,N-1} функцииУолша Спектр следующей за номером t фу кции Уолша находится аналогично,при этом состояние счетчика 1 увеличива ется на единицу по сигналу от блока 17 управления. Технико-экономическая эффективность предлагаемого- устройства определяется повышением быстродействи расширением функциональных возможностей, повышением точности вычислений, что позволяет полностью исключить искажения и повысить разрешающую способность устройства, т.е. обеспечивается возможность анализировать функции более высоких частот при этом ограничения характеризуются не быстродействием элементной базы, а разрядностью конструкции. Формула изобретения 1. Устройство для вычисления спек тра функций Уолша, содержащее счетчик, блок адресации, блок задания констант, блок умножения, сумматор переключатель, блок сравнения, триггер, формирователь номера цикла, элемент И и блок управления, первый выход которого подключен к первому входу триггера, первый выход которого подключен к первому входу элемента И,, выход которого подключен к пер вому входу блока управления, а второй вход элемента И соединен с первым выходом формирователя номерка цик ла, вход которого подключен к выходу сумматора, а второй выход формирователя номера цикла является первым выходом устройства и соединен с пер.выми входами переключателя и блока сравнения, выход которого подключен к второму входу триггера, второй выход которого подключен к второму входу переключ:ателя,выход которого подключен к первому входу блока адресации, выход которого подключен к входу блока задания константы, выход которого подключен к первому входу блока умножения, выход которого является йторым выходом устройства, вход счетчика является первым входом устройства, вход регистра является вторым входом устройства, выход регистра соединен с вторым входом блока сравнения, отличающеес я тем, что, с целью повышения быстродействия и расширения функциональных возможностей, в него введены группа элементов И, генератор кода Грея, регистр сдвига, циклический регистр сдвига и блок формирования знака, выход которого подключен к второму входу блока умножения, .а вход блока формирования знака соединен с первым входом регистра сдвига и первым вы.содом генератора кода Грея, второй и третий выходы которого подключены соответственно к первому и второму входам сумматора, а вход генератора кода Грея соединен с в лxoдoм счетчика, второй вход блока адресации объединен с вторьлм входом блока управления и подключен к выходам элементов И группы, входы которы подключены к первомувыходурегистра сдвига, второй выход которого подключен к третьему входу блока адресации, четвертый вход которого соединен с выходом циклического регистра сдвига, первый вход которого подключен к второму входу регистра сдвига и второму выходу блока управления, а второй вход циклического регистра сдвига соединен с третьим выходом блока управления. 2. Устройство ПОП.1, отличаю щ- ее ся тем, что блок управления содержит четыре элемента И, делитель частоты, генератор импульсов, регистр сдвига и одновибратор, выход которого соединен с входом генератора импульсов, выходы которого соединены с первыми входами трех элементов И и тактовым входом регистра сдвига, первый и второй выходы которого соединены с вторыми входами соответственно первого и второго.элементов И, выходы которых являются соответственно первым и третим выходами блока управл.ения, первый и второй входы четвертого элемента И являются соответственно первым и вторым входами блока управления, а выход- четвертого элемента И соединен

с вторым входом третьего элемента И, вьоход которого подключен к входу делителя частоты, выход )оторого является вторым выходом блока управления / а входы регистра сдвига и одновибратора объединены и являются, управляющим входом устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 509872, кл. G 06 F 15/34, 1976,

2.Авторское свидетельство СССР 532863, кл, G 06 F 15/34, 1976 (прототип).

Внешний вход

фиг..2

вияодЗ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления спектра уолша функций синуса и косинуса | 1979 |

|

SU864291A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU842829A1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| Устройство для преобразования по функциям Уолша | 1986 |

|

SU1383393A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1137479A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1129619A2 |

| Устройство для формирования сложныхСигНАлОВ | 1979 |

|

SU817994A1 |

| Устройство для спектральногоАНАлизА | 1978 |

|

SU813286A1 |

| Устройство для спектрального анализа | 1978 |

|

SU767774A1 |

Stfxo92

Авторы

Даты

1981-07-23—Публикация

1979-10-18—Подача