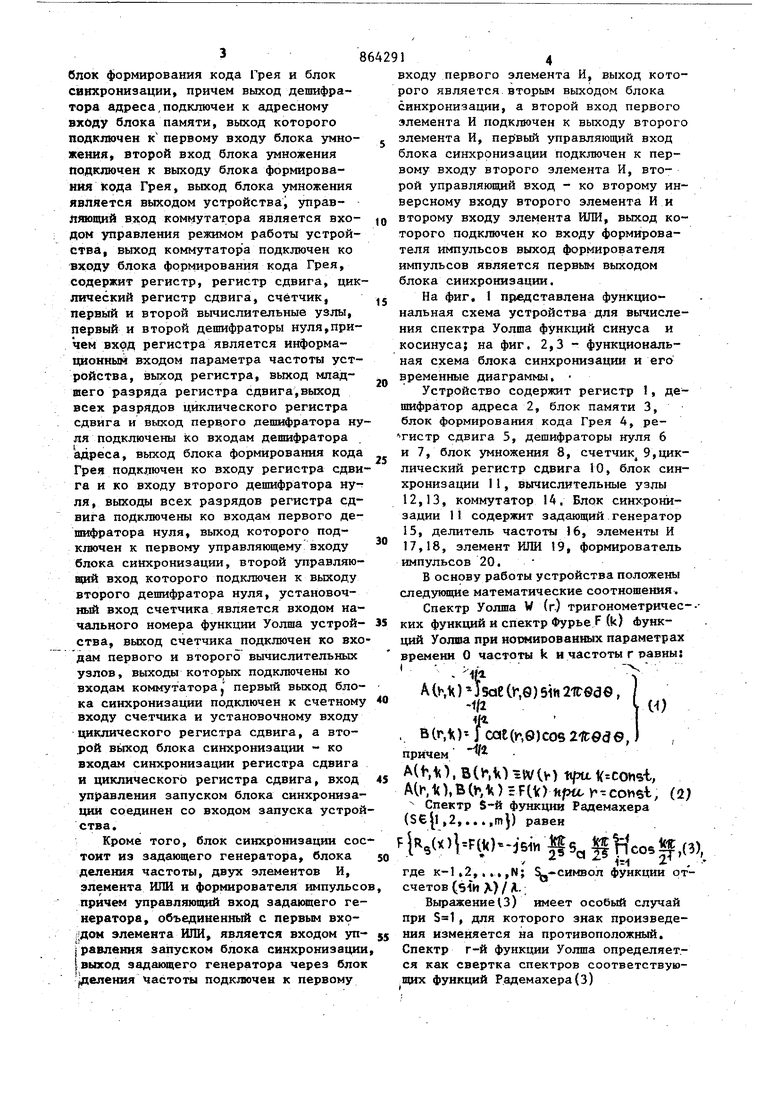

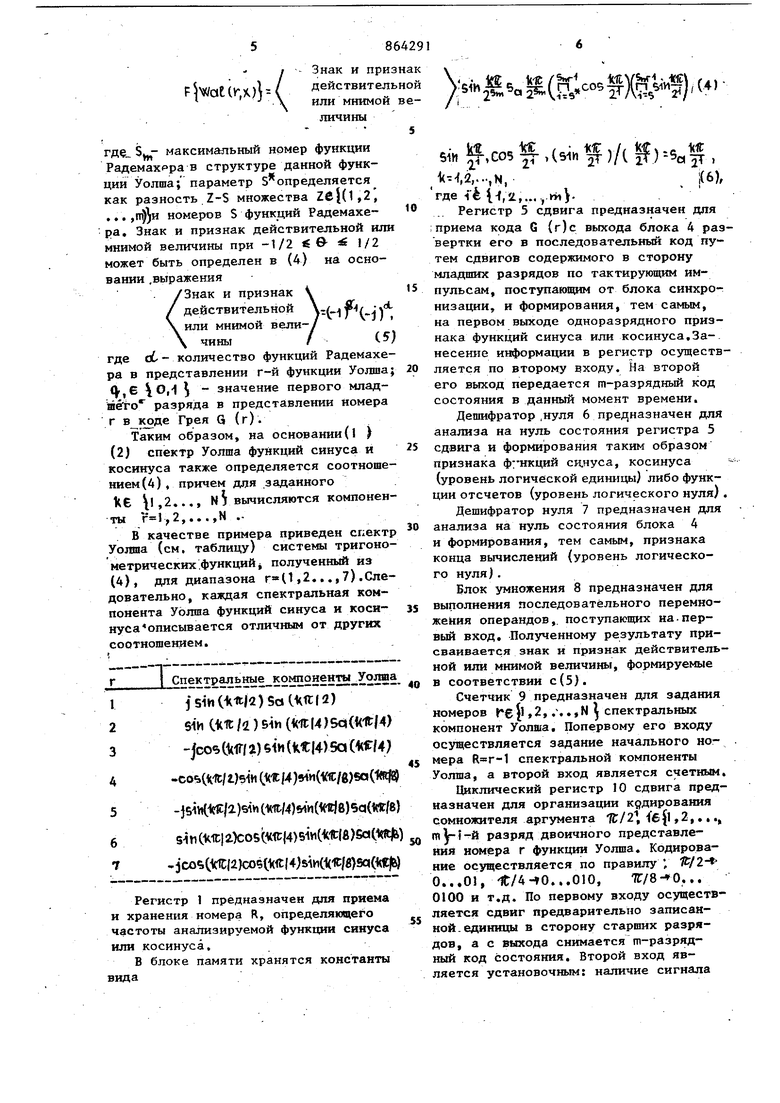

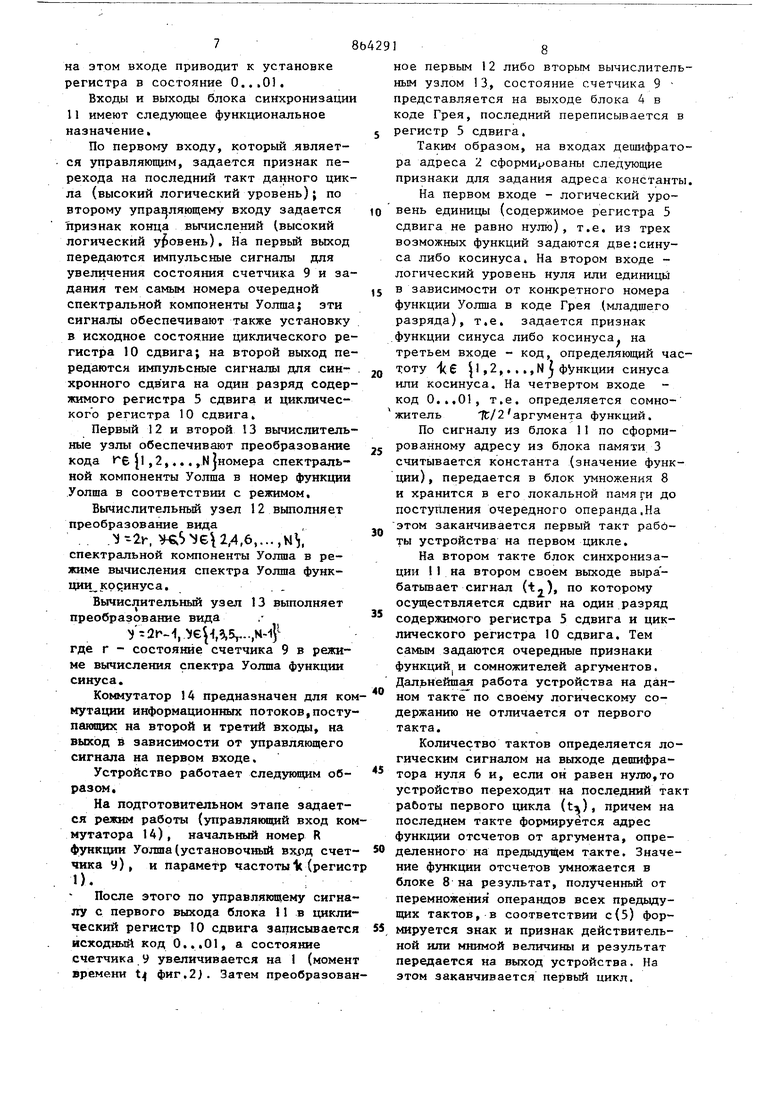

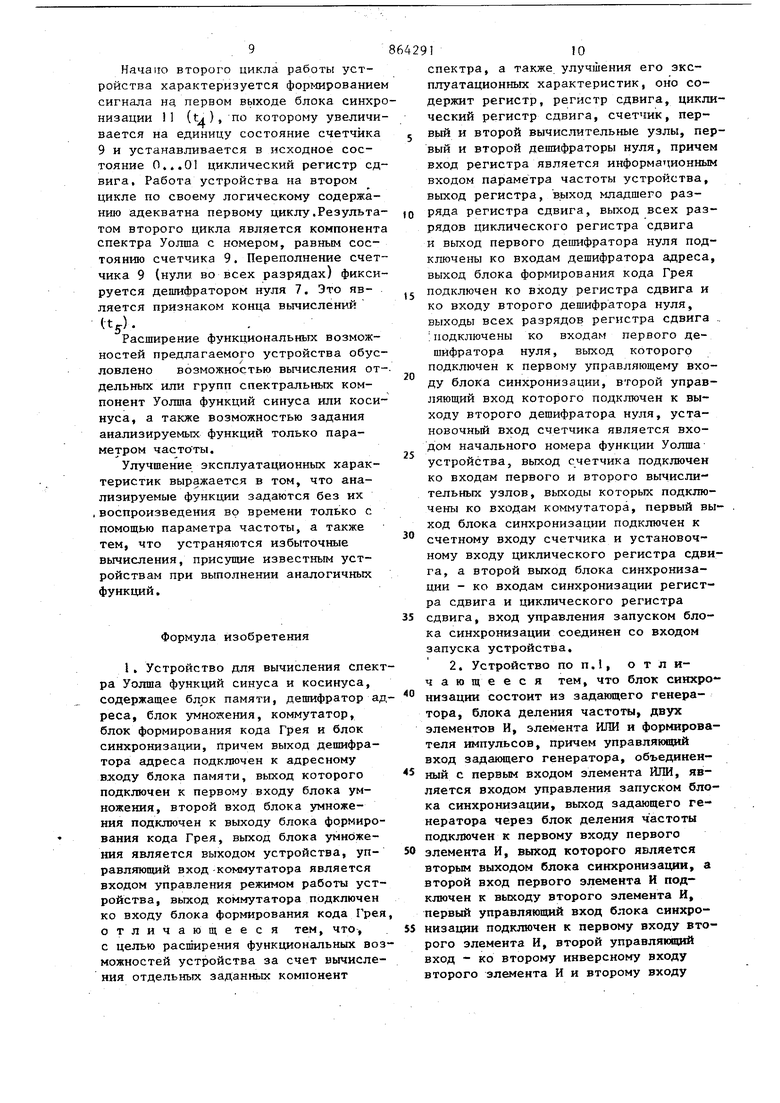

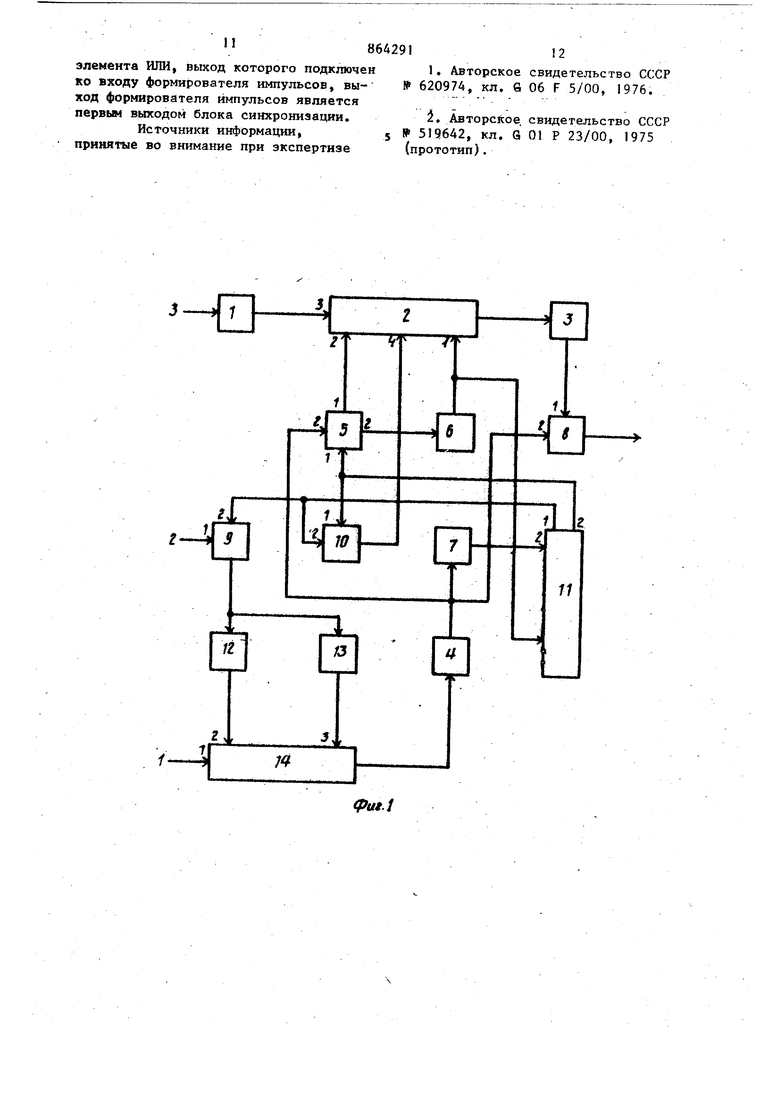

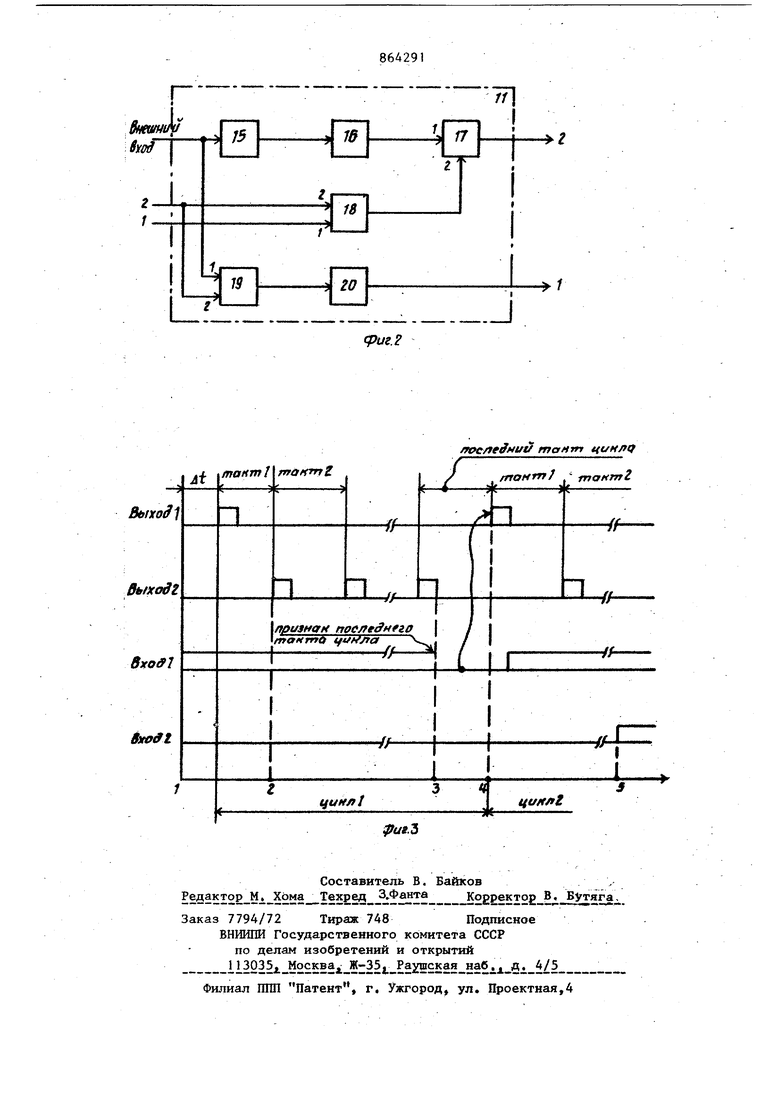

(54)УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СПЕКТРА У.ОЛША ФУЖЦИЙ СИНУСА И КОСИНУСА Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении специализированных процессоров для преобразований спектральных характеристи в различных базисных системах функ1Ц1Й, цифровых многоканальных систем связи, систем автоматизированного син теза сложных структурных элементов цифровой техники методом спектральных отображений, аппаратуры распознавания и имитации образоВ; а также при создании диагностической аппаратуры для систем и устройств, работающих в базисе функций Уолта. Известно устройство для вычисления спектра Уолша, содержащее сумматоры-вычитатели н регистры сдвига р Наиболее близким к предлагаемому является устройство для вычисления спектра Уолша функций синуса и косинуса, содержащее блок памяти, дешифратор, блок умножения, коммутатор, блок формирования кода Грея, блок син-, хронизации, а также триггер 123., Однако эти устройства не позволяют вычислять отдельные, заданные своим номером компоненты спектра Уолша функций синуса и косинуса. Кроме того, обладая определенной универсальностью относительно анализируемые процессов и сигналов, эти устройства требуют избыточных преобразований для сигналов типа функций синуса и косинуса, что отражается на их эксплуатационных характеристиках(аппаратурные затраты, меньшая эффективность и т.д), Цель изобретения - расширение функциональных возможностей устройства за счет вычисления отдельных заданных компонент спектра, а также улучшение его эксплуатационных характеристик. Поставленная .цель достигается тем, что устройство для вычисления спектра Уолша функций синуса и косинуса, содержащее блок памяти, дешифратор адреса, блок умножения, коммутатор. блок формирования кода Грея и блок свихронизации, причем выход дешифратора адреса,подключен к адресному входу блока памяти, выход которого подключен к первому входу блока згмножения, второй вход блока умножения подключен к выходу блока формирования кода Грея, выход блока умножения является выходом устройства управЛяющий вход коммутатора является вхо- д дом управления режимом работы устройства, выход коммутатора подключен ко входу блока формирования кода Грея, содержит регистр, регистр сдвига, циклический регистр сдвига, счётчик, первый и второй вычислительные узлы, первый и второй дешифраторы нуля,причем вход регистра является информационный входом параметра частоты устройства, выход регистра, выход младшего разряда регистра сдвига,выход всех разрядов циклического регистра сдвига и вьпсод первого дешифратора ну ля подключены ко входам дешифратора адреса, выход блока формирования кода Грея подключен ко входу регистра сдви га и ко входу второго дешифратора ну- ля, выходы всех разрядов регистра сдвига подключены ко входам первого дешифратора нуля, выход которого подключен к первому управляющему входу блока синхронизации, второй управляющий вход которого подключен к выходу второго дешифратора нуля, установочный вход счетчика является входом начального номера функции Уолша устройства, выход счетчика подключен ко вхо дам первого и второго вычислительных узлов, выходы кото1)ых подключены ко входам коммутатора j первый выход блока синхронизации подключен к счетному входу счетчика и установочному входу циклического регистра сдвига, а второй вьпсод блока синхронизации ко входам синхронизации регистра сдвига и циклического регистра сдвига, вход управления запуском блока синхронизации соединен со входом запуска устрой ства. Кроме того, блок синхронизации сос тоит из задающего генератора, блока деления частоты, двух элементов И, элемента ИЛИ и формирователя импульсо причем управляющий вход задакяцего генератора, объединенный с первым вхо;;дом элемента или, является входом упIравлеиия запуском блока синхронизации I выход задающего генератора через блок деления частоты подключен к первому 8642 J 14 входу первого элемента И, выход которого является вторым выходом блока синхронизации, а второй вход первого элемента И подключен к выходу второго элемента И, первый управляющий вход блока синхронизации подключен к первому входу второго элемента И, второй управляющий вход - ко второму инверсному входу второго элемента И и второму входу элемента ИЛИ, выход которого подключен ко входу формирователя импульсов выход формирователя импульсов является первьм выходом блока синхронизации. На фиг. 1 представлена функциональная схема устройства для вычисления спектра Уолша функций синуса и косинуса; на фиг. 2,3 - функциональная схема блока синхронизации и его временные диаграммы, Устройство содержит регистр 1, дешифратор адреса 2, блок памяти 3, блок формирования кода Грея 4, реис тр сдвига 5, дешифраторы нуля 6 и 7, блок умножения 8, счетчик 9,циклический регистр сдвига 10, блок синхронизации I1, вычислительные узлы 12,13, коммутатор 14. Блок синхронизации П содержит задающий генератор 15, делитель частоты 16, элементы И 17,18, элемент ИЛИ 19, формирователь импульсов 20. В основу работы устройства положены следующие математические соотношения. Спектр Уолша W (г) тригонометричес- ких функций и спектр Фурье/ (k) Функций Уолша при нормированных параметрах времени О частоты k и частоты г равны: 4ггА (ЬД) JScsE tV,Q) 5i« 2rede, ,. В (гд)-. j cae (П0)COS aitea ©, причем А(Д ), 1(,41 rWlv) K COHsi, ACr.1(),B(,H)rF(V)ftf tty rcohei, (2) Спектр S-й функции Радемахера (S€| ,2,... ,mp равен KU)F(t).j5i« М5,,дЗ) где к-1,2,...,N; -символ функции отсчетов (51И Л) / ЛВыражение 13) имеет особый случай при , для которого знак произведе ия изменяется на противоположный. Спектр г-й функции Уолша определяет,ся как свертка спектров соответствующих функций Радемахера(З) Знак и признак F(/at(v,x,) действительной или мнимой ве личины где максимальный номер функции Радемахрра в структуре данной функции Уолша; параметр S определяется как разность Z-S множества Z6|(1,2, ... , номеров S функций Радемахера. Знак и признак действительной или мнимой величины при -1/2 & 1/2 может быть определен в (4) на основании .выражения . /Знак и признак Ч / действительной V( I I ИЛИ мнимой вели-/ чины / с) где об - количество функций Радемахера в представлении г-й функции Уолша; (е О,-1 значение первого младш го разряда в представлении номера г Грея G (г). Таким образом, на основании(1 ) (2) спектр Уолша функций синуса и косинуса также определяется соотношением (4) , причем для заданного Хе ,2..., N V вычисляются компоненты ,2,...,N.В качестве примера приведен спектр Уолша (см. таблицу) системы тригонометрических .фуикций получеиный из (4), для диапазона 2,. .,7) .Следовательно, каждая спектральная компонента Уолша функций синуса и косинуса описывается отличным от других соотношением. I Спектральные компоненты Уолша jSiH(k1t|2)Soi(.Vtt(2) sin UIC /2 ) 51И (1(11(4)50(1(1(4) -jco CldTfj) siM(kt|4)5a(if/4) .co.(4lc/iM« (1(1c|4)«n(ViC/e)ea(1«fe} - )s (H1t/4)«n(iff|8)5a(Wr/8} sitiOcic|i)co5(vic|4)(Vlt|e)SoiO«t)ti) .jCO Ck1C|2)c05CK t|4)5iK1(K;/8)Sq(WC(B) Регистр 1 предназначен для приема и хранения номера R, определяющего частоты анализируемой функции синуса или косинуса. В блоке памяти хранятся константы вида )() 5iH,COsf-,(s.nf )/().5«f. ,bi2..,N,), где i€ i-f/iL,... , m}. .. Регистр 5 сдвига предназначен для ;приема кода G (г)с выхода блока 4 развертки его в последовательный код путем сдвигов содержимого в сторону младших разрядов по тактирующим импульсам, поступаюпщм от блока синхронизации, и формирования, тем самьм, на первом выходе одноразрядного признака функций синуса или косинуса,За-несение информации в регистр осуществляется по второму входу. На второй его выход передается п-разрядный код состояния в данный момент времени. Дешифратор ,нуля 6 предназначен для анализа на нуль состояния регистра 5 сдвига и формирования таким образом признака фтнкций сцнуса, косинуса (уровень логической единицы) либо функции отсчетов (уровень логического нуля) . Дешифратор нуля 7 предназначен для анализа на нуль состояния блока 4 и формирования, тем самым, признака конца вычислений (уровень логического нуля). Блок умножения 8 предназначен для выполнения последовательного перемножения операндов,, поступающих на-первый вход. Полученному результату присваивается знак и признак действительной или мнимой величины, формируемые в соответствии с(5). Счетчик 9 предназначен для задания номеров С€| t2,.. .N I спектральиых компонент Уолша. Попервому его входу осуществляется задание начального номера спектральной компоненты Уолша, а второй вход является счетным. Циклический регистр 10 сдвига предназначен для организации кодирования сомножителя аргумента К/2 {б|1,2,..., mV-t-A разряд двоичного представления номера г функции Уолша. Кодирование осуществляется по правилу , 7Z/2- O...OJ, t/4- 0.,.010, ТГ/В-О... 0100 и т.д. По первому входу осуществяется сдвиг предварительно записанной, единицы в сторону старших разряов, а с выхода снимается т-разрядный код состояния. Второй вход явяется установочным: наличие сигнала к установке на этом входе приводит регистра в состояние О ...01. Входы и выходы блока синхронизации 11 имеют следующее функциональное назначение. По первому входу, который является управляющим, задается признак перехода на последний такт данного цик ла (высокий логический уровень); по второму управляющему входу задается признак конца вычислений (высокий логический уровень). На первьй выход передаются импульсные сигналы для увеличения состояния счетчика 9 и за дания тем самым номера очередной спектральной компоненты Уолша; зти сигналы обеспечивают также установку в исходное состояние циклического ре гистра 10 сдвига; на второй выход пе редаются импульсные сигналы для синхронного сдвига на один разряд содер жимого регистра 5 сдвига и циклического регистра 10 сдвига. Первый 12 и второй 13 вычислитель ные узлы обеспечивают преобразование кода е J1,2,..., N номера спектральной компоненты Уолша в номер функции Уолша в соответствии с режимом, Вычислительньй узел 12 выполняет преобразование вида .. ,4,6,...,l, спектральной компоненты Уолша в режиме вычисления спектра Уолша функции косинуса.. , Вычислительный узел 13 выполняет преобразование вида ,..,N-15 где г - состояние счетчика 9 в режиме вычисления спектра Уолша функции синуса. Коммутатор 14 предназначен для ко мутации информационных потоков,посту паницих на второй и третий входы, на выход в зависимости от управляющего сигнала на первом входе. Устройство работает следующим образом. На подготовительном этапе задается режим работы (управлякиций вход ко мутатора 14), начальный номер R функции Уолша(установочный вхрд счет чика у), и параметр частоты It (регис 1).: После этого по управляющему сигна лу с первого выхода блока I1 в цикли ческий регистр 10 сдвига записываетс исходный код 0...0, а состояние счетчика 9 увеличивается на 1 (момен времени t фиг.2). Затем преобразова 8 ов первым 12 либо вторым вычислительым узлом 13, состояние счетчика 9 редставляется на выходе блока 4 в коде Грея, последний переписывается в регистр 5 сдвига. Таким образом, на входах дешифратора адреса 2 сформированы следующие признаки для задания адреса константы. На первом входе - логический уровень единицы (содержимое регистра 5 сдвига не равно нулю), т.е. из трех возможных функций задаются две:синуса либо косинуса. На втором входе логический уровень куля или единицй в зависимости от конкретного номера функции Уолша в коде Грея (младшего разряда), т.е. задается признак функции синуса либо косинуса, на третьем входе - код, определяющий час- т.оту 1 1,2,...,NJ ФУНКЦИИ синуса или косинуса. На четвертом входе код О..,01, т.е. определяется сомножитель Tt/2аргумента функций. По сигналу из блока 11 по сформированному адресу из блока памяти 3 считывается константа (значение функции) , передается в блок умножения 8 и хранится в его локальной памя ги до поступления очередного операнда,На этом заканчивается первый такт рабйты устройства на первом цикле. На втором такте блок синхронизации i 1 на втором своем выходе вырабатьшает сигнал (t-), по которому осуществляется сдвиг на один разряд содержимого регистра 5 сдвига и циклического регистра 10 сдвига. Тем самым задаются очередные признаки функций И сомножителей аргументов. Дальнейшая работа устройства на данном такте по своему логическому содержанию не отличается от первого такта. Количество тактов определяется логическим сигналом на выходе дешифратора нуля 6 и, если он равен нулю,то устройство переходит на последний такт работы первого цикла (ц), причем на последнем такте формируется адрес функции отсчетов от аргумента, определенного на предьщущем такте. Значение функции отсчетов умножается в блоке 8 на результат, полученный от перемножения операндов всех предьздущих тактов, в соответствии с(5) формируется знак и признак действительной или мнимой величины и результат передается на выход устройства. На этом заканчивается первый цикл. Начано второго цикла работы устройства характеризуется формировани сигнала на первом выходе блока синх низации 11 (t), по которому увелич вается на единицу состояние счетчик 9 и устанавливается в исходное состояние 0...01 циклический регистр сд вига. Работа устройства на втором цикле по своему логическому содержа нию адекватна первому циклу.Результ том второго цикла является компонент спектра Уолша с номером, равным состоянию счетчика 9. Переполнение сче чика 9 (нули во всех разрядах) фикси руется дешифратором нуля 7. Это является признаком конца вычислений (ty) . Расширение функциональных возможностей предлагаемого устройства обус ловлено возможностью вычисления от дельных или групп спектральных компонент Уолша функций синуса или коси нуса, а также возможностью задания анализируемых функций только параметром частоты. Улучшение эксплуатационных характеристик выражается в том, что анализируемые функции задаются без их ,воспроизведения во времени только с помощью параметра частоты, а также тем, что устраняются избыточные вычисления, присущие известным устройствам при выполнении аналогичных функций. Формула изобретения I . Устройство для вычисления спек ра Уолша функгщй синуса и косинуса, содержащее блок памяти, дешифратор а реса, блок умножения, коммутатор, блок формирования кода Грея и блок синхронизации. Причем выход дешифратора адреса подключен к адресному входу блока памяти, выход которого подключен к первому входу блока умножения, второй вход блока умножения подключен к выходу блока формиро вания кода Грея, выход блока умножения является выходом устройства, управляющий вход коммутатора является входом управления режимом работы уст ройства, выход коммутатора подключен ко входу блока формирования кода Гре отличающееся тем, что-, с целью распшрения функциональных во можностей устройства за счет вычисле ния отдельных заданных компонент спектра, а также улучшения его зксплуатационных характеристик, оно содержит регистр, регистр сдвига, циклический регистр сдвига, счетчик, первый и второй вычислительные узлы, первый и второй дешифраторы нуля, причем вход регистра является информационным входом параметра частоты устройства, выход регистра, выход младшего разряда регистра сдвига, выход всех разрядов циклического регистра сдвига и выход первого дешифратора нуля подключены ко входам дешифратора адреса, выход блока формирования кода Грея подключен ко входу регистра сдвига и ко входу второго дешифратора нуля, выходы всех разрядов регистра сдвига .. :подключены ко входам первого дешифратора нуля, выход которого подключен к первому управляющему входу блока синхронизации, второй управляющий вход которого подключен к выходу второго дешифратора нуля, установочный вход счетчика является входом начального номера функции Уолша устройства, выход счетчика подключен ко входам первого и второго вычислительных узлов, выходы которых подключены ко входам коммутатора, первый выход блока синхронизации подключен к счетному входу счетчика и установочному входу циклического регистра сдвига, а второй выход блока синхронизации - ко входам синхронизации регистра сдвига и циклического регистра сдвига, вход управления запуском блока синхронизации соединен со входом запуска устройства. 2. Устройство по п.1| отличающееся тем, что блок синхронизации состоит из задающего генератора, блока деления частоты, двух элементов И, элемента ШШ и формирователя импульсов, причем управляющий вход задающего генератора, объединеи- ный с первым входом злемента ИЛИ, является входом управления запуском блока синхронизации, выход задающего генератора через блок деления частоты подключен к первому входу первого элемента И, выход которого является вторым выходом блока синхронизации, а торой вход первого элемента И подлючен к выходу второго элемента И, ервый управляющий вход блока синхроизации подключен к первому входу втоого элемента И, второй управляющий ход - ко второму инверсному входу торого элемента И и второму входу

элемента ИЛИ, выход которого подключен ко входу формирователя импульсов, выход формирователя импульсов является первым выходом блока синхронизации.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 620974, кл. 6 06 F 5/00, 1976.

И, Авторское, свидетельство СССР № 519642, кл. G 01 Р 23/00, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU842829A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Устройство для вычисления спектраМОщНОСТи | 1978 |

|

SU805191A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Цифровой генератор спектра фурье | 1973 |

|

SU446063A1 |

| Устройство для спектральногоАНАлизА | 1978 |

|

SU813286A1 |

| Цифровой анализатор спектра | 1978 |

|

SU734579A1 |

| Устройство для спектрального анализа | 1978 |

|

SU767774A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

tffut.i

/юс/tf Mui/ та ft т nuHflQ

Авторы

Даты

1981-09-15—Публикация

1979-12-17—Подача