Изобретение относится к автоматике и вычислительной технике, в частности к средствам виртуального контроля исправности цифровых логических устройств.

Известен логический пробник, содержащий буферный каскад, компараторы, формирователь, ключ, элемент И-НЕ и индикаторные лампы l .

Недостатками этого пробника являются большая условность индикации и невысокая достоверность получаемой информации.

Известен также двухпороговыи логический пробник, содержащий входной узел, компаратор верхнего уровня сигнала, компаратор нижнего уровня сигнала, формирователи, ключ, элемент И-НЕ, одновибратор и ТРИ сигнашьные-лампы 2 .

Недостатками этого устройства являются невысокие достоверность и информативность индикации.

Цель изобретения - поёышение достоверности и информативности индикации .

Поставленная цель достигается тем, что в двухпороговыи логический пробник, содержащий входной узел, &ХОД которого соединен со входом

устройства, компаратор верхнего уровня сигнала (КВУС), вход которого соединен с первым выходом входного узла, компаратор нижнего уровня сигнала (КНУС), вход которого соединен со вторым выходом входного узла, первый формирователь, второй формирователь, ключ, одновибратор индикации и элемент И-НЕ, введен анализа0тор импульсов, статический регистр, шифратор, одновибратор анализа,сегментный индикатор, обостритель импульсов запуска, коммутатор, причем первый вход анализатора импульсов

5 соединен с выходом компаратора верхнего уровня сигнала и первым входом коммутатора, второй вход анализатора импульсов соединен с выходом компаратора нижнего уровня сигнала и вторым

0 входом коммутатора, первый и второй выходы анализатора импульсов соединены соответственно с третьим и четвертым входами коммутатора, остальные выходы анализатора импульсов, за

5 исключением третьего, соединены с первыми информационными входами статического регистра, первые выходы которого соединены со -входами шифратора, первые выходы которого соеди0нены с пятым входом коммутатора,ВТО-.

рые выходы - с первыми сегментами сегментного индикатора, вторые сегменты которого соединены с выходами коммутатора, шестой вход которого соединен со вторым выходом статического регистра, а седьмой вход - со вторым информационным входом статического регистра, третьим выходом анализатора импульсов и первым контактом ключа, второй контакт которого соединен со входом контролируемого устройства, а переключающий контакт - со входом оеострителя импульсов запуска, выход которого соединен со входом одновибратора анализа, выход которого соединен со входом одновибратора индикации и входом второго формирователя, выход которог соединен с третьим входом анализатор импульсов и входом записи статического регистра, вход установки в исхо ное состояние которого соединен с выходом первого формирователя, вход которого соединен с выходом элемента -И-НЕ, первый вход которого соединен с выходом одновибратора индикации и восьмым входом коммутатора, а второй вход - с выходом одновибратора анализа.

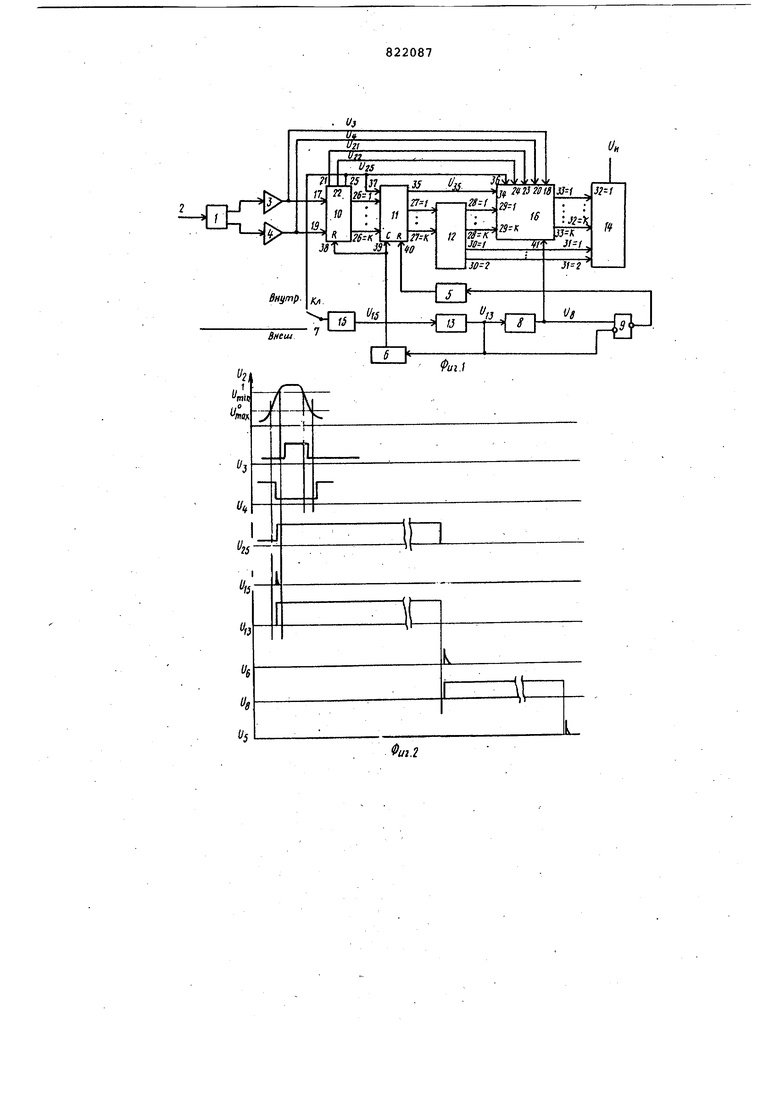

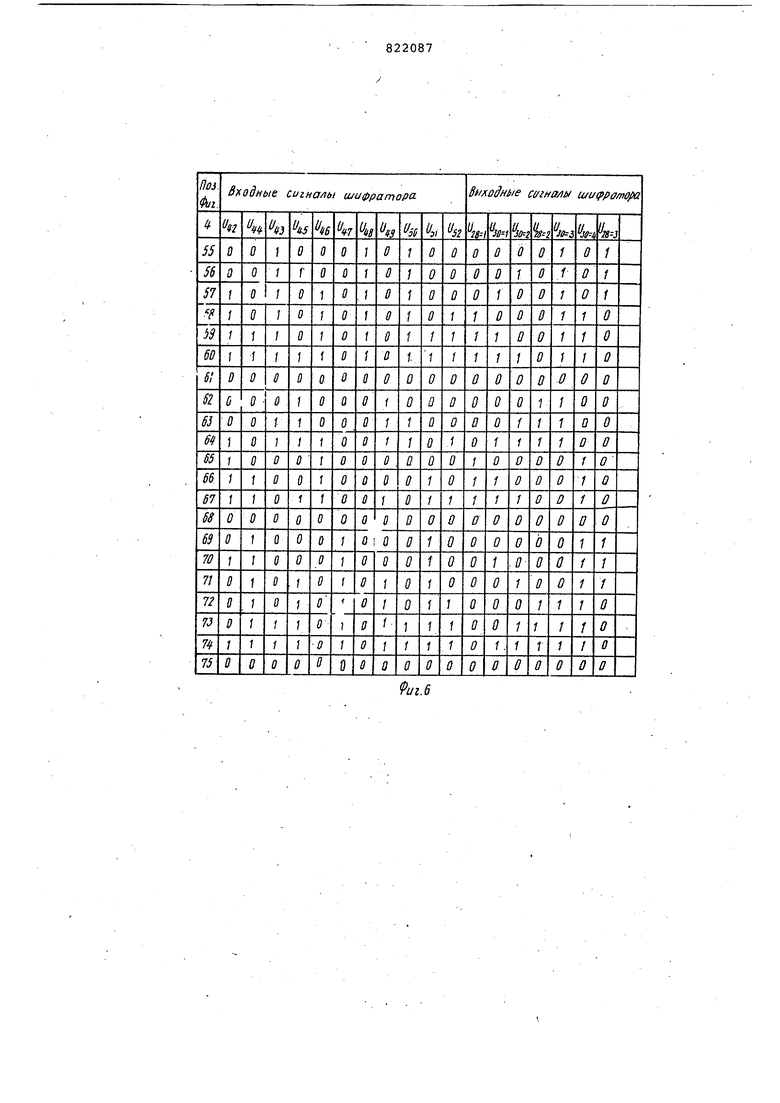

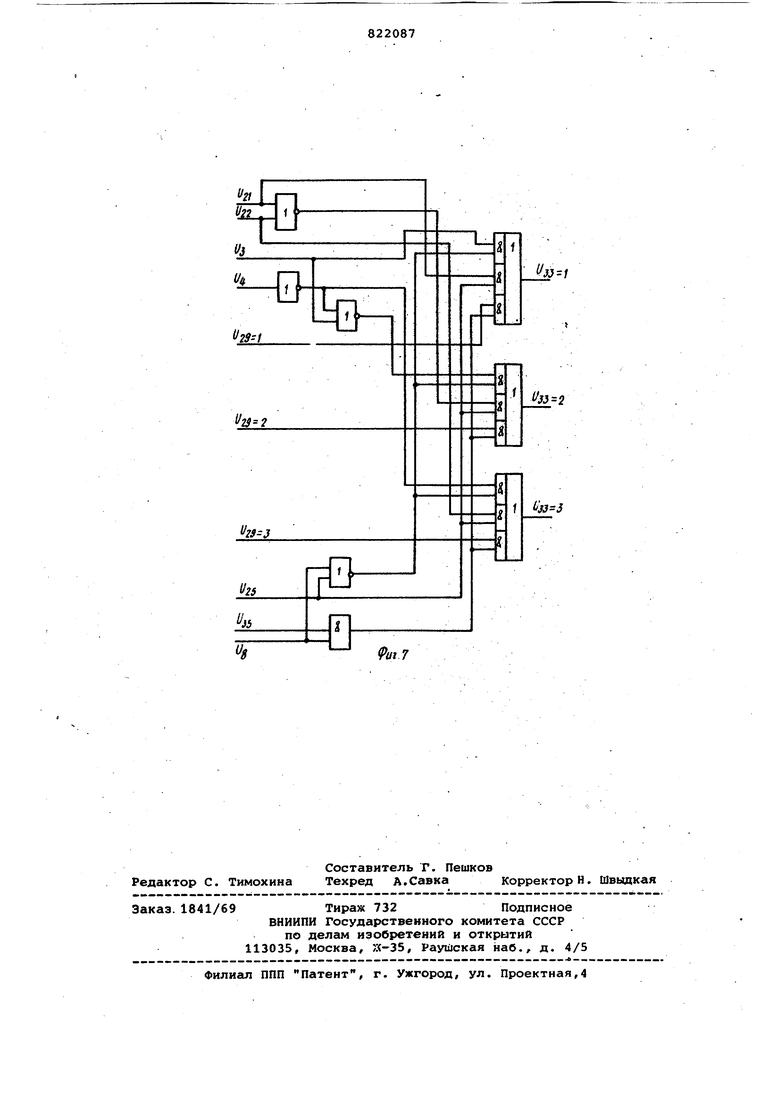

На фиг. 1 представлена блок-схема двухпорогового логического пробника; на фиг. 2 - эпюры напряжений на выходах соответствующих элементов по их номеру в блок-схеме;на фиг. 3 схематические изображения 7-, 9- и 1б-сегментных инд 1каторов; на фиг. 4 - соответствие индицируемого изображения контролируемому сигналу для 7-сегмемтного индикатора; на фиг. 5 - пример реализации анализатора импульсов на базе триггеров для устройства с 7-сегментным индикатором и индикацией состояния контрол . руемого сигнала в соответствии с фиг.4; на фиг. 6 - таблица кодировк-i шифратора; на фиг. 7 - схема комм татора для двухпорогового пробника на базе 7-сегментного индикатора при способе индикации согласно фиг.4

В соответствии с фиг.1 в двухпороговый логический пробник, содержащий входной узел 1, вход которого соединен со входом 2 устройства, компаратор верхнего уровня сигнала (КВУС) 3, вход которого соединен с первым выходом входного уЗла 1, компаратор нижнего уровня сигнала (ККУС) 4, вход которого соединен со вторым выходом входного узла, первый формирователь 5, второй формирователь 6, ключ 7, одновибратор 8 индикации и элемент И-НЕ 9, введены анализатор 10 импульсов, статический регистр 11, шифратор 12, одновибратор 13 анализа, сегментный индикатор 14, обостритель 15 импульсов запуска, коммутатор 16, причем вход 17 анализатора 10 импульсов соединен с выходом КВУС 3 и входом 18

коммутатора 16, вход 19 анализатора 10 соединен с выходом КНУС 4 и входом 20 коммутатора 16, выходы 21 и 22 анализатора 10 импульсов соединены соответственно с входами 23 и 24 коммутатора 16, остальные выходы анализатора импульсов, за исключением выхода 25, соедичены с первыми информационными входами . . . .26 статического регистра 11, выходы .... которого соединены со входами шифратора 12, выходы .,.. которого соединены с входами 29 коммутатора 16, выходы 30 1,30 2 - с выводами и сегментов сегментног индикатора 14, выводы ... других сегментов которого соединены с выходами .... коммутатора 16, вход 34 которого соединен с выходом 35 статического регистра 11, а вход 36 коммутатора 16 - с входом 37 статического регистра 11, выходом 25 анализатора 10 и первым контактом ключа 7, второй контакт которого соединен со входом контролируемого устройства, а переключающий контакт - со входом обострителя 15 импульсов запуска, выход которого соединен со входом одновибратора 13 анализа, выход которого соединен со входом одновибратора 8 индикации и входом формирователя 6, выход которого соединен с входом 38 анализатора 10 импульсов и входом 39 запис статического регистра 11, вход 40 установки в исходное состояние которого соединен с выходом формирователя 5, вход которого соединен с выходом элемента И-НЕ 9, первый вхо которого соединен с выходом одновибpaTjpa 8 индикации и входом 41 коммутатсра 16, а второй вход - с выходом одновибратора 13 анализа.

Устройство функционирует следуюЩ1м образом.

Хонтролируемый сигнал поступает не. входной узел 1,содержащий разделм ельную цепь и два буферных каск 1да, обеспечивающих высокое входное сопротивление схемы. С выходов буферных каскадов сигнал поступает на входы соответствующих компараторов. КВУС 3 обеспечивает формирование высокого уровня напряжения на выходе при превышении сигналом минимально допустимого верхнего уровня сигнала, а КНУС 4 - при уровне входного сигнала, меньше максимально допустимого нижнего уровня сигнала .

При высоком входном сопротивлении компараторов буферные каскады i. во входном узле могут отсутствовать Выходные сигналы компараторов пос.тупают на анализатор 10 импульсов, который фиксирует наличие и очередность перепадов этих сигналов. При появлении .первого перепада на выходе 25 анализатора 10 появляется сигнал сохраненк-я индицируемого изображения на время анализа после прихода первого перецада на выходе анализатора импульсов формируются сигналы и и Uj. . которые несут информацию о состоянии контролируемой схемы в момент,предше ствующии первому фиксируе1 1Ому перепаду, причем формируется сигнал U.J.1 (переключение ,с высокого уровня) , если оперным пришел отрицательный перепад сигнала Uo,,тогда как сигнал 1)2 (переключение контролируемой схемы с низкого уровня) формируется, если первым зафиксированположительный перепад сигнала U. Фиксирование этих перепадов осуществляется передним фронтом сигнала и . Сигнал UQ.5 через размыкающий и переключающий контакты ключа 7 поступает на вход обострителя 15 импульсов запуска, формирующего узкий импульс привязанный к переднему фронту сигнала ОQ .Импульс U вызывает срабатывание одновибратора 13 анализа, формирующего импулЬс Ufj Задний фронт импульса запускает одновибратор В индикации, вырабатывающий импульс U0 длительностью, равно ; длительности импульса и,г, . Длительность импульса Ug из условий удобства визуального наблюдения составляет .не менее 0,1-0,2 с. Из импульса UjOj второй формирователь 6 вырабатыаает узкий импульс и,передним фронтом привязанный к заднему фронту импульса Импульс Ug обеспечивает запись выходных сигналов анализатора 10 импульсов в статический регистр 11 и сброс анализатора 10 импульсов в исходное сотояние с задср;.;кбя относительно фрота импульса U.J из-за задержки входящих в него элементов.

Первый формирователь 5 при отсутствии импульса вырабатывает узкий импульс Ug обнуления статическо регистра 11, передний фронт которог привязан к заднему фронту импульса Ug .

Шифратор 12 преобразовывает в соответствии с принятой схемой выходные сигналы статического регистр 11 в сигналы возбуждения сигмёнтов индикатора 14, причем сигналы возбуждения вертикальных сегментов поступают непосредственно на сегменты индикатора (на входы и ), а сигналы возбуждения горизонтальны сегментов индикатора поступают на коммутатор (на входы ..,). Коммутатор подключает к соответствущим горизонтальным сегментам (электродам) индикатора или выходные сигналы компараторов U(j, и U;, при отсутствии импульсов и Ug, или сигналы возбуждения с выхода шифратора 12 при наличии импульсов Ug и

с выхода 35 регистра 11, или сигналы Ur., , Uji .при наличии сигнала U, , причем сигнал промежуточного уровня формиру ется коммутатором при одновременном отсутствии сигналов LljjH и.

При переключении ключа во второе положение характер работы устройства не изменяется за исключением того, что запуск одновибратора 13 анализа осуществляется от источника синхро0импульсов, в качестве которого удобно брать один из входных сигналов контролируемой схемы. Обостритель 15 импульсов запуска должен .иметь высокий входной импеданс для исклю5чения влияния цепи запуска пробника на параметры входного сигнала контролируемой схемы.

Для произвольного изменения времени анализа вход формирователя б должен подключаться к выходу

0 одновибратора 13, формирующего импульс требуемой длительности,но меньшей длительности импульса Ug с приходом импульса U., .Применение 7-сегментного индикатора в предло5женном устройстве дает возможность индицировать до четырех перепадов контролируемого сигнала.

При использовании 9-сегментного индикатора можно дополнительно отоб0ражать расширение (обужение) импульса на выходе контролируемого устройства по сравнению с импульсом на ее входе. Схема с 16-сегментным индикатором на выходе позволила бы ин5дицировать до шести первых перепадов контролируемого сигнала, а также, например, его расширение или обужение. Следует отметить взаимно однозначное соответствие и похо;;:есть индицируемого изображения контроли0руемому сигналу для 7-сегментного индикатора (фиг.4). На фиг.5 представлен пример реализации анализатора 10 импульсов на базе триггеров для схемы с 7-сегментным индикатором и

5 индикацией состояний контролируемого сигнала в соответствии с фиг.4. Триггеры 42 и 43 устанавливаются в состояние 1 положительными перепадами выходных сигналов 0 и

0 КВУС и КНУС соответственно, тогда как триггеры 44 и 4,5 устанавливаются в единичное состояние отрицательными перепадами этих сигналов. Индексг1ми 1 и 2 обозначены положительный и

5 отрицательный фронты выходного сигнала КВУС 3 соответственно, а индексами 3 и 4 - положительный и отрицательный фронты сигнала КНУС 4 соответственно. Триггеры 46-51 фиксируют очередность прихода фронтов сигна0лов КВУС 3 и КНУС 4. Двойной индекс напряжения, стоящий у выходного сигнала триггера,указывает,что триггер устанавливается в единичное состояние, если первым приходит фронт, чей индёкс стоит первым. Триггер 52 устанавливается в единичное состояние, если контролируемый сигнал пересек оба пошаговых уровня в установленно время, определяемое длительностью имЪульсов на выходе формирователей 53 и 54. Выходной сигнал анализатора 10 импульсов формируется при появлении хотя бы одного перепада контролируемого сигнала, т.е. при появлении напряжений и, АЪ 4 прямых выходах триггеров 42, 43, 44, 45.

На фиг. би 7 представлены примерная таблица кодировки шифратора k примерная схема коммутатора соответственно для двухпорогового пробника на базе 7-сегмектного индикатора при способе индикации согласно фиг.4, где позициями 55-75 обозначены варианты возможных изображений на индикаторе.

Пробник может быть реализован в виде компактной стержневой конструкции.

Повышение достоверности надежности и информативности индикации в устройстве достигается введением анализатора импульсов, статического регистра, шифратора, коммутатора, одновибратора анализа, обострителя импульсов запуска вследствие увеличния числа фиксируемых и анализируемых перепадов контролируемого сигнала; возможности привязки индицируемого сигнала с выхода контролируемой схемы к известному сигналу на ее входе;разделения времени анализа и времени индикации, что обеспечивает одинаковое время возбуждения сегментов и ее уверенное считывание отображения на индикаторе как текущего, так и предшествующего состояния контролируемой схемы и переход между ними; снижения условности изображения и приближения его к реальному, привычному осциллографическому ; одновременной индикации как полных,так и неполных перепадов; увеличения числа комбинаций индицируемых перепадов; исключения прерывистого характера индикации, являющегося одной из .причин утомляемости оператора.

Формула изобретения

Двухпороговый логический пробник, содержащий входной узел, вход которого соединен со входом устройства, компаратор верхнего уровня сигнала, вход которого соединен с первым выходом входного узла, компаратор нижнего уровня сигнала, вход которого соединен со вторым выходом входного узла, первый формирователь, второй формирователь, ключ, одновибратор индикации и элемент И-НЕ, отличающийся тем, что, с целью повышения достоверности и информативности индикации, в него введены анализатор импульсов, статический регистр, шифратор, одновибратор анализа, сегментный индикатор, обостритель импульсов запуска коммутатор, причем первый вход анализатора импульсов соединен с выходом компаратора верхнего уровня сигнала и первым входом коммутатора, второй вход анализатора импульсов соединен с выходом компаратора нижне уровня сигнала и вторым входом коммутатора, первый и второй выходы анализатора импульсов соединены соответственно с третьим и четвертым входами коммутатора, остальные выходы анализатора импульсов, за исключением третьего, соединены с первыми информационными входами статического регистра, первые выходы которого соединены со входами шифратора,первы выходы которого соединены с пятым входом коммутатора, вторые выходы с первыми сегментами сегментного индикатора, вторые сегменты которого соединены с выходами коммутатора, шестой вход которого соединен со вторым выходом статического регистра а седьмой вход - со вторым информационным входом статического регистра третьим выходом анализатора импульсов и первым контактом ключа, второй контакт которого соединен со входом контролируемого устройства, а переключающий контакт - со входом обострителя импульсов запуска, выход которого соединен со входом .одновибратора анализа, выход которого соединен со входом одновибратора индикации и входом второго формирователя, выход которого соединен с третьи входом анализатора импульсов и входом записи статического регистра, вход установки в исходное состояние которого соединен с выходом первого формирователя, вход которого соединен с выходом элемента И-НЕ, первый вход которого соединен с выходом одновибратора индикации и восьмым входом коммутатора, а второй вход с выходом одновибратора анализа.

Источники информации, принятые во внимание при экспертизе

1.Приборы и системы управления 1974, 12, с. 38, рисЛ.

2. Патент США № 4110687, кл. G 01 R 31/02, 29.08.78.

« (

С U2

mm

твд

т 1 т п и

П fucfu fu fD D

J5 5 7 f953 60SI

- .

Л- X

-s.

(/;

min

тал

// / / 7 Ш f/7/ Шс f/J/r и LJ Of L-/

W63W WW«7W

i уъ

ffTiEJ n г}в n 6 I-I О bJ HJ Ш LJ

70fl 7273 /«V

РигЛ

Яг,

(Jfy

%--/

JJ /

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический пробник | 1981 |

|

SU1019378A1 |

| Логический пробник | 1980 |

|

SU917144A1 |

| Сигнатурный анализатор | 1982 |

|

SU1108452A1 |

| Сигнатурный анализатор | 1980 |

|

SU903898A1 |

| Устройство для обнаружения неисправностей в электрическом монтаже | 1976 |

|

SU636560A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Пробник для проверки логических устройств на микросхемах эмиттерно-связанной логики | 1983 |

|

SU1108373A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

гтО

il2S

Ui

Риг

Авторы

Даты

1981-04-15—Публикация

1979-06-11—Подача