11

Изобретение относится к автоматике и вычислительной технике и может быть использовано для автоматизированной подготовки nporpaMJ станков с ЧПУ, а также роботов-манипулято- ров.

Цель изобретения - повьпяение точности и сокращение времени подготовки программ.

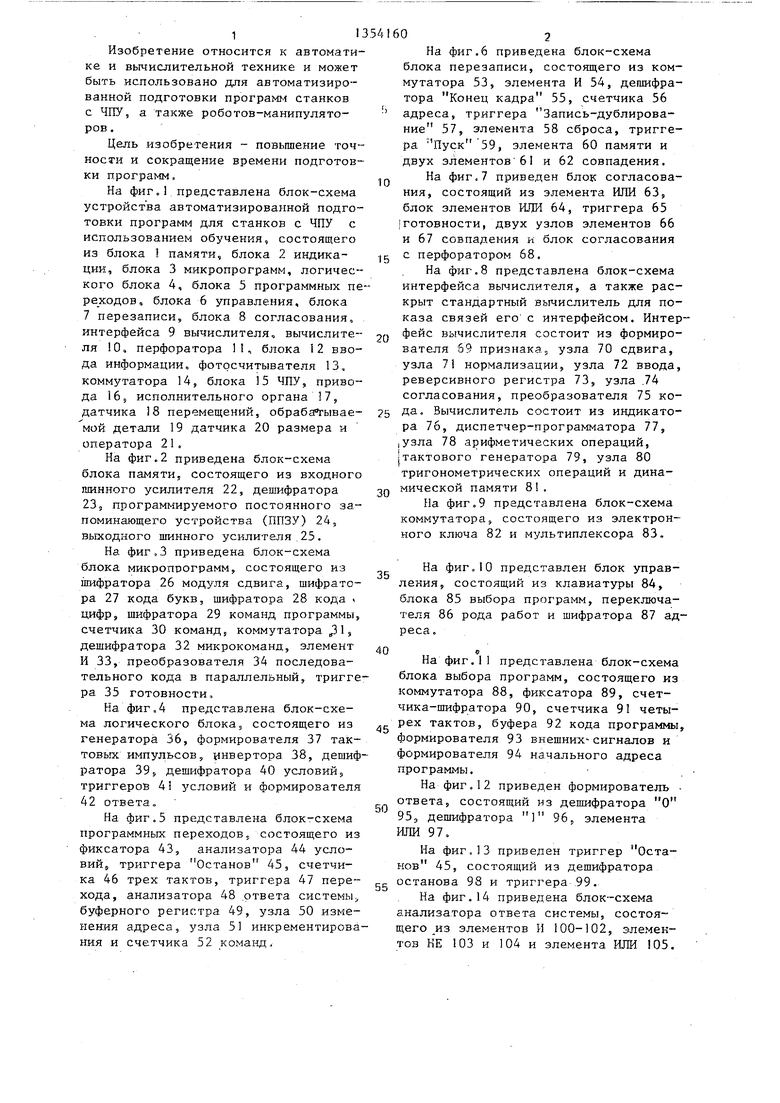

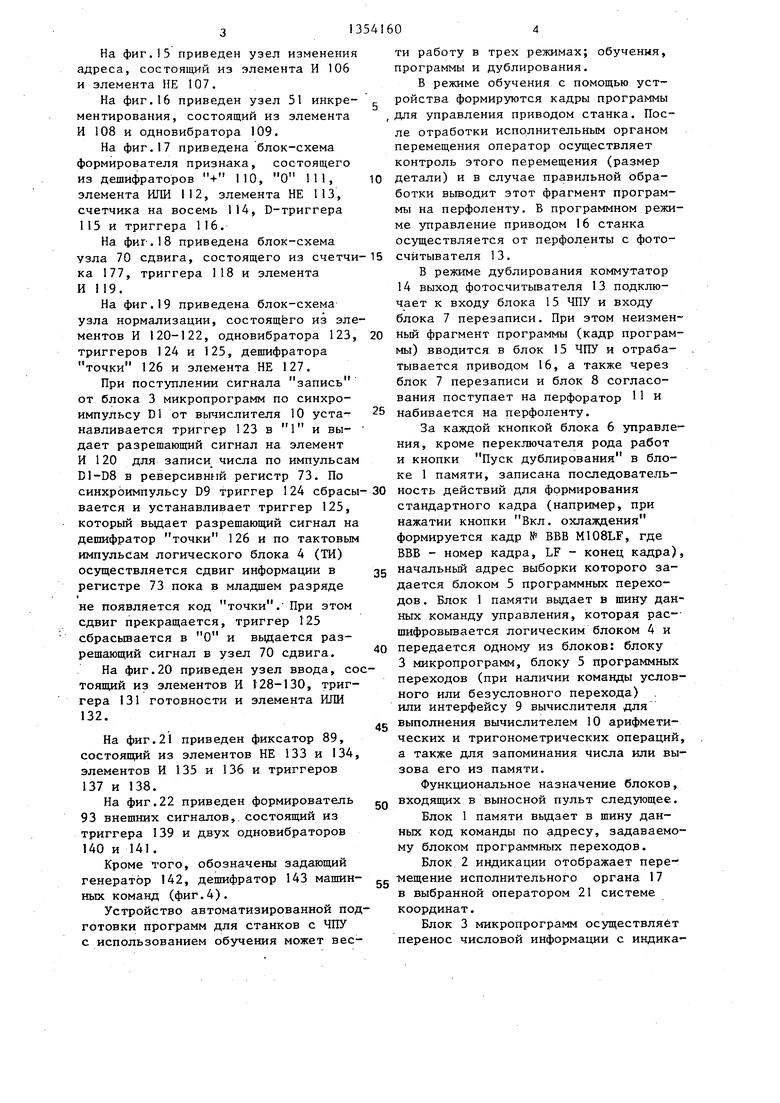

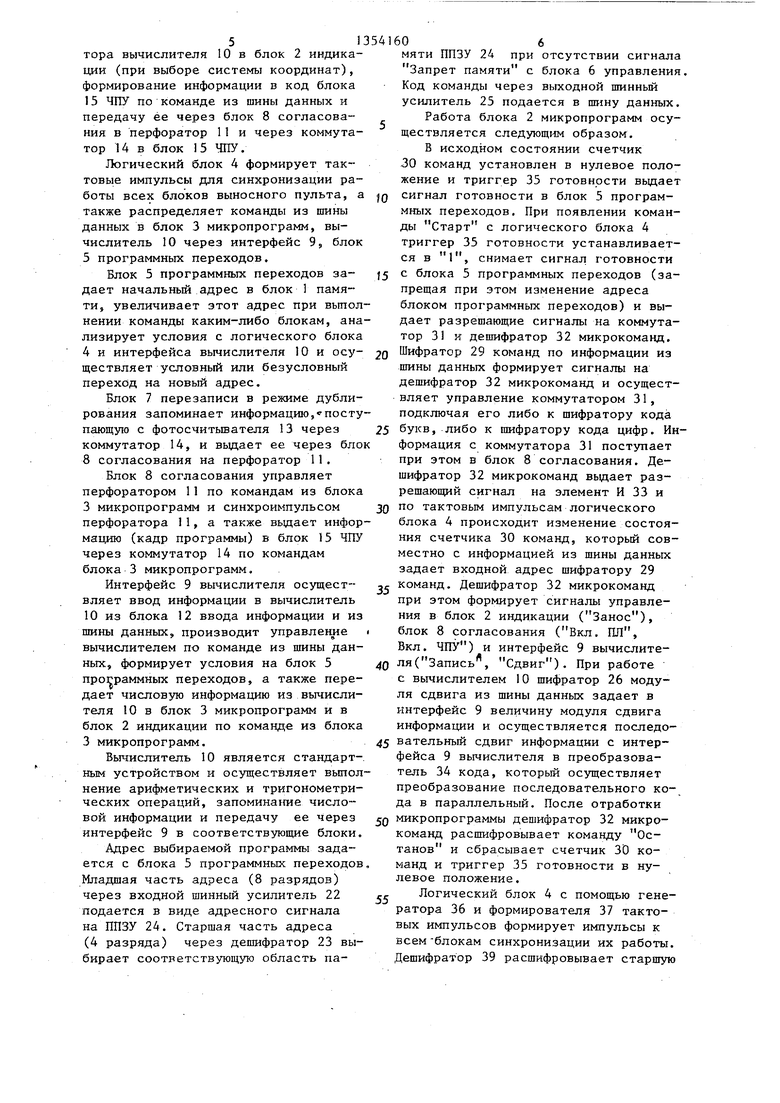

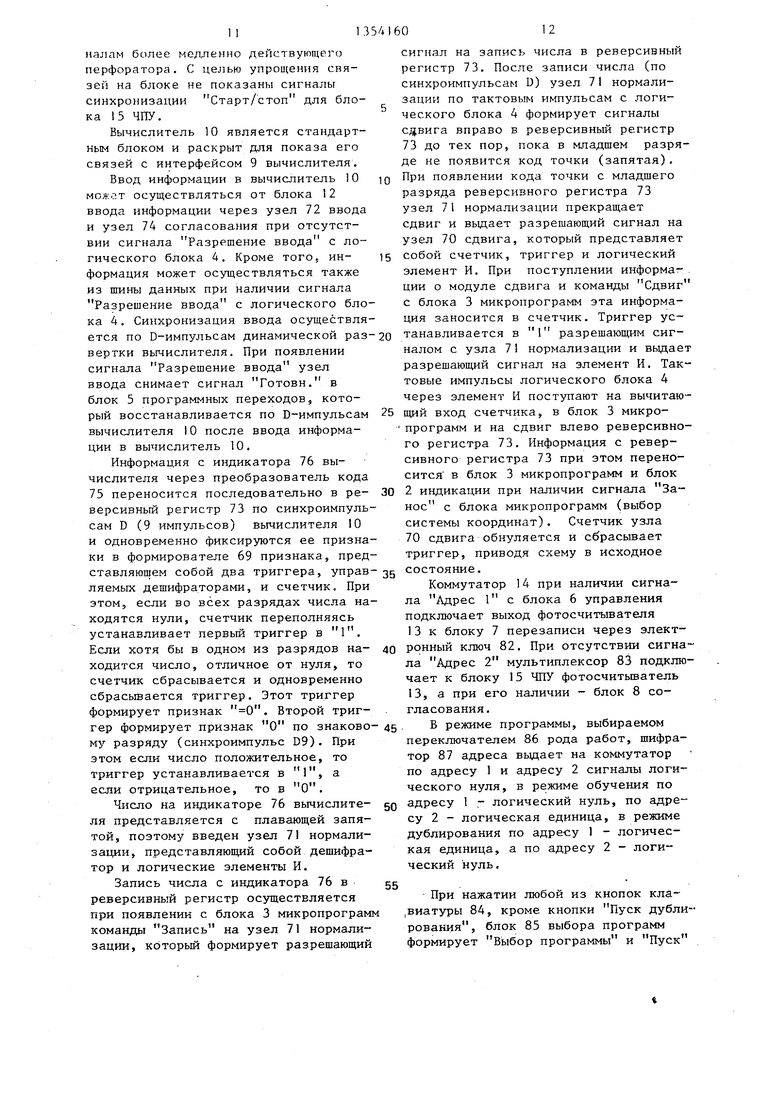

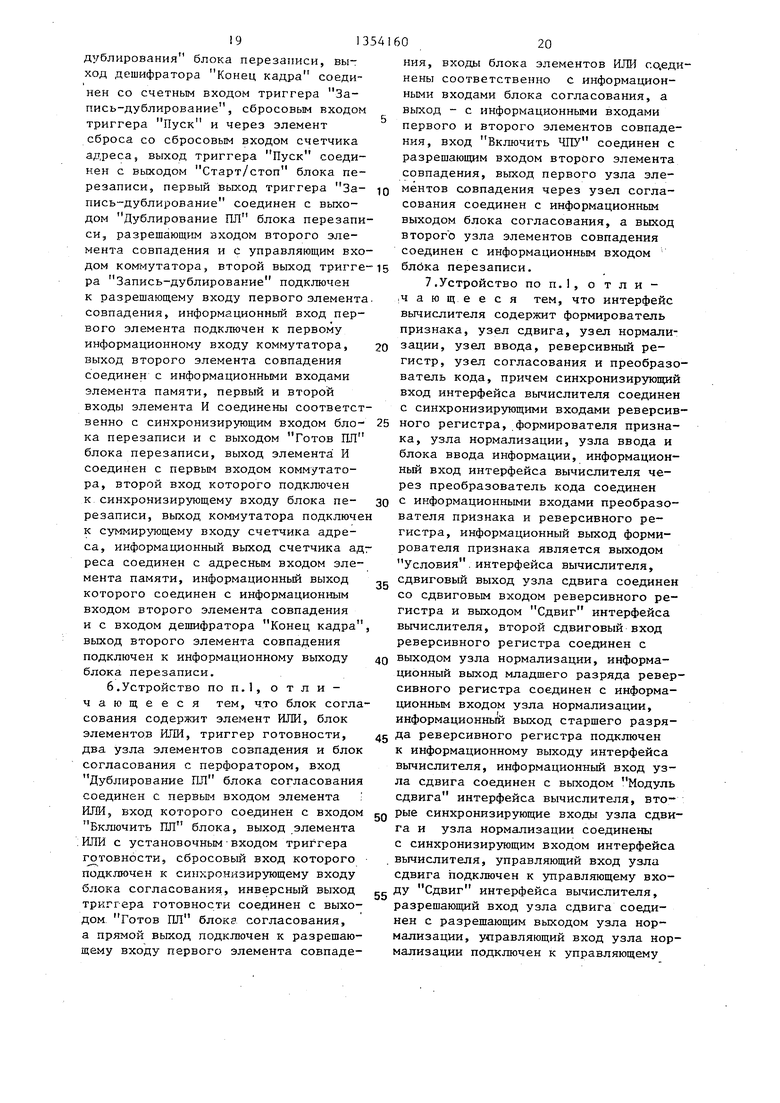

На фиг.1 представлена блок-схема устройства автоматизированной подготовки программ для станков с ЧПУ с использованием обучения, состоящего из блока памяти, блока 2 индика- цин, блока 3 микропрограмм, логического блока 4, блока 5 программных переходов, блока 6 управления, блока 7 перезаписи, блока 8 согласования, интерфейса 9 вычислителя, вычислите- ля 0, перфоратора П, блока 12 ввода информации, фотосчитывателя 13, коммутатора 14, блока 15 ЧПУ, привода 16, исполнительного органа 17, датчика 18 перемещений, обраба ывае- мой детали 19 датчика 20 размера и оператора 21.

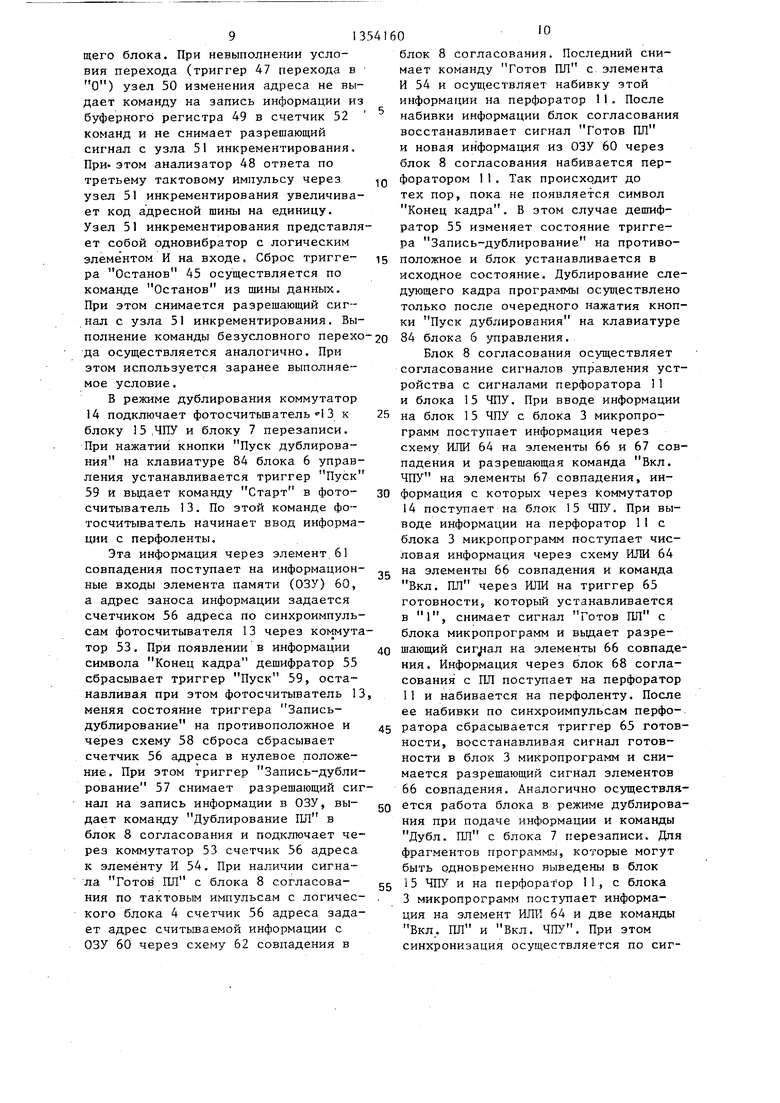

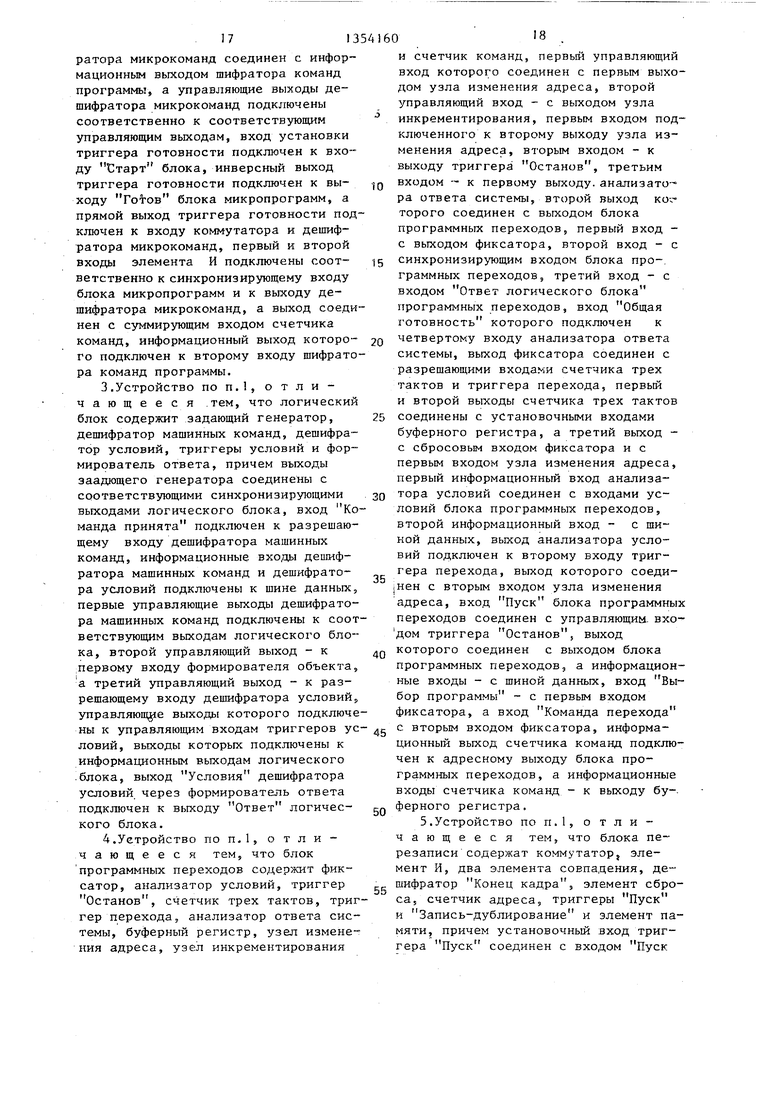

На фиг.2 приведена блок-схема блока памяти, состоящего из входного шинного усилителя 22, дешифратора 23, программируемого постоянного запоминающего устройства (ППЗУ) 24, выходного шинного усилителя . 25.

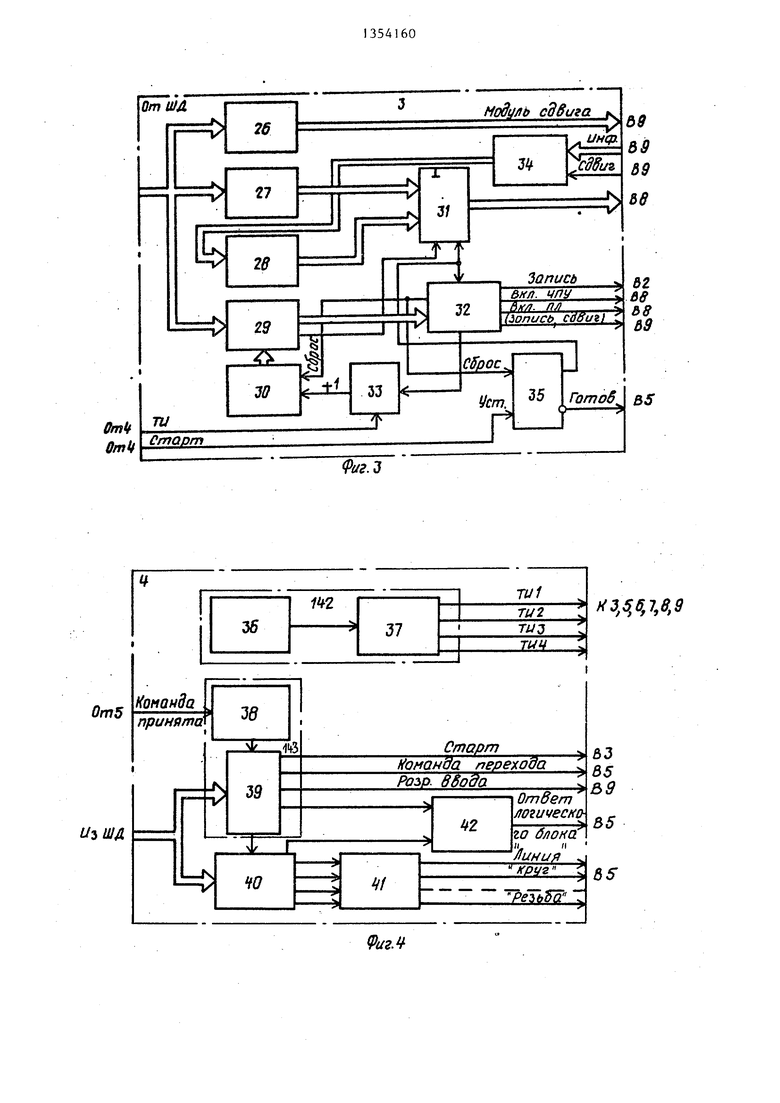

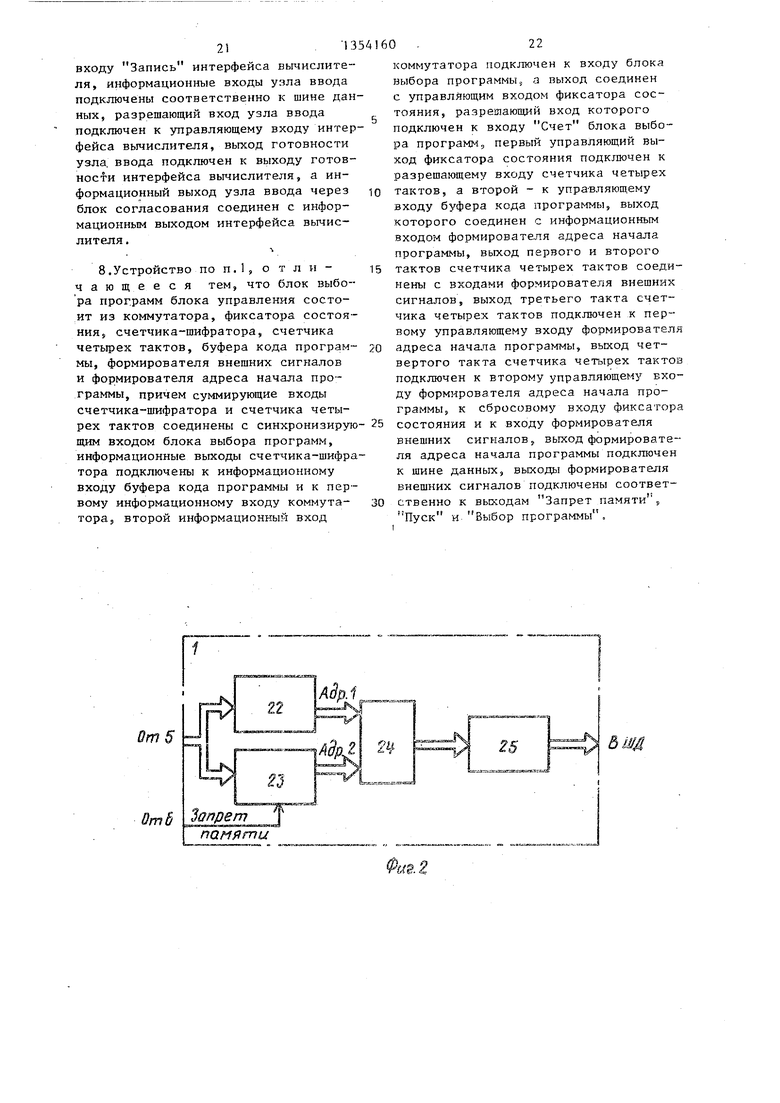

На фиг,3 приведена блок-схема блока микропрограмм, состоящего из шифратора 26 модуля сдвига, шифратора 27 кода букв, шифратора. 28 кода цифр, шифратора 29 команд программы, счетчика 30 команд, коммутатора 1, дешифратора 32 микрокоманд, элемент И 33, преобразователя 34 последовательного кода в параллельный, триггера 35 готовности.

На фиг.4 представлена блок-схема логического блока, состоящего из генератора 36, формирователя 37 тактовых импульсов , нвертора 38, дешифратора 39s дешифратора 40 условий, триггеров 4 i условий и формирователя 42 ответа.

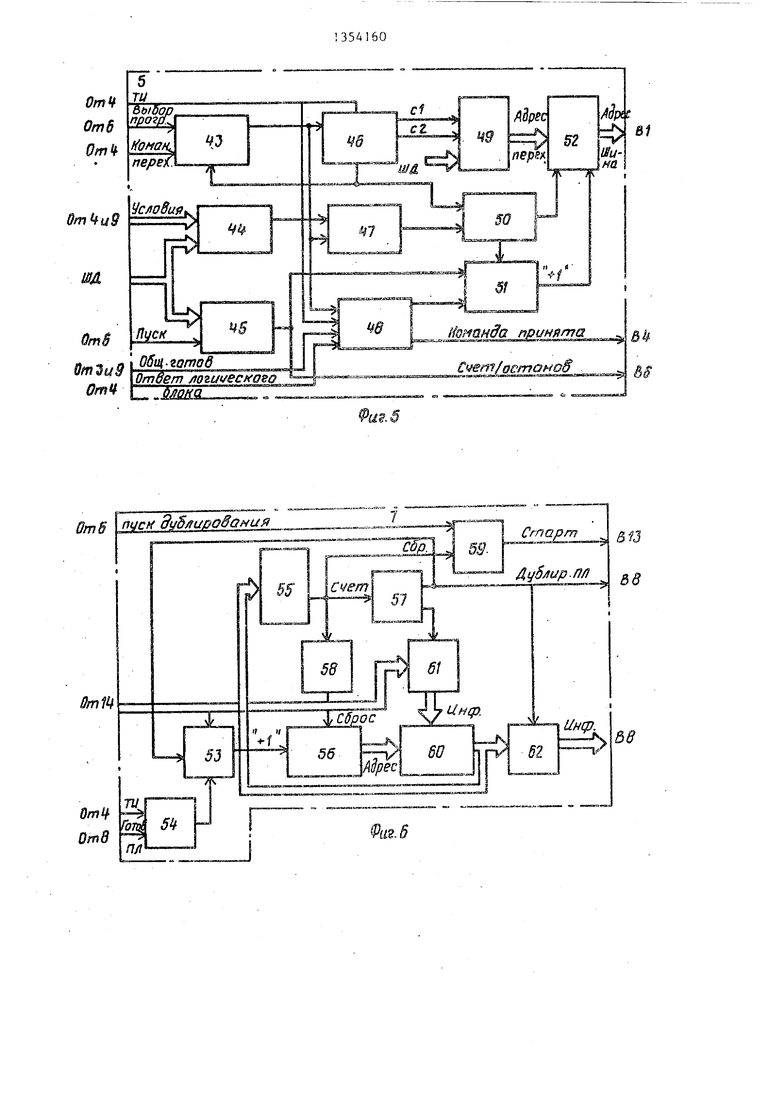

На фиг,5 представлена блок-схема программных переходов, состоящего из фиксатора 43, анализатора 44 условий, триггера Останов 45, счетчика 46 трех тактов, триггера 47 пере- хода, анализатора 48 .ответа системы,, буферного регистра 49, узла 50 изменения адреса, узла 51 инкрементирова ния и счетчика 52 команд,,

0

1

g о 5

о

602

На фиг.6 приведена блок-схема блока перезаписи, состоящего из коммутатора 53, элемента И 54, дешифратора Конец кадра 55, счетчика 56 адреса, триггера Запись-дублирование 57, элемента 58 сброса, триггера Пуск 59, элемента 60 памяти и двух элементов 61 и 62 совпадения.

На фиг.7 приведен блок согласования, состоящий из элемента ИЛИ 63, блок элементов ИДИ 64, триггера 65 готовности, двух узлов элементов 66 и 67 совпадения и блок согласования с перфоратором 68,

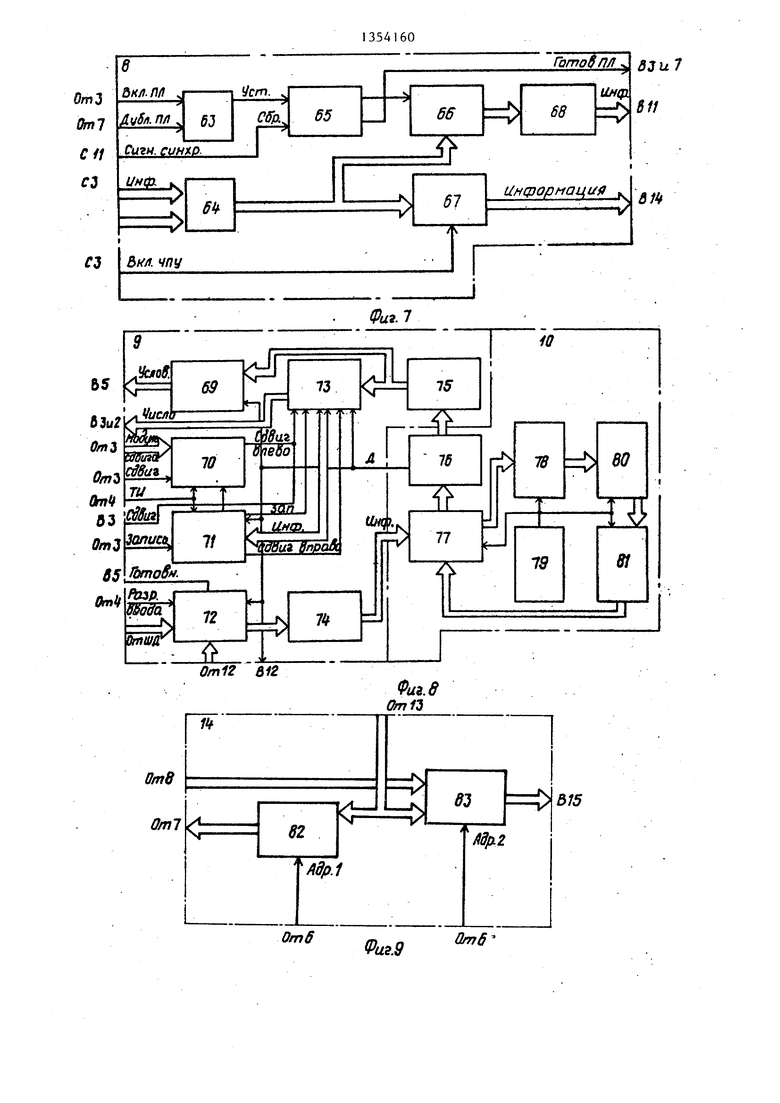

На фиг,8 представлена блок-схема интерфейса вычислителя, а также раскрыт стандартный вычислитель для показа связей его с интерфейсом. Интерфейс вычислителя состоит из формирователя 59 признака, узла 70 сдвига, узла 7 нормализации, узла 72 ввода, реверсивного регистра 73, узла .74 согласования, преобразователя 75 кода. Вычислитель состоит из индикатора 76, диспетчер-программатора 77, .узла 78 арифметических операций, тактового генератора 79, узла 80 тригонометрических операций и динамической памяти 8.

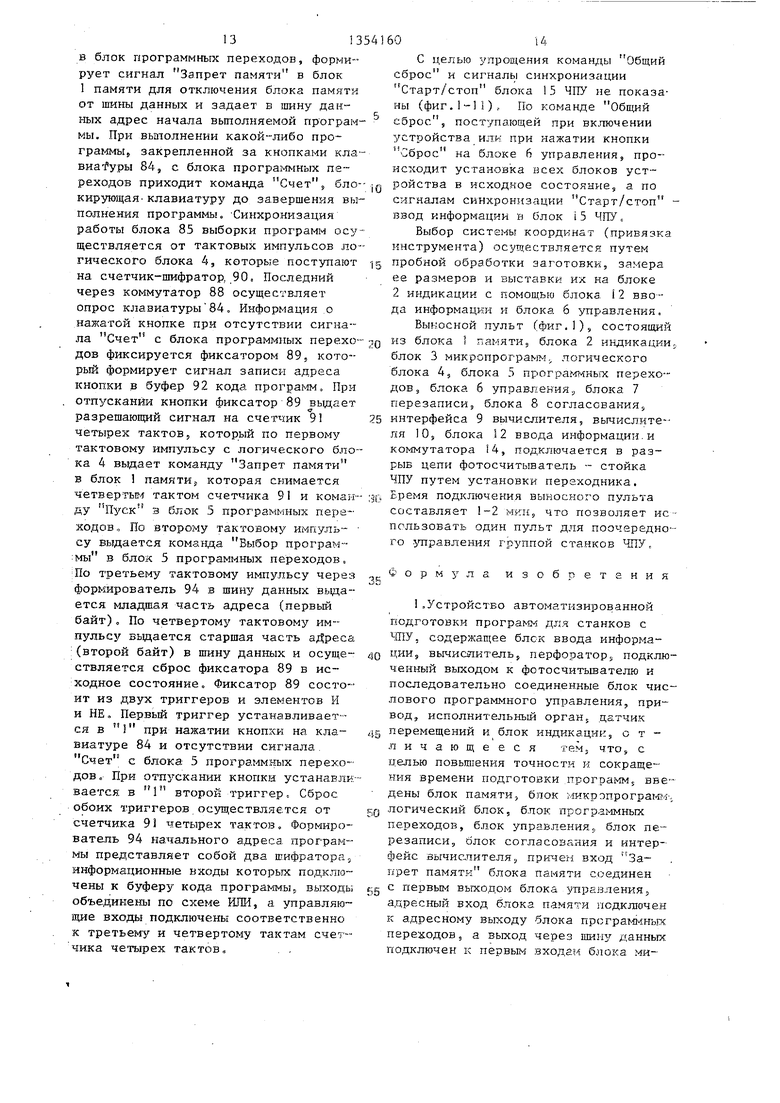

На фиг.9 представлена блок-схема коммутатора, состоящего из электронного ключа 82 и мультиплексора 83.

Q

g

5

0

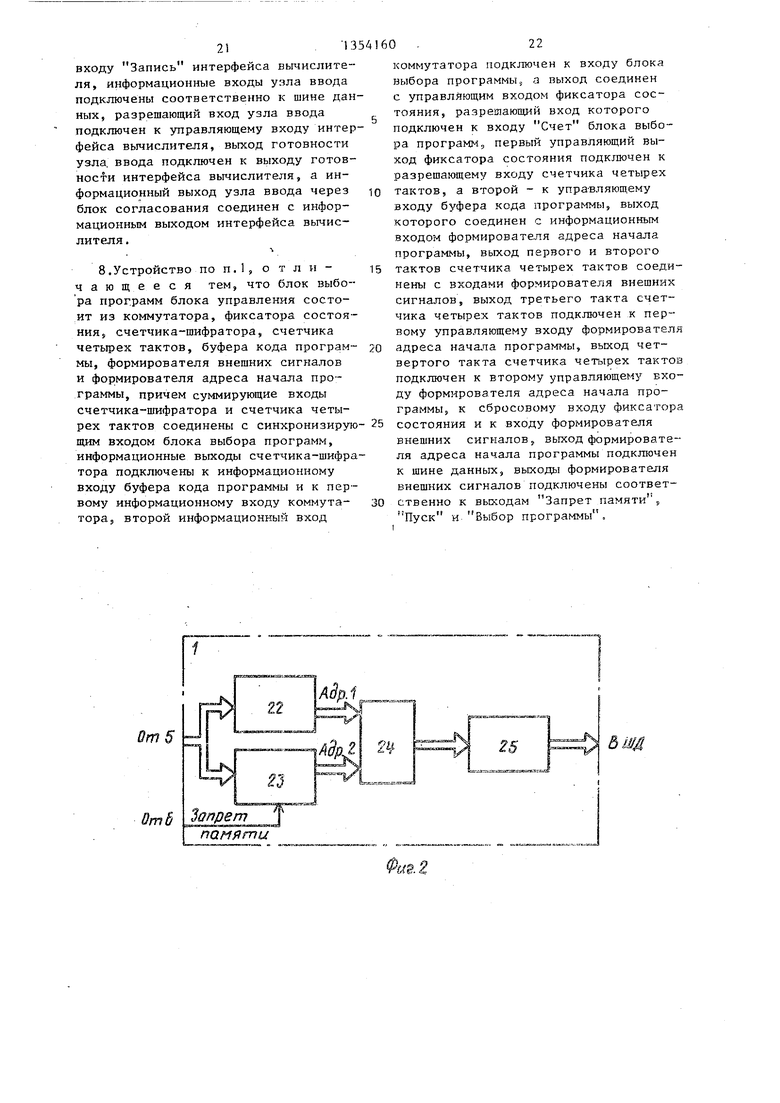

На фиг.10 представлен блок управления, состоящий из клавиатуры 84, блока 85 выбора программ, переключателя 86 рода работ и шифратора 87 адреса .

о На фиг.11 представлена блок-схема

блока выбора программ, состоящего из коммутатора 88, фиксатора 89, счетчика-шифратора 90, счетчика 91 четырех тактов, буфера 92 кода программы, формирователя 93 внешних сигналов и формирователя 94 начального адреса программы.

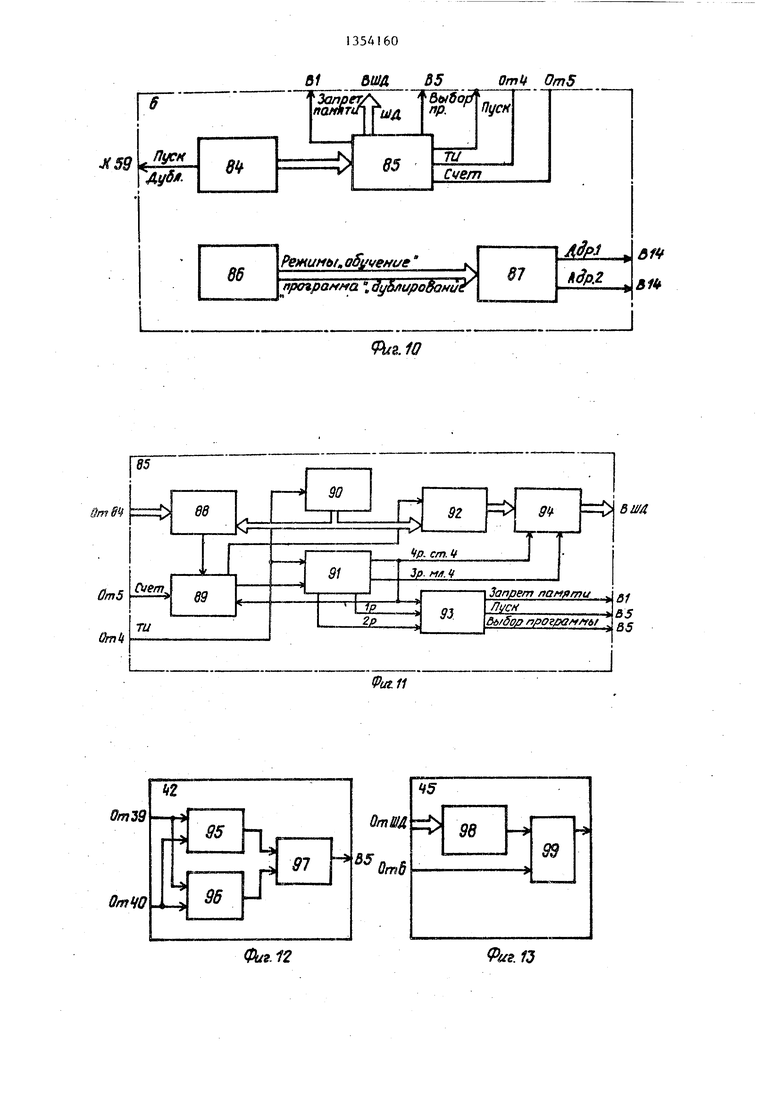

На фиг.12 приведен формирователь ответа, состоящий из дешифратора О 95, дешифратора 1 96, элемента ШШ 97.

На фиг.13 приведен триггер Останов 45, состоящий из дешифратора останова 98 и триггера .99.

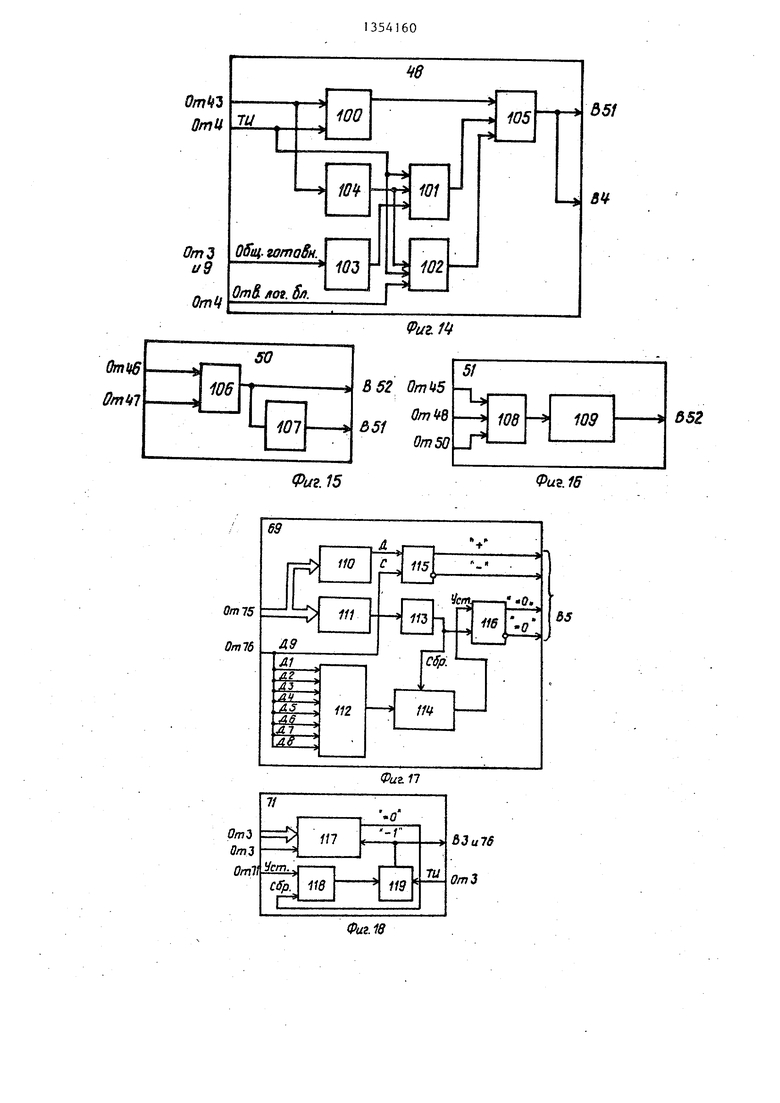

На фиг.14 приведена блок-схема анализатора ответа системы, состоящего из элементов И 100-102, элементов НЕ 103 и 104 и элемента ИШИ 05.

На фиг.15 приведен узел изменения адреса, состоящий из элемента И 106 и элемента НЕ 107.

На фиг.16 приведен узел 51 инкре- ментирования, состоящий из элемента И 108 и одновибратора 109.

На фиг.17 приведена блок-схема формирователя признака, состоящего

из дешифраторов + ПО, О 111,

элемента ИЛИ 112, элемента НЕ 113, счетчика на восемь 114, D-триггера 1 15 и триггера 116.

На фиг.18 приведена блок-схема узла 70 сдвига, состоящего из счетчи ка 177, триггера 118 и элемента И I 19.

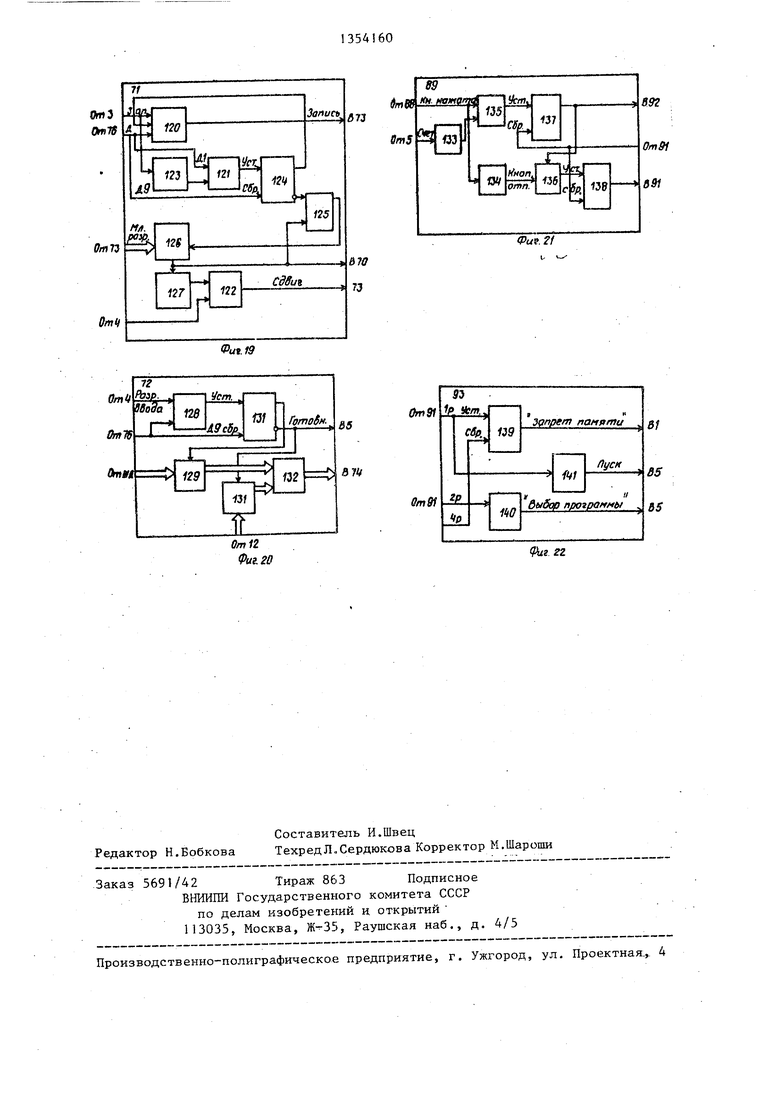

На фиг.19 приведена блок-схема узла нормализации, состоящего из элементов И 120-122, одновибратора 123, триггеров 124 и 125, дешифратора точки 126 и элемента НЕ 127.

При поступлении сигнала запись от блока 3 микропрограмм по синхроимпульсу D1 от вычислителя 10 уста- навливается триггер 123 в 1 и вы- дает разрешающий сигнал на элемент И 120 для записи числа по импульсам B1-D8 в реверсивний регистр 73. По синхроимпульсу D9 триггер 124 сбрасы вается и устанавливает триггер 125, который выдает разрешающий сигнал на дешифратор точки 126 и по тактовым импульсам логического блока 4 (ТИ) осуществляется сдвиг информации в регистре 73 пока в младшем разряде

не появляется код точки. При этом сдвиг прекращается, триггер 125 сбрасьшается в О и выдается разрешающий сигнал в узел 70 сдвига.

На фиг.20 приведен узел ввода, сотоящий из элементов И }28-130, триггера 131 готовности и элемента ИЛИ 132.

На фиг.21 приведен фиксатор 89,

состоящий из элементов НЕ 133 и 134, элементов И 135 и 136 и триггеров 137 и 138.

На фиг.22 приведен формирователь 93 внешних сигналов,. состоящий из триггера 139 и двух одновибраторов 140 и 141.

Кроме того, обозначены задающий генератор 142, дешифратор 143 машин- ных команд (фиг.4).

Устройство автоматизированной подготовки программ для станков с ЧПУ с использованием обучения может вес

0

5

0

25 0 35

0

45

gQ

gg

ти работу в трех режимах; обучения, программы и дублирования.

В режиме обучения с помощью устройства формируются кадры программы , для управления приводом станка. После отработки исполнительным органом перемещения оператор осуществляет контроль этого перемещения (размер детали) и в случае правильной обработки вьгоодит этот фрагмент программы на перфоленту. Б программном режиме управление приводом 16 станка осуществляется от перфоленты с фото- считывателя 13.

В режиме дублирования коммутатор 14 выход фотосчитывателя 13 подключает к входу блока 15 ЧПУ и входу блока 7 перезаписи. При этом неизменный фрагмент программы (кадр программы) вводится в блок 15 ЧПУ и отрабатывается приводом 16, а также через блок 7 перезаписи и блок 8 согласования поступает на перфоратор 11 и набивается на перфоленту.

За каждой кнопкой блока 6 управления, кроме переключателя рода работ и кнопки Пуск дублирования в блоке 1 памяти, записана последовательность действий для формирования стандартного кадра (например, при нажатии кнопки Вкл. охлаждения формируется кадр № ВВВ M108LF, где ВВВ - номер кадра, LF - конец кадра), начальный адрес выборки которого задается блоком 5 программных переходов . Блок 1 памяти выдает в шину данных команду управления, которая рас-- шифровьшается логическим блоком 4 и передается одному из блоков: блоку 3 микропрограмм, блоку 5 программных переходов (при наличии команды условного или безусловного перехода) или интерфейсу 9 вычислителя для выполнения вычислителем 10 арифметических и тригонометрических операций, а также для запоминания числа или вызова его из памяти.

Функциональное назначение блоков, входящих в выносной пульт следующее.

Блок 1 памяти выдает в шину данных код команды по адресу, задаваемому блоком программных переходов.

Блок 2 индикации отображает перемещение исполнительного органа 17 в выбранной оператором 21 системе координат.

Блок 3 микропрограмм осуществляет перенос числовой информации с индика513

тора вычислителя 10 в блок 2 индикации (при выборе системы координат), формирование информации в код блока 15 ЧПУ по команде из шины данных и передачу ее через блок 8 согласования в перфоратор 11 и через коммутатор 14 в блок 15 ЧПУ.

Логический блок 4 формирует тактовые импульсы для синхронизации работы всех блоков выносного пульта, а также распределяет команды из шины данных в блок 3 микропрограмм, вычислитель 10 через интерфейс 9, блок 5 программных переходов.

Блок 5 программных переходов за- дает начальный адрес в блок 1 памяти, увеличивает этот адрес при выполнении команды каким-либо блокам, анализирует условия с логического блока 4 и интерфейса вычислителя 10 и осу- ществляет условный или безусловный переход на новый адрес.

Блок 7 перезаписи в режиме дублирования запоминает информацию,поступающую с фотосчитьшателя 13 через коммутатор 14, и выдает ее через бло 8 согласования на перфоратор 11.

Блок 8 согласования управляет перфоратором 11 по командам из блока 3 микропрограмм и синхроимпульсом перфоратора 11, а также выдает информацию (кадр программы) в блок 15 ЧПУ через коммутатор 14 по командам блока 3 микропрограмм.

Интерфейс 9 вычислителя осущест-- вляет ввод информации в вычислитель 10 из блока 12 ввода информации и из шины данных, производит управление вычислителем по команде из шины данных, формирует условия на блок 5 программных переходов, а также передает числовую информацию из вычислителя 10 в блок 3 микропрограмм и в блок 2 индикации по команде из блока 3 микропрограмм.

Вычислитель 10 является стандартным устройством и осуществляет выполнение арифметических и тригонометрических операций, запоминание числовой информации и передачу ее через интерфейс 9 в соответствующие блоки.

Адрес выбираемой программы задается с блока 5 программных переходов Младшая часть адреса (8 разрядов) через входной шинный усилитель 22 подается в виде адресного сигнала на ППЗУ 24. Старшая часть адреса (4 разряда) через дешифратор 23 выбирает соответствующую область па06

мяти ППЗУ 24 при отсутствии сигнала Запрет памяти с блока 6 управления. Код команды через выходной шинный усилитель 25 подается в шину данных.

Работа блока 2 микропрограмм осуществляется следующим образом.

В исходном состоянии счетчик 30 команд установлен в нулевое положение и триггер 35 готовности выдает сигнал готовности в блок 5 программных переходов. При появлении команды Старт с логического блока 4 триггер 35 готовности устанавливается в

снимает сигнал готовности

с блока 5 программных переходов (запрещая при этом изменение адреса блоком программных переходов) и выдает разрешающие сигналы на коммутатор 3 и дешифратор 32 микрокоманд. Шифратор 29 команд по информации из шины данных формирует сигналы на дешифратор 32 микрокоманд и осуществляет управление коммутатором 31, подключая его либо к шифратору кода букв, либо к шифратору кода цифр. Иформация с коммутатора 31 поступает при этом в блок 8 согласования. Дешифратор 32 микрокоманд выдает разрешающий сигнал на элемент И 33 и по тактовым импульсам логического блока 4 происходит изменение состояния счетчика 30 команд, который совместно с информацией из шины данных задает входной адрес шифратору 29 команд. Дешифратор 32 микрокоманд при этом формирует сигналы управления в блок 2 индикации (Занос), блок 8 согласования (Вкл. ПЛ, Вкл. ЧПУ) и интерфейс 9 вычислите- ля(3апись, Сдвиг). При работе с вычислителем 10 шифратор 26 модуля сдвига из шины данных задает в интерфейс 9 величину модуля сдвига информации и осуществляется последовательный сдвиг информации с интерфейса 9 вычислителя в преобразователь 34 кода, который осуществляет преобразование последовательного кода в параллельный. После отработки микропрограммы дешифратор 32 микрокоманд расшифровывает команду Останов и сбрасывает счетчик 30 команд и триггер 35 готовности в нулевое положение.

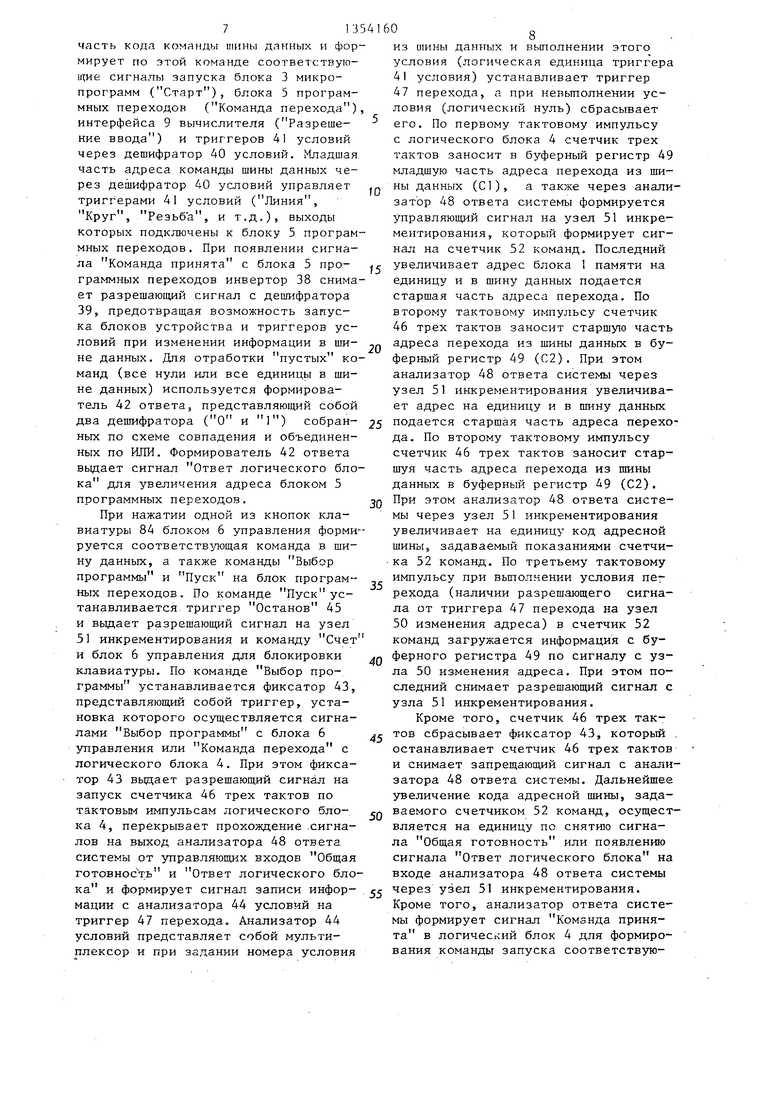

Логический блок 4 с помощью генератора 36 и формирователя 37 тактовых импульсов формирует импульсы к всем-блокам синхронизации их работы Дешифратор 39 расшифровывает старшую

)0

7i:J54160

часть кода команды шнны данных и формирует по этой команде соответствующие сигналы запуска блока 3 микропрограмм (Старт), блока 5 программных переходов (Команда перехода), интерфейса 9 вычислителя (Разрешение ввода) и триггеров 41 условий через дешифратор 40 условий. Младшая часть адреса команды шины данных через дешифратор АО условий управляет триггерами 41 условий (Линия, Круг, Резьб а, и т.д.). выходы которых подключены к блоку 5 програм мных переходов. При появлении сигнала Команда принята с блока 5 программных переходов инвертор 38 снимает разрешающий сигнал с дешифратора 39, предотвращая возможность запуска блоков устройства и триггеров условий при изменении информации в ши- -,„ адреса перехода из шины данных в бу- не данных. Дпя отработки пустых ко- фарный регистр 49 (С2). При этом манд (все нули или все единицы в ши- анализатор 48 ответа системы через

15

8 из шины дашгых и выполнении этого

условия (логическая единица триггера 41 условия) устанавливает триггер 47 перехода, а при невьтолнемии условия (логический нуль) сбрасывает его. По первому тактовому импульсу с логического блока 4 счетчик трех тактов заносит в буферный регистр 49 младшую часть адреса перехода из шины данных (С1), а также через анализатор 48 ответа системы формируется У правляюш 1Й сигнал на узел 51 инкре- ментирования, который формирует сигнал на счетчик 52 команд. Последний увеличивает адрес блока 1 памяти на единицу и в шину данных подается старшая часть адреса перехода. По второму тактовому импульсу счетчик 46 трех тактов заносит старшую часть

не данных) используется формирователь 42 ответа, представляющий собой два дешифратора (О и 1) собранных по схеме совпадения и объединенных по ИЛИ. Формирователь 42 ответа вьщает сигнал Ответ логического блока для увеличения адреса блоком 5 программных переходов.

При нажатии одной из кнопок клавиатуры 84 блоком 6 управления формируется соответствующая команда в шину данных, а также команды Выбор программы и Пуск на блок програм- ных переходов. По команде Пуск устанавливается триггер Останов 45 и вьщает разрешаю1ций сигнал на узел 51 инкрементирования и команду Счет и блок 6 управления для блокировки клавиатуры. По команде Выбор программы устанавливается фиксатор 43, представляюш;ий собой триггер, установка которого осуществляется сигналами Выбор программы с блока 6 управления или Команда перехода с логического блока 4. При этом фиксатор 43 выдает разрешающий сигнал на запуск счетчика 46 трех тактов по тактовым импульсам логического блока 4, перекрывает прохождение .сигналов на выход анализатора 48 ответа системы от управляющих входов Общая roTOBHOcVb и Ответ логического блока и формирует сигнал записи информации с анализатора 44 условий на триггер 47 перехода. Анализатор 44 условий представляет собой мультиплексор и при задании номера условия

0

160

,„ адреса перехода из шины данных в бу- фарный регистр 49 (С2). При этом анализатор 48 ответа системы через

5

8 из шины дашгых и выполнении этого

условия (логическая единица триггера 41 условия) устанавливает триггер 47 перехода, а при невьтолнемии условия (логический нуль) сбрасывает его. По первому тактовому импульсу с логического блока 4 счетчик трех тактов заносит в буферный регистр 49 младшую часть адреса перехода из шины данных (С1), а также через анализатор 48 ответа системы формируется У правляюш 1Й сигнал на узел 51 инкре- ментирования, который формирует сигнал на счетчик 52 команд. Последний увеличивает адрес блока 1 памяти на единицу и в шину данных подается старшая часть адреса перехода. По второму тактовому импульсу счетчик 46 трех тактов заносит старшую часть

5

0

5

0

узел 51 инкрементирования увеличивает адрес на единицу и в шину данных подается старшая часть адреса перехода. По второму тактовому импульсу счетчик 46 трех тактов заносит стартуя часть адреса перехода из шины данных в буферный регистр 49 (С2). При этом анализатор 48 ответа системы через узел 51 инкрементирования увеличивает на единицу код адресной шины, задаваемый показаниями счетчика 52 команд. По третьему тактовому импульсу при выполнении условия перехода (наличии разрешающего сигнала от триггера 47 перехода на узел 50 изменения адреса) в счетчик 52 команд загружается информация с буферного регистра 49 по сигналу с узла 50 изменения адреса. При этом последний снимает разрешающий сигнал с узла 51 инкрементирования.

Кроме того, счетчик 46 трех такг тов сбрасывает фиксатор 43, который . останавливает счетчик 46 трех тактов и снимает запрещающий сигнал с анализатора 48 ответа системы. Дальнейшее увеличение кода адресной шины, задап ваемого счетчиком 52 команд, осуществляется на единицу по снятию сигнала Общая готовность или появлению сигнала Ответ логического блока на входе анализатора 48 ответа системы

е через узел 51 инкрементирования.

Кроме того, анализатор ответа системы формирует сигнал Команда принята в логический блок 4 для формирования команды запуска соответствую

щего блока. При невыполнении условия перехода (триггер 47 перехода в О) узел 50 изменения адреса не выдает команду на запись информации из буферного регистра 49 в счетчик 52 команд и не снимает разрешающий сигнал с узла 51 инкрементирования. При- этом анализатор 48 ответа по третьему тактовому импульсу через узел 51 инкрементирования увеличивает код адресной шины на единицу. Узел 51 инкрементирования представляет собой одновибратор с логическим элементом И на входе. Сброс тригге- ра Останов 45 осуществляется по команде Останов из шины данных. При этом снимается разрешающий сиг-нал с узла 51 инкрементирования. Выполнение команды безусловного перехо да осуществляется аналогично. При этом используется заранее выполняемое условие.

В режиме дублирования коммутатор 14 подключает фотосчитьшатель 13 к блоку 15.ЧПУ и блоку 7 перезаписи. При нажатии кнопки Пуск дублирования на клавиатуре 84 блока 6 управления устанавливается триггер Пуск 59 и выдает команду Старт в фотосчитыватель 13. По этой команде фотосчитыватель начинает ввод информации с перфоленты.

Эта информация через элемент.61 совпадения поступает на информационные входы элемента памяти (ОЗУ) 60, а адрес заноса информации задается счетчиком 56 адреса по синхроимпульсам фотосчитывателя 13 через коммутатор 53. При появлении в информации символа Конец кадра дешифратор 55 сбрасывает триггер Пуск 59, останавливая при этом фотосчитыватель 13 меняя состояние триггера Запись- дублирование на противоположное и через схему 58 сброса сбрасывает счетчик 56 адреса в нулевое положение. При этом триггер Запись-дублирование 57 снимает разрешающий сигнал на запись информации в ОЗУ, выдает команду Дублирование ПЛ в блок 8 согласования и подключает через коммутатор 53 счетчик 56 адреса к элементу И 54. При наличии сигнала Готов ПЛ с блока 8 согласования по тактовым импульсам с логического блока 4 счетчик 56 адреса задает адрес считьшаемой информации с ОЗУ 60 через схему 62 совпадения в

5

5

блок 8 согласования. Последний снимает команду Готов ПЛ с элемента И 54 и осуществляет набивку этой информации на перфоратор 11. После набивки информации блок согласования восстанавливает сигнал Готов ПЛ и новая информация из ОЗУ 60 через блок 8 согласования набивается перфоратором 11. Так происходит до тех пор, пока не появляется символ Конец кадра. Б этом случае дешифратор 55 изменяет состояние триггера Запись-дублирование на противоположное и блок устанавливается в исходное состояние. Дублирование следующего кадра программы осуществлено только после очередного нажатия кнопки Пуск дублирования на клавиатуре 84 блока 6 управления.

Блок 8 согласования осуществляет согласование сигналов управления устройства с сигналами перфоратора 11 и блока 15 ЧПУ. При вводе информации на блок 15 ЧПУ с блока 3 микропрограмм поступает информация через схему ИЛИ 64 на элементы 66 и 67 совпадения и разрешающая команда Вкл. ЧПУ на элементы 67 совпадения, ин- 0 формация с которых через коммутатор

14поступает на блок 15 ЧПУ. При выводе информации на перфоратор 11 с блока 3 микропрограмм поступает числовая информация через схему ИЛИ 64

g на элементы 66 совпадения и команда Вкл. ПЛ через ИЛИ на триггер 65 готовности, который устанавливается в 1, снимает сигнал Готов ПЛ с блока микропрограмм и выдает разре0 шающий на элементы 66 совпадения . Информация через блок 68 согласования с ПЛ поступает на перфоратор 11 и набивается на перфоленту. После ее набивки по синхроимпульсам перфо-. ратора сбрасывается триггер 65 готовности, восстанавливая сигнал готовности в блок 3 микропрограмм и снимается разрешающий сигнал элементов 66 совпадения. Аналогично осуществляется работа блока в режиме дублирования при подаче информации и команды Дубл. ИЛ с блока 7 перезаписи. Для фрагментов программы, которые могут быть одновременно выведены в блок

15ЧПУ и на перфоратор 11, с блока 3 микропрограмм поступает информация на элемент ИЛИ 64 и две команды Вкл. ПЛ и Вкл. ЧЛУ. При этом синхронизация осуществляется по сиг5

0

5

налам более медленно де ствующего перфоратора. С целью упрощения связей на блоке не показаны сигналы синхронизации Старт/стоп для блока 15 ЧПУ.

Вычислитель 10 является стандартным блоком и раскрыт для показа его связей с интерфейсом 9 вычислителя.

Ввод информации в вычислитель 10 мож..т осуществляться от блока 12 ввода информации через узел 72 ввода и узел 74 согласования при отсутствии сигнала Разрешение ввода с логического блока 4. Кроме того, ин- формация может осуществляться также из шины данных при наличии сигнала Разрешение ввода с логического блока 4. Синхронизация ввода осуществляется по D-импульсам динамической раз вертки вычислителя. При появлении сигнала Разрешение ввода узел ввода снимает сигнал Готовн. в блок 5 программных переходов, который восстанавливается по D-импульсам вычислителя 10 после ввода информации в вычислитель 10.

Информация с индикатора 76 вычислителя через преобразователь кода 75 переносится последовательно в ре- версивный регистр 73 по синхроимпульсам D (9 импульсов) вычислителя 10 и одновременно фиксируются ее признаки в формирователе 69 признака, представляющем собой два триггера, управ ляемых дешифраторами, и счетчик. При этом, если во всех разрядах числа находятся нули, счетчик переполняясь устанавливает первый триггер в 1. Если хотя бы в одном из разрядов на- ходится число, отличное от нуля, то счетчик сбрасывается и одновременно сбрасьшается триггер. Этот триггер формирует признак 0. Второй триг- гер формирует признак О по знаково му разряду (синхроимпульс D9). При этом если число положительное, то триггер устанавливается в 1, а если отрицательное, то в О.

Число на индикаторе 76 вычислите- ля представляется с плавающей запятой, поэтому введен узел 71 нормализации, представляющий собой дешифратор и логические элементы И.

Запись числа с индикатора 76 в реверсивный регистр осуществляется при появлении с блока 3 микропрограм команды Запись на узел 71 иормали- зации, который формирует разрешающий

5 5

0 5 0 5

0

g

сигнал на запись числа в реверсивный регистр 73. После записи числа (по синхроимпульсам D) узел 71 нормализации по тактовым импульсам с логического блока 4 формирует сигналы сдвига вправо в реверсивный регистр 73 до тех пор, пока в младшем разряде не появится код точки (запятая). При появлении кода точки с младшего разряда реверсивного регистра 73 узел 71 нормализации прекращает сдвиг и вьщает разрешающий сигнал на узел 70 сдвига, который представляет собой счетчик, триггер и логический элемент И. При поступлении информаг . ции о модуле сдвига и команды Сдвиг с блока 3 микропрограмм эта информация заносится в счетчик. Триггер устанавливается в 1 разрешающим сигналом с узла 71 нормализации и вьщает разрешаюш 1й сигнал на элемент И. Тактовые импульсы логического блока 4 через элемент И поступают на вычитающий вход счетчика, в блок 3 микро- программ и на сдвиг влево реверсивного регистра 73. Информация с реверсивного регистра 73 при этом переносится в блок 3 микропрограмм и блок 2 индикации при наличии сигнала Занос с блока микропрограмм (выбор системы координат). Счетчик узла 70 сдвига обнуляется и сбрасывает триггер, приводя схему в исходное состояние.

Коммутатор 14 при наличии сигнала Адрес 1 с блока 6 управления подключает выход фотосчитывателя 13 к блоку 7 перезаписи через электронный ключ 82. При отсутствии сигнала Адрес 2 мультиплексор 83 подключает к блоку 15 ЧПУ фотосчитьшатель 13, а при его наличии - блок 8 согласования.

Б режиме программы, выбираемом переключателем 86 рода работ, шифратор 87 адреса выдает на коммутатор по адресу 1 и адресу 2 сигналы логического нуля, в режиме обучения по адресу 1 - логический нуль, по адресу 2 - логическая единица, в режиме дублирования по адресу 1 - логическая единица, а по адресу 2 - логический нуль.

При нажатии любой из кнопок кла- |Виатуры 84, кроме кнопки Пуск дублирования, блок 85 выбора программ формирует Выбор программы и Пуск

в блок программных переходов, формирует сигнал Запрет памяти в блок 1 памяти для отключения блока памяти от шины данных и задает в шину данных адрес начала выполняемой программы. При вьэтолнении какой-либо про- rpar-sMHf закрепленной за кнопками кла 84, с блока программных переходов приходит команда Счет, бло кирующаЯ клавиатуру до завершения выполнения программы, Синхронизация работы блока 85 выборки программ осуществляется от тактовых импульсов логического блока 4, которые поступают на счетчик-шифратор, 90 Последний через коммутатор 88 осуществляет опрос клавиатуры 84, Информация .о нажатой кнопке при отсутствии сигнала Счет с блока программных переходов фиксируется фиксатором 89, который формирует сигнал записи адреса кнопки в буфер 92 кода nporpaiviMo При отпускании кнопки фиксатор 89 выдает разрешающий сигнал на счетчик 91 четырех тактов, который по первому тактовому импульсу с логического блока 4 вьщает команду Запрет памяти в блок 1 памяти5 которая сн:имается четвертьм тактом счетчика 91 и команду Пуск 3 блок 5 программных переходов. По второму тактовому импуль- су выдается комавда Выбор програм- :мы в блок 5 программных переходов. По третьему тактовому импульсу через формирователь 94 в шину данных выдается младшая часть адреса (первьш байт)„ По четвертому тактовому импульсу вьщается старшая часть аДреса (второй байт) в шину данных и осуществляется сброс фиксатора 89 в исходное состояние. Фиксатор 89 состоит из двух триггеров и элементов И и НЕ, Первый триггер устанавливается в при нажатии кнопки на клавиатуре 84 и отсутствии сигнала. Счет с блока 5 программных перехо-- дон. При отпускании кнопки устанавливается в 1 второй триггер. Сброс обоях триггеров осзпцествляется от счетчика 91 четырех тактов. Формирователь 94 начального адреса программы представляет собой два шифратора- информационные входы которых подключены к буферу кода программы, выходы объединены по схеме ИЛИ, а управляющие входы подключены соотззетственно к третьему и четвертому тактам счет -- чика четырех тактов . .

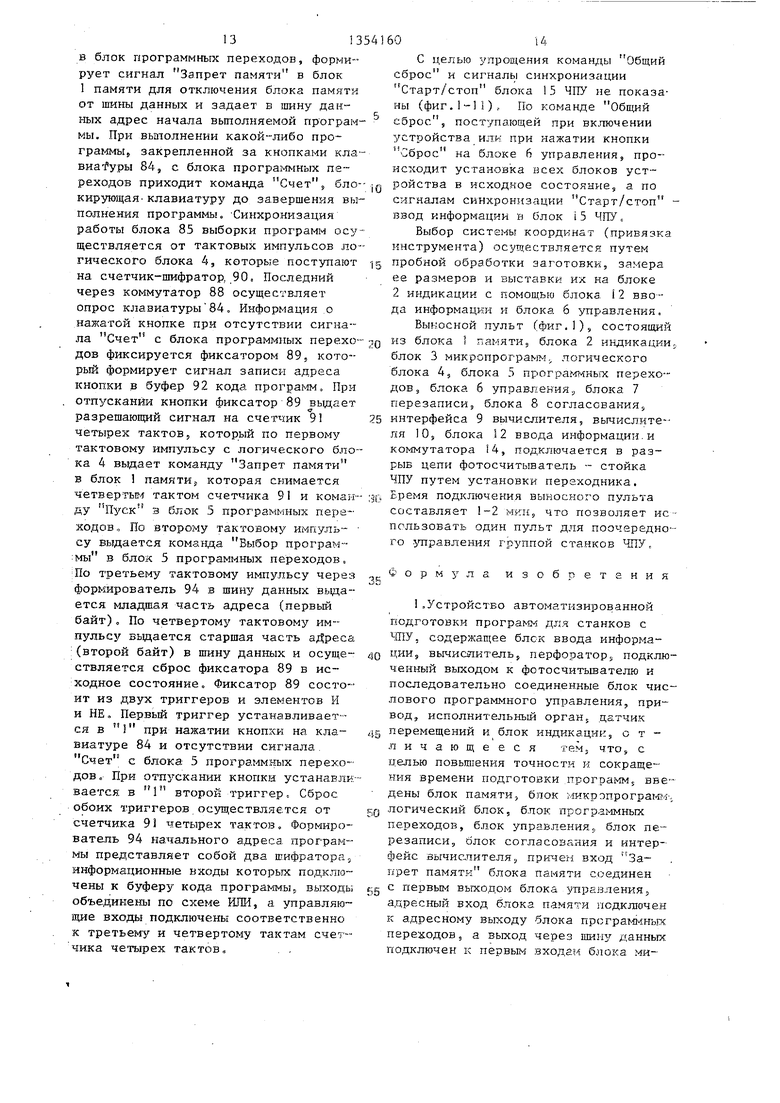

С целью упрощения коман/,ы Общий сброс и сигналы синхронизации Старт/стоп блока 15 ЧПУ не показаны (фиг.1-11), По команде Общий

сброс, поступающей при включении устройства или при нажатии кнопки Сброс на блоке 6 управления, происходит установка всех блоков устройства в исходное состояние, а по сигналам синхронизации Старт/стоп - ввод информации в блок 15 ЧПУо

Выбор системы координат (привязка инструмента) осуществляется путем

пробной обработки заготовки, замера ее размеров и выставки их на блоке 2 индикации с помощью блока i 2 ввода информации и блока б управления Выносной пульт (фиг,), состоящий

из блока I памятиS блока 2 индикации, блок 3 микропрограмм., логического блока 4, блока 5 пpoгpa гr.{ныx переходов, блока 6 управления, блока 7 перезаписи, блока 8 согласования,

интерфейса 9 вычислителя, вычислителя 10, блока 12 ввода информации.и коммутатора 14, подключается в разрыв цепи фотосчитываталь - стойка ЧПУ путем установки переходника.

Бремя подключения выносного пульта составляет 1-2 мин, что позволяет ис пользовать один пульт для поочередного управления группой станков ЧПУ.

Ф о р .м у л а изобретения

1.Устройство автоматизированной подготовки программ дл.ч станков с ЩУ. содержащее блек ввода информадни, вычислитель, перфоратор, подключенный выходом к фотосчитьшателю и последовательно соединенные блок числового программного управления, привод, исполнительный орган, датчик

перемещений индикации, о т - .п и ч а ю щ е е с я темэ что, с целью повьш:ения точности и сокращения времени подготовки программ, введены блок памяти, блок микропрограмм-.

логический блок, блок программных переходов, блок управления, блок перезаписи, блок согласования и интерфейс вычислителя, причега вход Запрет памяти блока памяти соединен

с первым выходом блока упра зления5 адресный вход блока памяти подключен к адресному выходу блока пр(зграм1у ньш переходов, а выход через шину данных подключен к первым входам блока ми

кропрограмм, логического блока, блока программных переходов и интерфейс вычислителя, выход Занос блока микропрограмм соединен с установочным входом блока индикации, информационный выход блока микропрограмм соединен с первым информагщонным входом блока согласования, выходы Модуль сдвига, Запись и Сдвиг подключены к соответствующим входам интерфейса вычислителя, управляющие выходы подключены к. соответствующим управляющим входам блока согласования, второй вход логического блока соединен с выходом Команда принята блока программнь х переходов, синхро- низирзтощий выход логического блока соединен с синхронизирующими входами блока микропрограмм, блока про- граммных переходов, блока перезаписи, блока согласования, интерфейса вычислителя и блока управления, выход Старт логического блока подключен к входу блока микропрограмм, вы- ходы логического блока Команда перехода и Ответ логического блока подключены к соответствующим входам блока программных переходов, выход Разрешение ввода логического блока подключен к управляющему входу интерфейса вычислителя, вход Общая готовность блока программных переходов соединен с выходами готовности блока микропрограмм и интерфейса вычислителя, вход условия блока программных переходов соединен с выхо- ходами условия логического блока и интерфейса вычислителя, входы выбор программы и пуск блока про граммных переходов соединены с соответствующими выходами блока управления, выход счет блока программных переходов подключен к блокирующему входу блока управления, управляющий выход пуск дублирования блока управления соединен с блоком перезаписи, информационный выход блока управления подключен к шине данных, управляющие выходы Адрес 1 и Ад- рее 2 соединены с управляющими входами коммутатора, информационный вход блока перезаписи подключен к первому информационному выходу коммутатора, второй информационный выход коммутатора соединен с входом блока числового программного .управления информационный выход блока перезаписи соединен с вторым информационным

входом блока -управления, выход Старт блока перезаписи подключен к управляющему входу фотосчитывателя, выход дублирование блока перезаписи соединен с входом блока согласования рыход Готов ПЛ блока согласования соединен с входами блока перезаписи и блока микропрограмм, второй синхронизирующий вход блока COTJ; гласования соединен с синхронизирую-, щим выходом перфоратора, первый информационный выход блока согласования подключен к перфоратому, а второй информационный выход - к первому информационному входу коммутатора, второй информационный вход которого соединен с выходом фотосчитывателя, первый информационный вход интерфейса вычислителя соединен с входом блока ввода информации, а второй информационный вход - с вычислителем, информационный выход Число интерфейса вычислителя соединен с информационными входами блока микропрограмм и блока индикации, второй информационный выход интерфейса вычислителя соединен с вьгчислителем, синхронизирующий вход D интерфейса вычислителя соединен с вычислителем, а выход D - с блоком ввода информации, выход Сдвиг.интерфейса вычислителя соединен с блоком микропрограмм.

2.Устройство по п.1, о т л и - чающееся тем, что блок микропрограмм содержит шифратор модуля сдвига, шифратор кода букв, шифратор кода цифр, шифратор команд программы, счетчик команд, коммутатор, дешифратор микрокоманд, элемент И, триггер готовности и преобразователь кода, причем входы шифратора модуля сдвига, шифратора кода букв и шифратора ко-, манд программы подключены к шине данных, выход шифратора модуля сдвига подключен к интерфесу вычислителя, информационный вход и вход Сдвиг преобразователя кода являются информационным и пусковым входами блока микропрограмм, а выход соединен с входом шифратора кода цифр, ииформа-г ционные входы коммутатора подключены к выходам шифратора кода букв и шифратора кода цифр соответственно, а информационный выход является выходом блока микропрограмм, управляющий вход коммутатора подключен к управляющему выходу шифратора команд программы , информационный вход дешиф17

1354

ратора микрокоманд соединен с информационным выходом шифратора команд программы, а управляющие выходы дешифратора микрокоманд подключены соответственно к соответствующим управляющим выходам, вход установки триггера готовности подключен к входу Старт блока, инверсный выход триггера готовности подключен к выходу блока микропрограмм, а прямой выход триггера готовности подключен к входу коммутатора и дешифратора микрокоманд, первый и второй входы элемента И подключены соответственно к синхронизирующему входу блока микропрограмм и к выходу дешифратора микрокоманд, а выход соединен с суммирующим входом счетчика команд, информационный выход которого подключен к второму входу шифратора команд программы.

3.Устройство по п.1, о т л и - чающееся .тем, что логический блок содержит задающий генератор, дешифратор машинных команд, дешифратор условий, триггеры условий и формирователь ответа, причем выходы заадющего генератора соединены с соответствующими синхронизирующими выходами логического блока, вход Команда принята подключен к разрешающему входу дешифратора машинных команд, информационные входы дешифратора машинных команд и дешифратора условий подключены к шине данных, первые управляющие выходы дешифратора машинных команд подключены к соответствующим выходам логического блока, второй управляющий выход - к первому входу формирователя объекта, а третий управляющий выход - к разрешающему входу дешифратора условий, управляющее выходы которого подключены к управляющим входам триггеров условий, выходы которых подключены к информационным выходам логического Яблока, выход Условия дешифратора условий через формирователь ответа подключен к выходу Ответ логического блока.

4.Устройство по п.1, отличающееся тем, что блок программных переходов содержит фиксатор, анализатор условий, триггер Останов, счетчик трех тактов, три:- гер перехода, анализатор ответа системы, буферный регистр, узел измене- ния адреса, узел инкрементирования

0

5

0

5

0

5

0

5

0

5

6018 .

и счетчик команд, первый управляющий вход которого соединен с первым выходом узла изменения адреса, второй управляющий вход - с выходом узла инкрементирования, первым входом подключенного к второму выходу узла изменения адреса, вторым входом - к выходу триггера Останов, третьим входом - к первому выходу, анализато- ра ответа системы, второй выход KOV торого соединен с выходом блока программных переходов, первый вход - с выходом фиксатора, второй вход - с синхронизирующим входом блока про-, граммных переходов, третий вход - с входом Ответ логического блока программных переходов, вход Общая готовность которого подключен к четвертому входу анализатора ответа системы, выход фиксатора соединен с разрешающими входами счетчика трех тактов и триггера перехода, первый и второй выходы счетчика трех тактов соединены с уСтановочньсми входами буферного регистра, а третий выход - с сбросовым входом фиксатора и с первым входом узла изменения адреса, первый информационный вход анализатора условий соединен с входами условий блока программных переходов, второй информационный вход - с шиной данных, выход анализатора условий подключен к второму входу триггера перехода, выход которого соеди- ;нен с вторым входом узла изменения адреса, вход Пуск блока программных переходов соединен с управляющим, вхо- дом триггера Останов, выход которого соединен с выходом блока программных переходов, а информационные входы - с шиной данных, вход Выбор программы - с первым входом фиксатора, а вход Команда перехода с вторым входом фиксатора, информационный выход счетчика команд подключен к адресному выходу блока программных переходов, а информационные входы счетчика команд - к вьгходу бу-. ферного регистра.

5.Устройство по п.1, о т л и - чающееся тем, что блока перезаписи содержат коммутатор, элемент И, два элемента совпадения, дешифратор Конец кадра, элемент сброса, счетчик адреса, триггеры Пуск и Запись-дублирование и элемент памяти, причем установочный вход триггера Пуск соединен с входом Пуск

дублирования блока перезаписи, выход дешифратора Конец кадра соединен со счетным входом триггера Запись-дублирование, сбросовым входом триггера Пуск и через элемент сброса со сбросовым входом счетчика адреса, выход триггера Пуск соединен с выходом Старт/стоп блока перезаписи, первый выход триггера Запись-дублирование соединен с выходом Дублирование ЦП блока перезаписи, разрешающим входом второго эления, входы блока элементов ИЛИ г.о.еди нены соответственно с информационными входами блока согласования, а выход - с информационными входами первого и второго элементов совпадения, вход Включить ЧПУ соединен с разрешающим входом второго элемента совпадения, выход первого узла элементов совпадения через узел согласования соединен с информационным выходом блока согласования, а выход второго узла элементов совпадения соединен с информационным входом блока перезаписи.

7.Устройство по п.1, о т л и мента совпадения и с управляющим входом коммутатора, второй выход тригге-15 ра Запись-дублирование подключен к разрешающему входу первого элемента, совпадения, информационный вход первого элемента подключен к первому информационному входу коммутатора, 20 выход второго элемента совпадения соединен с информационными входами элемента памяти, первый и второй входы элемента И соединены соответственно с синхронизирующим входом бло- 25 ного регистра, формирователя признака перезаписи и с выходом Готов ПЛ ка, узла нормализации, узла ввода и блока перезаписи, выход элемента; И блока ввода информации, информацион- соединен с первым входом коммутато- ный вход интерфейса вычислителя че.чающееся тем, что интерфейс вычислителя содержит формирователь признака, узел сдвига, узел нормализации, узел ввода, реверсивный регистр, узел согласования и преобразователь кода, причем синхронизирующий вход интерфейса вычислителя соединен с синхронизирующими входами реверсивра, второй вход которого подключен к синхронизирующему входу блока перезаписи, выход коммутатора подключен к суммирующему входу счетчика адреса, информационный выход счетчика адг реса соединен с адресным входом элемента памяти, информационный выход которого соединен с информационным входом второго элемента совпадения и с входом дешифратора Конец кадра, выход второго элемента совпадения подключен к информационному выходу блока перезаписи,

6.Устройство поп,1, отличающееся тем, что блок согласования содержит элемент РШИ, блок элементов 1ШИ, триггер готовности, два узла элементов совпадения и блок согласования с перфоратором, вход Дублирование ПЛ блока согласования соединен с первым входом элемента . ШШ, вход которого соединен с входом Включить ЦП блока, выход элемента :ИЛИ с установочнымвходом триггера готовности, сбросовый вход которого подключен к синхронизирующему входу

рез преобразователь кода соединен

30 с информационными входами преобраз вателя признака и реверсивного регистра, информационный выход форми рователя признака является выходом УСЛОВИЯ, интерфейса вычислителя,

сдвиговый выход узла сдвига соедин со сдвиговым входом реверсивного р гистра и выходом Сдвиг интерфейс вычислителя, второй сдвиговый вход реверсивного регистра соединен с

4Q выходом узла нормализации, информа ционный выход младшего разряда рев сивного регистра соединен с информ ционным входом узла нормализации, информационный выход старшего разр

45 да реверсивного регистра подключен к информационному выходу интерфейс вычислителя, информационный вход у ла сдвига соединен с выходом Моду сдвига интерфейса вычислителя, вт рые синхронизирующие входы узла сд га и узла нормализации соединены с синхронизирующим входом интерфей вычислителя, управляющий вход узла сдвига подключен к управляющему вх

50

блока согласования, инверсный выход gg ду Сдвиг интерфейса вычислителя.

триггера готовности соединен с выходом Готов ПЛ блока согласования, а прямой выход подключен к разрешающему входу первого элемента совпадеразрешающий вход узла сдвига соеди нен с разрешающим выходом узла нор мализации, управляющий вход узла н мализации подключен к управляющему

ния, входы блока элементов ИЛИ г.о.еди- нены соответственно с информационными входами блока согласования, а выход - с информационными входами первого и второго элементов совпадения, вход Включить ЧПУ соединен с разрешающим входом второго элемента совпадения, выход первого узла элементов совпадения через узел согласования соединен с информационным выходом блока согласования, а выход второго узла элементов совпадения соединен с информационным входом блока перезаписи.

7.Устройство по п.1, о т л и ного регистра, формирователя признака, узла нормализации, узла ввода и блока ввода информации, информацион- ный вход интерфейса вычислителя ченого регистра, формирователя признака, узла нормализации, узла ввода и блока ввода информации, информацион- ный вход интерфейса вычислителя че.чающееся тем, что интерфейс вычислителя содержит формирователь признака, узел сдвига, узел нормализации, узел ввода, реверсивный регистр, узел согласования и преобразователь кода, причем синхронизирующий вход интерфейса вычислителя соединен с синхронизирующими входами реверсиврез преобразователь кода соединен

с информационными входами преобразователя признака и реверсивного регистра, информационный выход формирователя признака является выходом УСЛОВИЯ, интерфейса вычислителя,

сдвиговый выход узла сдвига соединен со сдвиговым входом реверсивного регистра и выходом Сдвиг интерфейса вычислителя, второй сдвиговый вход реверсивного регистра соединен с

выходом узла нормализации, информационный выход младшего разряда реверсивного регистра соединен с информационным входом узла нормализации, информационный выход старшего разряда реверсивного регистра подключен к информационному выходу интерфейса вычислителя, информационный вход узла сдвига соединен с выходом Модуль сдвига интерфейса вычислителя, вторые синхронизирующие входы узла сдвига и узла нормализации соединены с синхронизирующим входом интерфейса вычислителя, управляющий вход узла сдвига подключен к управляющему вхо

ду Сдвиг интерфейса вычислителя.

разрешающий вход узла сдвига соединен с разрешающим выходом узла нормализации, управляющий вход узла нормализации подключен к управляющему

214354160

входу Запись интерфейса вычислителя, информационные входы узла ввода подключены соответственно к шине данных, разрешающий вход узла ввода подключен к управляющему входу интерфейса вычислитепя, выход готовности узла, ввода подключен к выходу готовности интерфейса вычислителя, а информационный выход узла ввода через блок согласования соединен с информационным выходом интерфейса, вычислителя .

10 т

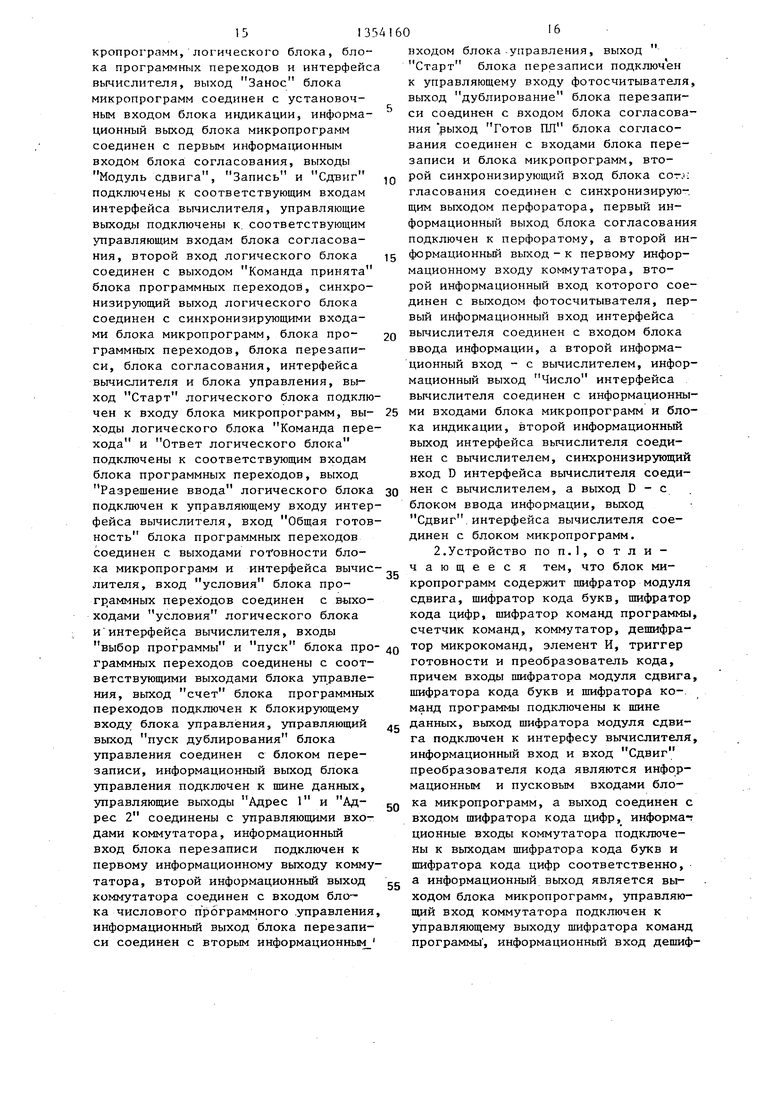

8.Устройство по п.1, о т л и - чающееся тем, что блок выбо- ра программ блока управления состоит из коммутатора, фиксатора состояния, счетчика-шифратора, счетчика четырех тактов, буфера кода програм- мы, формирователя внешних сигналов и формирователя адреса начала программы, причем суммирующие входы счетчика-шифратора и счетчика четырех тактов соединены с синхронизирую щим входом блока выбора программ, информационные выходы счетчика-шифратора подключены к информационному входу буфера кода программы и к первому информационному входу коммута- Topaj второй информационный вход

160

22

коммутатора подключен к входу блока выбора программы, а выход соединен с управляющим входом фиксатора состояния, разрешающий вход которого подключен к входу Счет блока выбора программ, первый управляющий выход фиксатора состояния подключен к разрешающему входу счетчика четырех 10 тактов, а второй - к управляющему

входу буфера кода программы, выход которого соединен с информационным входом формировате,пя адреса начала программы, выход первого и второго тактов счетчика четырех тактов соединены с входами формирователя внешних сигналов, выход третьего такта счетчика четырех тактов подключен к первому управляющему входу формирователя адреса начала программы, выход четвертого такта счетчика четырех тактов подключен к второму управляющему входу формирователя адреса начала программы, к сбросовому входу фиксатора состояния и к входу формирователя внешних сигналов, выход формирователя адреса начала программы подключен к шине данных, выходы формирователя внешних сигналов подключены соответственно к выходам Запрет памяти , Пуск и Bbi6op программы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Обучающее устройство | 1980 |

|

SU875434A1 |

| Графический дисплей с контролем | 1984 |

|

SU1249526A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для автоматизированной подготовки программ станков с ЧПУ. Цель изобретения - повышение точности и сокращение времени программ. Устройство автоматизированной подготовки программ для станков с ЧПУ содержит блок микропрограмм 3, блок согласования 8, блок перезаписи 7, блок памяти 1, блок управления 6, блок программных переходов 5, интерфейс вычислителя 9, блок ввода инфор-. мации 12, вычислитель 10, блок индикации 2, перфоратор 11, фотосчитыватель 13, коммутатор 14, блок ЧПУ 15 и логический блок 4, Включение процесса обработки в контур процесса создания программ на станке, т.к. в режиме обучения автоматически учитываются такие факторы, как погрешность установки исходного положения инструмента и упругие деформации системы СПИД, а введение режима дублирования обеспечивает более высокую оперативность подготовки программ. 7 3.п. ф-лы, 2 2 ил. с (Л оо СП 4 05

ч П/

22

От 5

23

ЛОч

вопрет J

памяти

щ

Omlf Omif

Modt//ib сдвига

bd

Готова

BS

иъшд

,6M9

От Ч От 6

.

Omt

От 6

писк дуЬлароВаний

Вт1Ц

Qmi Отв

6m 3 0ml

Cff C3

33 и 7

611

6 lit

ФигЛ

ОтВ 0ml

82

Отб

J

5/5

Лдр.2

Риг.9

Отб

01

Фиг. 12

ВШЛ В5

Qmlt OmS

s. 13

OmU

ТЦ

100

101

гЯ

105

551

101

JV

ffmS i/9

Omff

Odin, iffmofn.

Om& лог. 6fl.

lOZ

Фи2.15

Put 1

0m

От 50

652

Фиг. 16

ОЫЭ ftnTS

ОтП

Составитель И.Швец Редактор Н.Бобкова ТехредЛ„Сердюкова Корректор М.Шароши

Заказ 5691/42 Тираж 863 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и. открытий 113035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная., 4

т№ вт5

S92

Om&f 691

В 70

УЭ

Фи9.21

I&5

От91

Авторы

Даты

1987-11-23—Публикация

1986-03-21—Подача