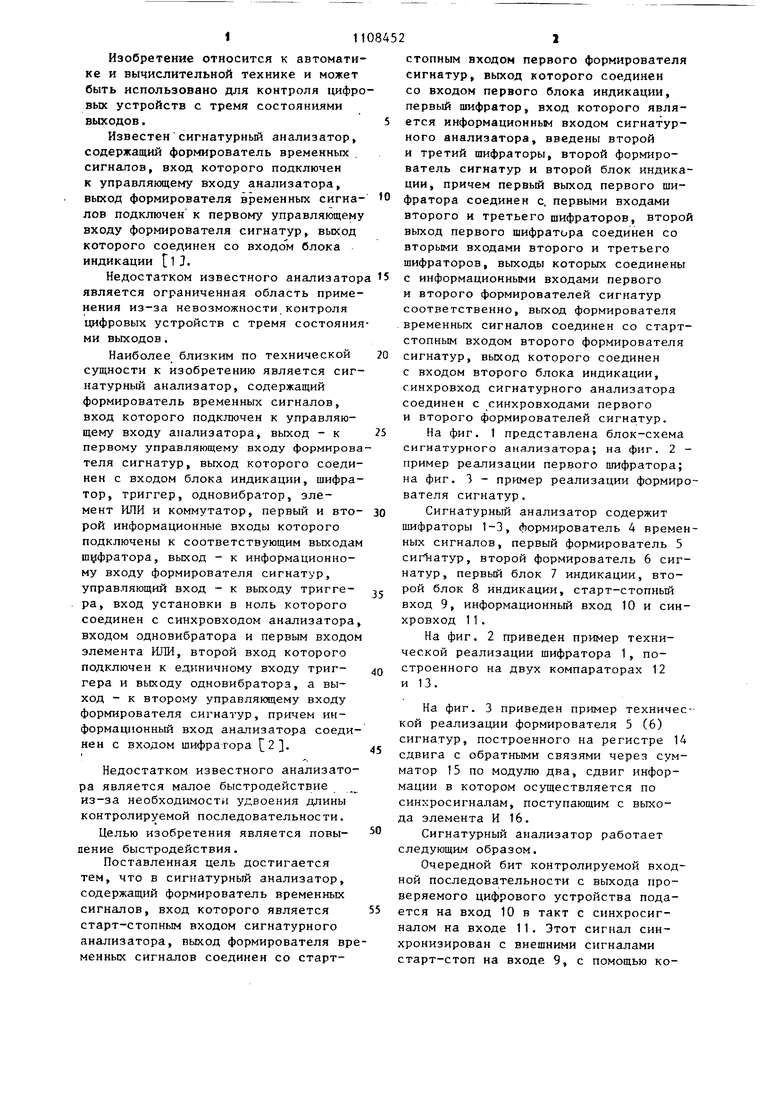

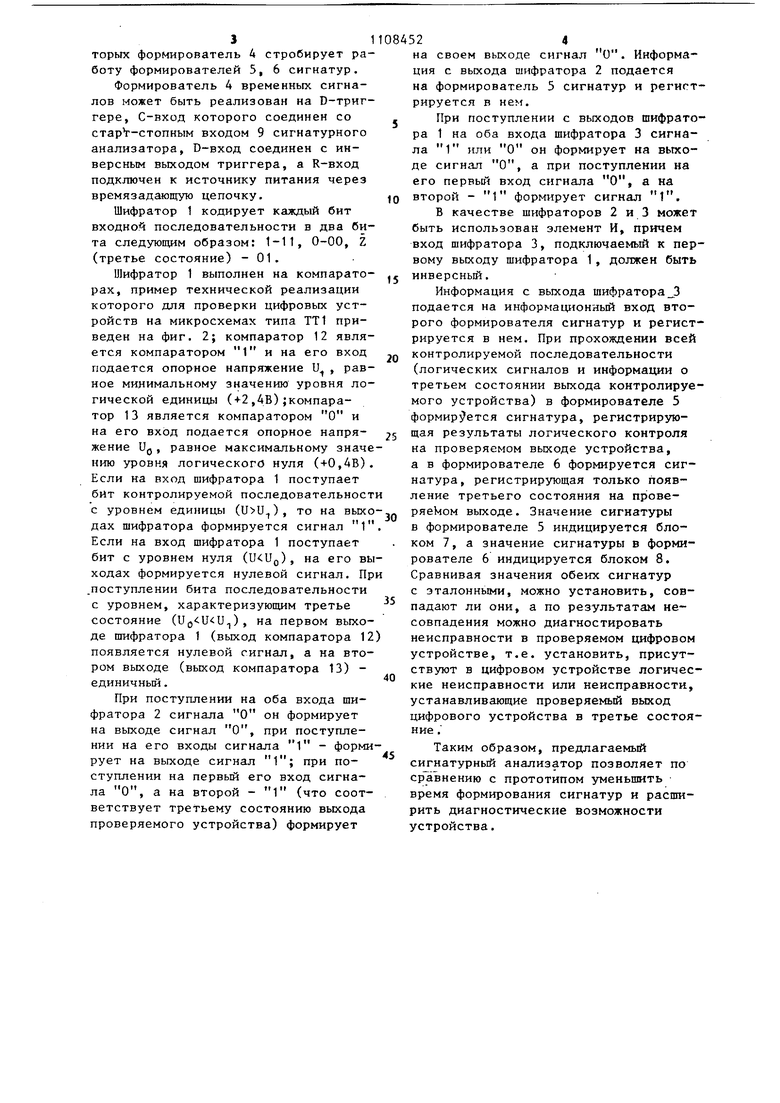

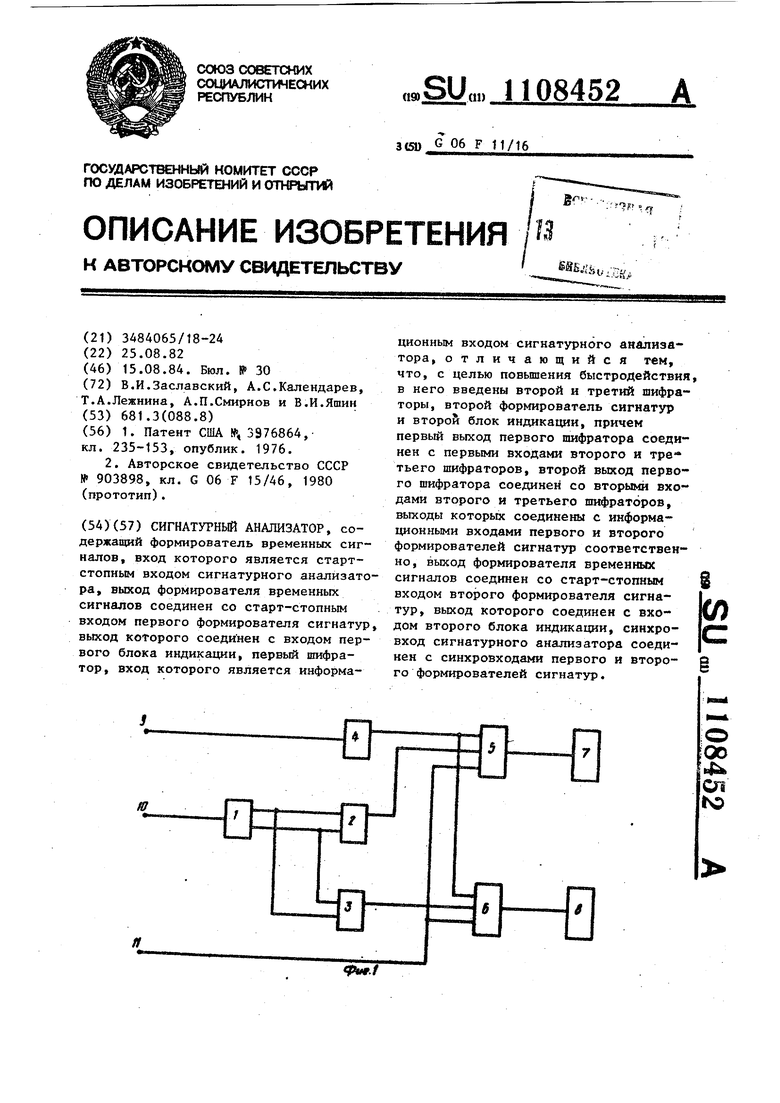

Изобретение относится к автомати ке и вычислительной технике и может быть использовано для контроля цифр вых устройств с тремя состояниями выходов. Известен сигнатурньй анализатор, содержащий формирователь временных сигнааов, вход которого подключен к управляклцему входу анализатора, выход формирователя временных сигна лов подключен к первому управляющем входу формирователя сигнатур, выход которого соединен со входом блока индикации t1J. Недостатком известного анализато является ограниченная область приме нения из-за невозможности контроля цифровых устройств с тремя состояни ми выходов. Наиболее близким по технической сущности к изобретению является сиг натурный анализатор, содержащий формирователь временных сигналов, вход которого подключен к управляющему входу анализатора, выход - к первому управляющему входу формиров теля сигнатур, выход которого соеди нен с входом блока индикации, шифра тор, триггер, одновибратор, элемент ИЛИ и коммутатор, первый и вто рой информационные входы которого подключены к соответствующим выхода шифратора, выход - к информационному входу формирователя сигнатур, управляющий вход - к выходу триггера, вход установки в ноль которого соединен с синхровходом анализатора входом одновибратора и первым входо элемента ИЛИ, второй вход которого подключен к единичному входу триггера и выходу одновибратора, а выход - к второму управлякщему входу формирователя сигнатур, причем информационный вход анализатора соеди нен с входом шифратора 2, Недостатком известного анализато ра является малое быстродействие из-за необходимости удвоения длины контролируемой последовательное ти. Целью изобретения является повыпение быстродействия. Поставленная цель достигается тем, что в сигнатурный анализатор, содержащий формирователь временных сигналов, вход которого является старт-CTonHbw входом сигнатурного анализатора, выход формирователя вр менных сигналов соединен со стартстопным входом первого формирователя сигнатур, выход которого соединен со входом первого блока индикации, первый шифратор, вход которого является информационным входом сигнатурного анализатора, введены второй и третий шифраторы, второй формирователь сигнатур и второй блок индикации, причем первый выход первого шифратора соединен с, первыми входами второго и третьего шифраторов, второй выход первого шифратора соединен со вторыми входами второго и третьего шифраторов, выходы которых соединены с информационными входами первого и второго формирователей сигнатур соответственно, выход формирователя временных сигналов соединен со стартстопным входом второго формирователя сигнатур, выход которого соединен с входом второго блока индикации, синхровход сигнатурного анализатора соединен с синхровходами первого и второго формирователей сигнатур. На фиг. 1 представлена блок-схема сигнатурного анализатора; на фиг. 2 пример реализации первого шифратора; на фиг. 3 - пример реализации формирователя сигнатур. Сигнатурный анализатор содержит шифраторы 1-3, формирователь 4 временных сигналов, первый формирователь 5 сигнатур, второй формирователь 6 сигнатур, первый блок 7 индикации, второй блок 8 индикации, старт-стопный вход 9, информационный вход 10 и синхровход 11 . На фиг. 2 приведен пример технической реализации шифратора 1, построенного на двух компараторах 12 и 13. На фиг. 3 приведен пример технической реализации формирователя 5 (6) сигнатур, построенного на регистре 14 сдвига с обратными связями через сумматор 15 по модулю два, сдвиг информации в котором осуществляется по синхросигналам, поступающим с выхода элемента И 16. Сигнатурный анализатор работает следующим образом. Очередной бит контролируемой входной последовательности с выхода проверяемого цифрового устройства подается на вход 10 в такт с синхросигналом на входе 11. Этот сигнал синхронизирован с внешними сигналами старт-стоп на входе 9, с помощью которых формирователь 4 стробирует работу формирователей 5, 6 сигнатур. Формирователь 4 временных сигналов может быть реализован на D-триггере, С-вход которого соединен со стар -стопным входом 9 сигнатурного анализатора, D-вход соединен с инверсным выходом триггера, а R-вход подключен к источнику питания через времязадающую цепочку. Шифратор 1 кодирует каждый бит входно последовательности в два бита следующим образом: 1-11, 0-00, Z (третье состояние) - 01. Шифратор 1 выполнен на компараторах, пример технической реализации которого для проверки цифровых устройств на микросхемах типа ТТ1 приведен на фиг. 2; компаратор 12 является компаратором 1 и на его вход подается опорное напряжение U , равное минимальному значению уровня логической единицы ( ,4В);компаратор 13 является компаратором О и на его вход подается опорное напряжение UQ , равное максимальному значе нию уровня логического нуля (+0,4В). Если на вход шифратора 1 поступает бит контролируемой последовательност с уровнем единицы (), то на выхо дах шифратора формируется сигнал 1 Если на вход шифратора 1 поступает бит с уровнем нуля (IKUg), на его вы ходах формируется нулевой сигнал. Пр .поступлении бита последовательности с уровнем, характеризующим третье состояние (U(), на первом выходе щифратора 1 (выход компаратора 12 появляется нулевой сигнал, а на втором выходе (выход компаратора 13) единичный. При поступлении на оба входа шифратора 2 сигнала О он формирует на выходе сигнал О, при поступлении на его входы сигнала 1 - форми рует на выходе сигнал при поступлении на первый его вход сигнала О, а на второй - 1 (что соответствует третьему состоянию выхода проверяемого устройства) формирует на своем выходе сигнал О. Информация с выхода шифратора 2 подается на формирователь 5 сигнатур и регистрируется в нем. При поступлении с выходов шифратора 1 на оба входа шифратора 3 сигнала 1 или О он формирует на выходе сигнал О, а при поступлении на его первый вход сигнала О, а на второй - 1 формирует сигнал 1. В качестве шифраторов 2 и 3 может быть использован элемент И, причем вход шифратора 3, подключаемый к первому выходу шифратора 1, должен быть инверсньй. Информация с выхода шифратора j3 подается на информационный вход второго формирователя сигнатур и регистрируется в нем. При прохождении всей контролируемой последовательности (логических сигналов и информации о третьем состоянии выхода контролируемого устройства) в формирователе 5 формируется сигнатура, регистрирующая результаты логического контроля на проверяемом выходе устройства, а в формирователе 6 формируется сигнатура, регистрирующая только появление третьего состояния на проверяеЫом выходе. Значение сигнатуры в формирователе 5 индицируется блоком 7, а значение сигнатуры в формирователе 6 индицируется блоком 8. Сравнивая значения обеих сигнатур с эталонными, можно установить, совпадают ли они, а по результатам несовпадения можно диагностировать неисправности в проверяемом цифровом устройстве, т.е. установить, присутствуют в цифровом устройстве логические неисправности или неисправности, устанавливающие проверяемый выход цифрового устройства в третье состояние . Таким образом, предлагаемый сигнатурный анализатор позволяет по сравнению с прототипом уменьшить время формирования сигнатур и расширить диагностические возможности устройства.

cpue.Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1988 |

|

SU1624459A1 |

| Сигнатурный анализатор | 1985 |

|

SU1297052A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Сигнатурный анализатор | 1982 |

|

SU1065857A1 |

| Сигнатурный анализатор | 1986 |

|

SU1361555A1 |

| Сигнатурный анализатор | 1985 |

|

SU1298771A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Сигнатурный анализатор | 1987 |

|

SU1434437A1 |

| Сигнатурный анализатор | 1984 |

|

SU1223231A1 |

| Сигнатурный анализатор | 1987 |

|

SU1589278A1 |

СИГНАТУРНЫЙ АНАЛИЗАТОР, содержаний формирователь временных сигналов, вход которого является стартстопным входом сигнатурного анализатора, выход формирователя временных сигналов соединен со старт-стопным входом первого формирователя сигнатур, выход которого соединен с входом первого блока индикации, первый шифратор, вход которого является информационным входом сигнатурного анализатора, отличающийся тем, что, с целью повьшения быстродействия, в него введены второй и третий шифраторы, второй формирователь сигнатур и второй блок индикации, причем первый выход первого шифратора соединен с первыми входами второго и тре- тьего шифраторов, второй выход первого шифратора соединен со вторыми входами второго и третьего шифраторов, выходы которьк соединены с информационньми входами первого и второго формирователей сигнатур соответственно, выход формирователя временных сигналов соединен со старт-стопным W входом второго формирователя сигнатур, выход которого соединен с входом второго блока индикации, синхровход сигнатурного анализатора соединен с синхровходами первого и второго формирователей сигнатур. /ff 00 4 СЛ 1С

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США №, 3976864, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сигнатурный анализатор | 1980 |

|

SU903898A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-15—Публикация

1982-08-25—Подача