Изобретение относится к вычислительной технике и может быть использовано в цифровых преобразователях.

Цель .изобретения - повьшение быстродействия,

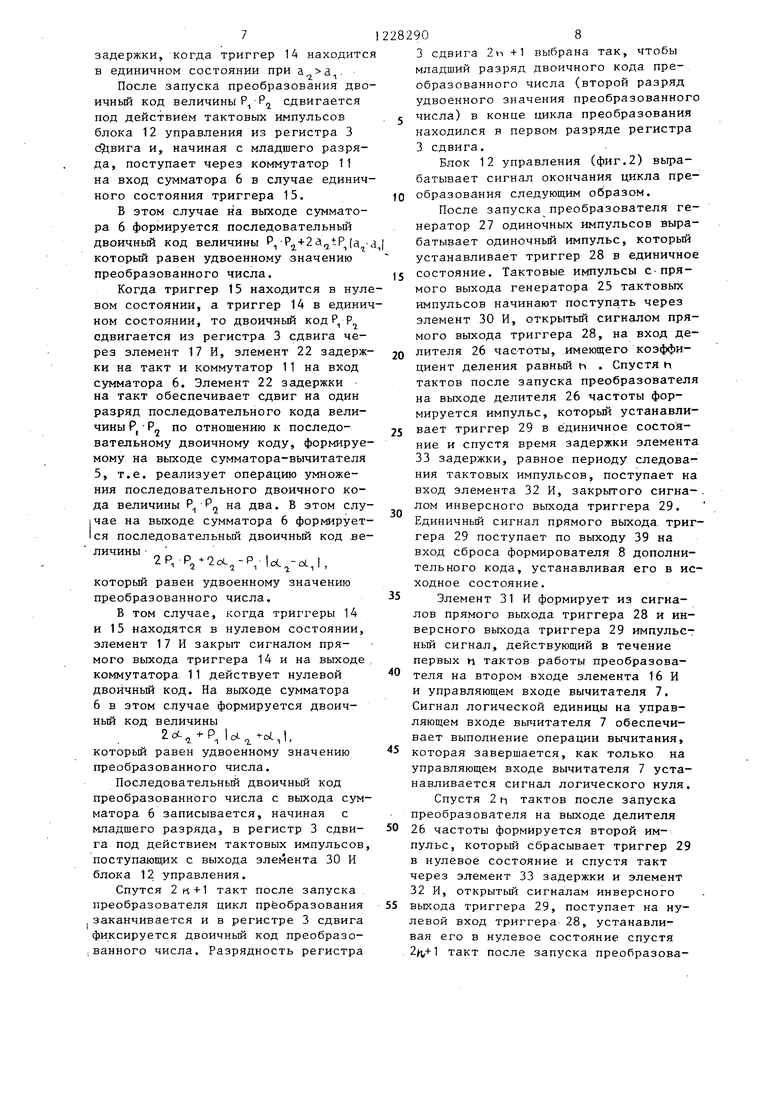

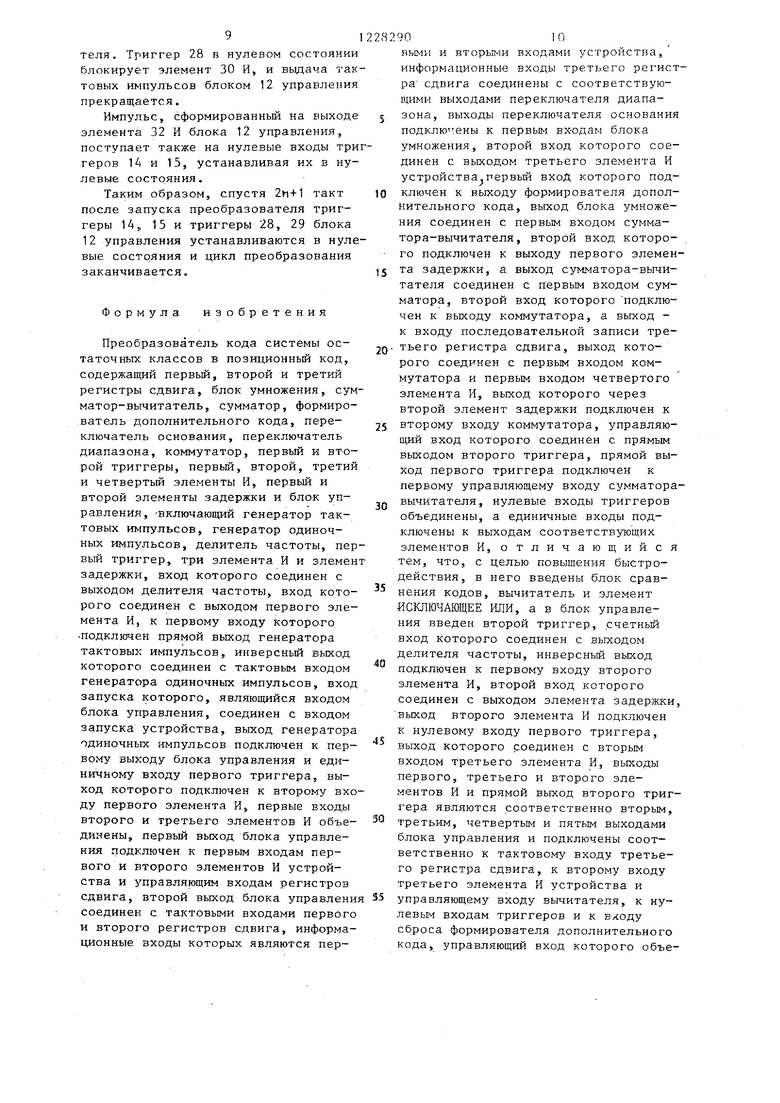

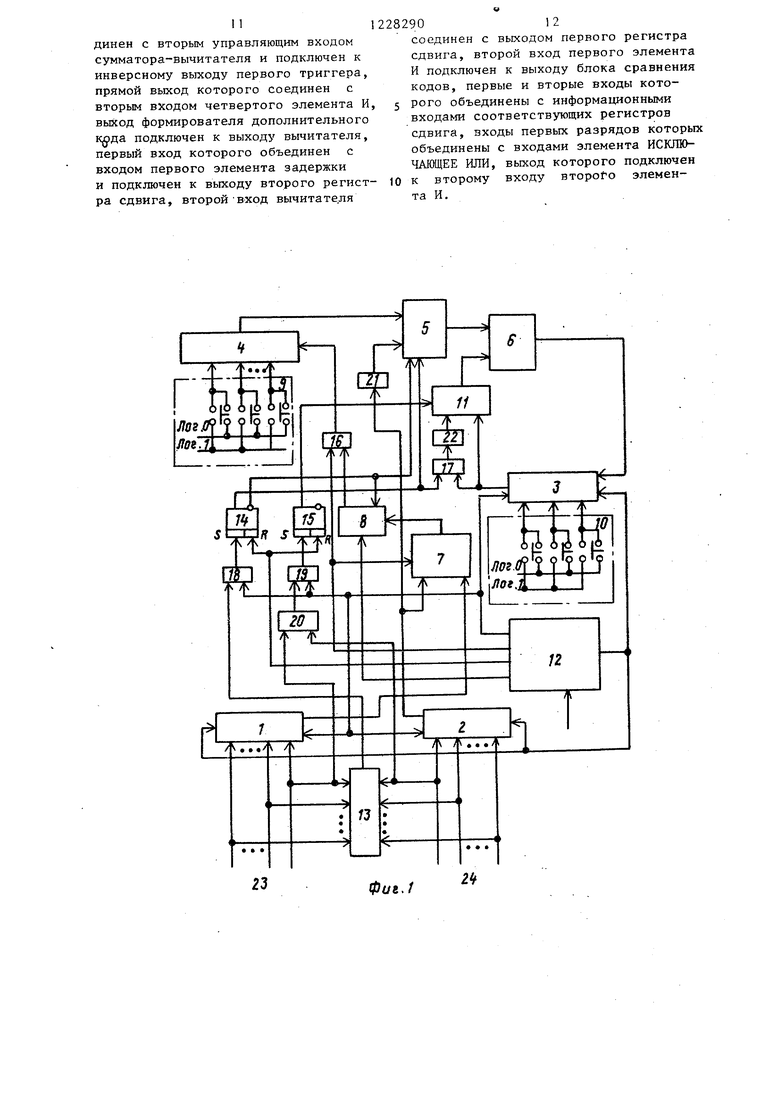

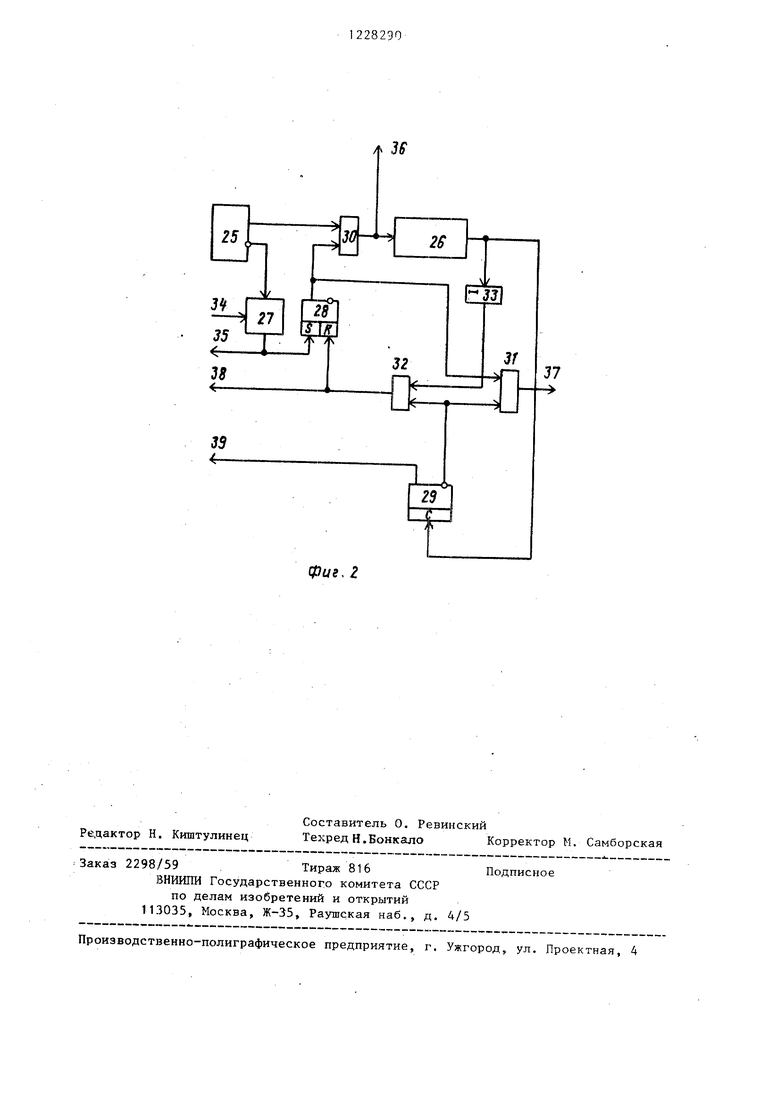

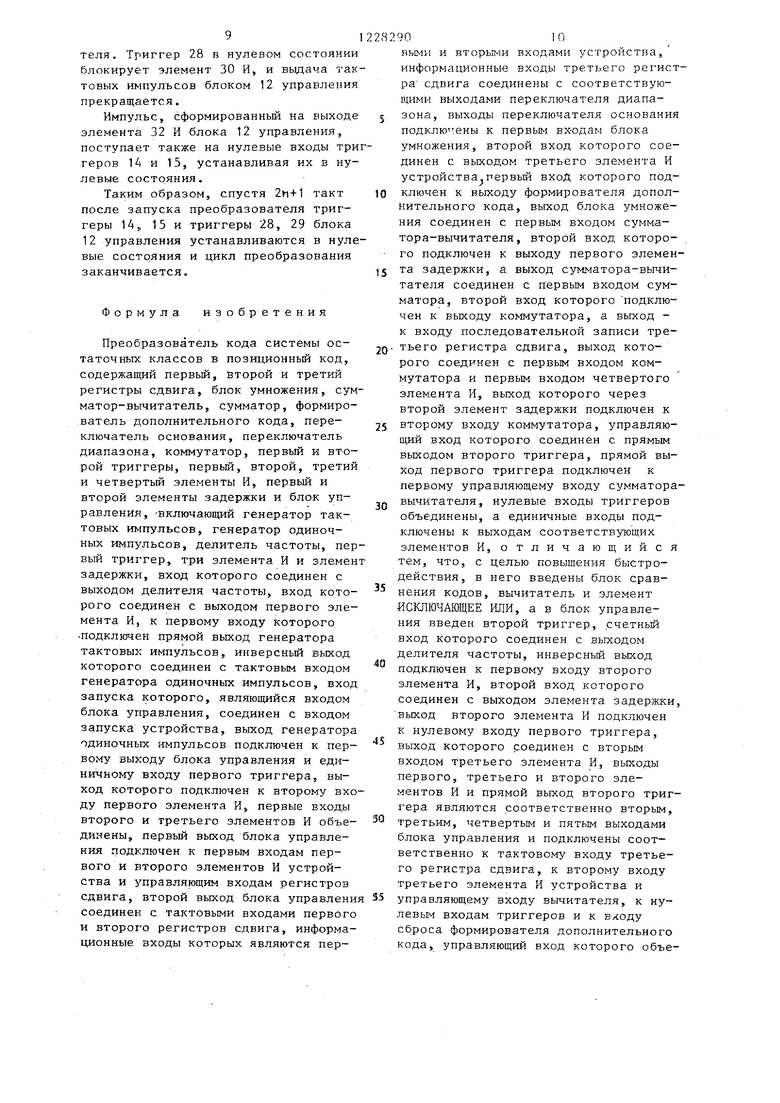

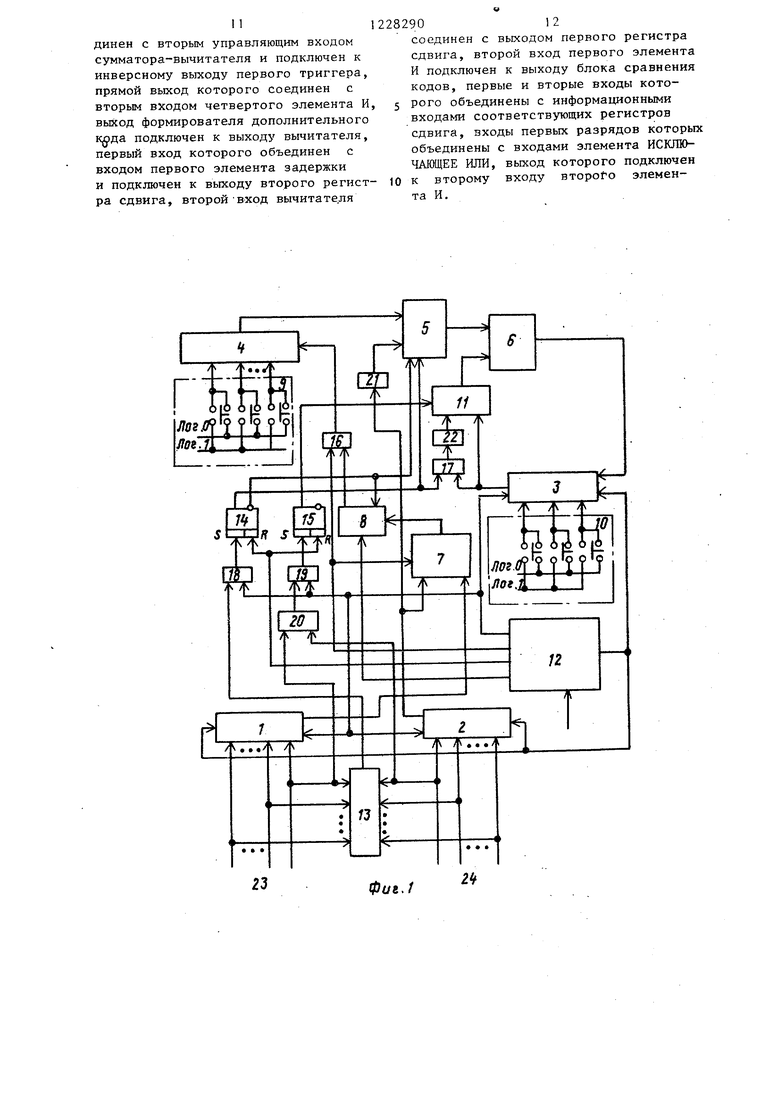

На фиг, 1 изображена функциональная схема преобразователя , на фиг, 2- функциональная схема блока управления ,

Преобразователь кода системы оста- точных классов в позиционный код содержит регистры 1-3 сдвига, блок 4 умножения, сумматор-вычитатель 5, сумматор 6, вычитатель 7, формирователь 8 дополнительного кода, пере- ключатель 9 основания системы остаточных классов, переключатель 10 диапазона представления чисел, коммутатор 11, блок 12 управленияJблок 13 сравнения кодов, RS-трйггеры 14 и 15, элементы 16-19 И, элемент 20 ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы 21 и 22 задержки, группы информационных входов 23 и 24 устройства.

Блок 12 управления (фиг,2) содержит генератор 25 тактовых импульсов, делитель 26 частоты, генератор 27 одиночных импульсов, RS -триггер 28, Т-триггер 29, элементы 30-32 И, элемент 33 задержки, вход 34 пуска преобразователя, первьй 35, второй 36, третий 37, четвертый 38 и пятьш 39 выходы блока управления. Входы управления занесением информации регистро 1-3 сдвига соединены с первым выходом 35 блока 12 управления, второй выход 36 которого соединен с тдк- товыми входами регистров 1-3 сдвига. Выход блока 4 умножения соединен с первым входом сумматора-вычитателя 5 выход которого соединен с первым входом сумматора 6, Выход вьгчитателя 7 соединен с входом формирователя 8 дополнительного кода, выход которого соединен с первым, входом элемента 16 И, Выход элемента 16 И соединен с входом блока 4 умножения, другие входы которого соединены с выходами переключателя 9 основания системы остаточных классов. Выходы переключателя 10 диапазона представления чисел соединены с информационными входами регистра 3 сдвига, вход последовательной записи которого соединен с выходом сумматора 6. Второй вход сум матора 6 соединен с входом коммутатора 11, первый информационньш вход которого соединен с выходом регистра

5

5 0

5

0

5

5

0

3 сдвига и с первым входом элемента 17 И, Второй вход элемента 16 И соединен с управляющим входом вычитате- ля 7 и с третьим выходом 37 блока 12 управления, четвертый выход 38 которого соединен с нулевыми входами триг- геров 14 и 15, Пятьй выход 39 блока 12 управления соединен с входом сброса формирователя 8 дойолнительного кода. Выход блока 13 сравнения кодов соединен с первым входом элемента 18 И, выход которого соединен с единичным входом триггера 14, Управ- . ляющий вход коммутатора 11 соединен с прямым выходом триггера 15, единичный .вход которого соединен с выходом элемента 19 И, первый вход которого подключен к выходу элемента 20 ИСКЛЮЧАЮЩЕЕ ИЛИ, Выход регистра 1 сдвига . соединен с входом вычитаемого вьгчитателя 7, вход уменьшаемого которого соединен с выходом регистра 2 сдвига и с входом элемента 21 задержки. Прямой и инверсньш выходы триггера 14 соединены с управляющими входами матора-вьиитателя 5, второй вход которого соединен с выходом элемента 21 задержки. Второй вход коммутатора 11 соединен через элемент 22 задержки с выходом элемента 17 И, второй вход которого соединен с прямым выходом триггера 14, инверсный выход которого подключен к управляющему входу формирователя 8 дополнительного кода. Вторые входы элементов 18 и 19 И соединены с первым выходом блока 12 управления.

Информационные входы 23 и 24 устройства соединены соответственно с первой и второй группами входов блока 13 сравнения кодов, Информа- циойные входы регистров 1 и 2 сдвига соединены соответственно с информационными входами 23 и 24 устройства. Первый и второй входы элемента 20. ИСКЛЮЧАЩЕЕ ИЛИ соединены с входами первых разрядов регистров 1 и 2 сдвига,.

Прямой выход генератора 25 тактовых сигналов (фиг, 2) блока 12 управления соединен с первым входом элемента 30 И, выход которого соединен с входом делителя 26 частоты. Инверсный выход генератора 25 тактовых сигналов соединен с тактовым входом генератора 27 одиночных импульсов, вход запуска которого соединен с входом 34 пуска преобразователя. Выход генератора 27 одиночных импульсов соединен с единичным входо триггера 28 и с выходом 35 блока 12 управления. Прямой выход триггера 28 соединен с вторым входом элемента 30 И и с первым входом элемента 31 И второй вход которого соединен с инверсным выходом триггера 29 и с первым входом элемента 32 И. Выход делителя 26 частоты соединен с счетным входом триггера 29 и через элемент 3 задержки - с вторым входом элемента 32 И, выход которого соединен с нулевым входом триггера 28.. Выходы элементов 30-32 И соединены соответственно с выходами 36-38 блока 12 управления. Прямой выход триггера 29 соединен с выходом 39 блока 12 управления. Выходы 35, 36, 37, 38 и 39 являются соответственно первым, вторым, третьим, четвертым и пятым выходами блока 12 управления.

Преобразователь кода системы остаточных классов в позиционньй код работает следующим образом.

В исходном состоянии триггеры 14 и 15 и триггеры 28 и 29 блока 12 управления находятся в нулевом состоянии, в которое они устанавливаются в результате предыдущего цикла преобразования.

С помощью переключателя 9 устанавливаются двоичный код основания Р системы остаточных классов, а переключателем 10 устанавливают диапазон представления чисел, равньй Р, Р, , где основания системы остаточных классов Р 6N -{- 1, P,j 6N- 1, N 1, 2, 3, ...; N- натуральный ряд чисел.

Переключатель 9 основания системы остаточных классов вьщает на параллельные входы блока 4 умножения сигналы логического нуля или логической единицы в зависимости от значения кода в разрядах двоичного числа ,

Переключатель 10 диапазона представления чисел выдает на параллельные входы ввода данных регистра 3 сдвига сигналы логического нуля или логической единицы в зависимости от значения кода в разрядах двоичного числа Р, P,j .

Запуск преобразователя осуществляется путем подачи сигнала догической единицы на вход 34 пуска преобразователя, который запускает генератор 27 одиночных импульсов блока 12 управления. По сигналу запуска генератор

282904

27 одиночных импульсов вырабатывает одиночный импульс в паузе между тактовыми импульсами генератора 25 тактовых импульсов. Выходной импульс генератора 27 одиночных импульсов устанавливает триггер 28 в единичное состояние и поступает с первого выхода 35 блока управления на входы управления занесением информации регистров 1-3 сдвига, а также на входы элементов 18 и 19 И. По этому сигналу в регистры 1-3 сдвига вводится исходная информация в виде параллельных двоичных кодов, а триггеры 14 и 15 устанавливаются в состояния, определяющие режим работы преобразователя. Регистр 3 сдвига содержит 2н+1 разряд, а регистры 1 и 2 сдвига -и разрядов, где h - количество разрядов представления остатков а и а

5

0

5

0

5

0

по основаниям Р, и Р системы остаточных классов.

Параллельные h -разрядные двоич-г ные коды остатков а, и д считываются соответственно с информационных входов 23 и 24 устройства и по импульсу генератора 27 одиночны импульсов блока 12 управления записываются в регистры 1 и 2 сдвига соответственно. Параллельный 2 и -разрядньй дво

ичный код Р Р диапазона представления чисел считывается с входов переключателя 10 и по импульсу генератора 27 одиночных импульсов блока 12 управления записывается в регистр 3 сдвига, старший 2п+1-й разряд которого находится в нулевом состоянии. Блок 13 сравнения кодов сравнивает два h -разрядных параллельных двоич- , ных кода остатков d и 4, действудо- щих на информационных входах 23 и 24 устройства соответственно, и вырабатывает на выходе сигнал логической единицы при ,, а в случае а, на выходе блока 13 сравнения кодов действует сигнал логического нуля.

В случае сигнал логической единицы на выходе блока 13 сравнения кодов открывает элемент 18 И, через которьш проходит импульс генератора 27 одиночных импульсов блока 12 управления и устанавливает триггер 14 в единичное состояние.

В случае й.и;) нулевой сигнал на выходе блока 13 сравнения кодов блокирует элемент 18 И и триггер 14 сохраняет нулевое состояние.

Элемент 20 ИСКЛЮЧАЮЩЕЕ ИЛИ сравнивает младшие разряды двоичных кодов остатков а и а s деиствуюпщх на первых информационных входах 23 и 24 устройства соответственно. Когда в младших разрядах двоичных кодов остатков а и а действуют различные сиг- налы, например логического нуля и логической единицы (комбинагдии кодов младших разрядов остатков или to), то на выходе элемента 20 ИСКЛЮЧАЮЩЕЕ ИЛИ формируется сигнал логической единицы, который открывает элемент 19 И. Выходной импульс генератора 27 одиночных импульсов блока 12 управления проходит через

20

Р -/ci/j-d, , который поступает, начиная с младшего разряда, на первый вход сумматора-вычитателя 5 Сумма- тор-вычитатель 5 устанавливается в режим суммирования, если триггер 14 находится в нулевом состоянии при ,, либо в режим вычитания, когда триггер 14 находится в единичном

элемент 19 И и устанавливает триггер 5 умножения формируется последова- 15 в единичное состояние.тальньй двоичный код произведения

В случае комбинации кодов младших разрядов остатков и 11 на выходе элемечта 20 ИСКЛЮЧАНЩЕЕ ИЛИ формируется сигнал логического нуля, который блокирует элемент 19 И и триггер 15 сохраняет нулевое состояние.

После установки триггера 28 блока 12 управления в единичное состоя- 2) состоянии при ,. Последователь- ние тактовые импульсы генератора 25 тактовых импульсов, действующие с частотой f , поступают через элемент 30 И на выход 36 блока 12 управления и на тактовые входы (управления сдвигом) регистров 1-3 сдвига.

Под действием тактовых импульсов генератора 25, тактовых импульсов блока .12 управления двоичные коды остатков а и а сдвигаются начиная с младшего разряда, с выходов ре30

ныи двоичньй код остатка а сдвигается, начиная с младшего разряда, под действием тактовых импульсов блока 12 управления на вход элемента 21 задержки на такт. Элемент 21 задержки обеспечивает сдвиг на один разряд последовательного двоичного кода остатка а по отношению к последовательному двоичному коду произведения Р , т.е. реализует операцию умножения двоичного кода остатка а 2 на два. Последовательньй дво- ичньш код величины 2 а поступает с выхода элемента 21 задержки на второй вход сумматора-вычитателя 5, ко- торьй в зависимости от режима суммирования или вычитания формирует Последовательньй двоичньй код величины

гистров 1 и 2 сдвига соответственно Вычитатель 7 выполняет последовательное вычитание из последовательного двоичного кода остатка а последовательного двоичного кода остатка а i а на выходе вычитателя 7 формируется последовательный двоичньй код разности остатков а , который, начиная с младшего разряда, по- ступае г на информационньй вход формирователя 8 дополнительного кода. Формирователь 8 дополнительного кода преобразует дополнительньм код разности остатков , в прямой код, если на его управляющий вход по ступает сигнал логической единицы с нулевого выхода триггера 14 в случае

ныи двоичньй код остатка а сдвигает ся, начиная с младшего разряда, под действием тактовых импульсов блока 12 управления на вход элемента 21 задержки на такт. Элемент 21 задержки обеспечивает сдвиг на один разряд последовательного двоичного кода остатка а по отношению к последовательному двоичному коду произведения Р , т.е. реализует операцию умножения двоичного кода остатка а 2 на два. Последовательньй дво- ичньш код величины 2 а поступает с выхода элемента 21 задержки на второй вход сумматора-вычитателя 5, ко- торьй в зависимости от режима суммирования или вычитания формирует Последовательньй двоичньй код величины

«

2oi,tP-|d,-ot,

Коммутатор 11 подключает выход регистра 3 сдвига к входу сумматора 6, если триггер 15 находится в еди- 50 ничном состоянии, либо подключает вход су1Ф1атора 6 к выходу элемента 22 задержки на такт, когда триггер 15 находится в нулевом состоянии. Элемент 17 И блокирует вход элемен- когда триггер 14 находится в единич- 5 та 22 задержки, если триггер 14 итги пропускает без изменения прямой код разности остатков

ном состоянии в случае .,. Таким образом, на выходе формирователя 8 дополнительного кода формируется поя , 82904

мой код абсолютной величины разности остатков (а,., который через элемент 16 И поступает, начиная с младшего разряда, на последовательный вход блока 4 умножения. Спустя И тактов после запуска преобразователя на третьем выходе блока 12 управления вырабатывается нулевой сигнал, блоки- руквдий управляющий вход вычитателя 7, а на пятом выходе блока 12 управления формируется сигнал логической единицы, устанавливающий по входу сброса формирователь 8 дополнительного кода в исходное состояние. На выходе блоШ

Р -/ci/j-d, , который поступает, начиная с младшего разряда, на первый вход сумматора-вычитателя 5 Сумма- тор-вычитатель 5 устанавливается в режим суммирования, если триггер 14 находится в нулевом состоянии при ,, либо в режим вычитания, когда триггер 14 находится в единичном

состоянии при ,. Последователь-

) состоянии при ,. Последователь-

ныи двоичньй код остатка а сдвигается, начиная с младшего разряда, под действием тактовых импульсов блока 12 управления на вход элемента 21 задержки на такт. Элемент 21 задержки обеспечивает сдвиг на один разряд последовательного двоичного кода остатка а по отношению к последовательному двоичному коду произведения Р , т.е. реализует операцию умножения двоичного кода остатка а 2 на два. Последовательньй дво- ичньш код величины 2 а поступает с выхода элемента 21 задержки на второй вход сумматора-вычитателя 5, ко- торьй в зависимости от режима суммирования или вычитания формирует Последовательньй двоичньй код величины

«

2oi,tP-|d,-ot,

ходится в нулевом состоянии при подключает выход регистра 3 сдвига к входу элемента 22

7

задержки, когда триггер 14 находитс в единичном состоянии при а а.

После запуска преобразования двоичный код величины сдвигается под действием тактовых импульсов блока 12 управления из регистра 3 (фвига и, начиная с младшего разряда, поступает через коммутатор 11 на вход сумматора 6 в случае единичного состояния триггера 15.

В этом случае на выходе сумматора 6 формируется последовательный двоичньй код величины Р P, который равен удвоенному значению преобразованного числа.

Когда триггер 15 находится в нулвом состоянии, а триггер 14 в единином состоянии, то двоичньй код Р Р, сдвигается из регистра 3 сдвига через элемент 17 И, элемент 22 задержки на такт и коммутатор 11 на вход сумматора 6. Элемент 22 задержки на такт обеспечивает сдвиг на один разряд последовательного кода величины по отношению к последовательному двоичному коду, формируемому на выходе сумматора-вычитателя 5, т.е. реализует операцию умножения последовательного двоичного кода величины Р Р,2 два. В этом случае на выходе сумматора 6 формируется последовательный двоичный код величины „

2P,-P,,-U,-.tJ,

который равен удвоенному значению преобразованного числа.

В том случае, когда триггеры 14 и 15 находятся в нулевом состоянии, элемент 17 И закрыт сигналом прямого выхода триггера 14 и на выходе коммутатора 11 действует нулевой двоичный код. На выходе сумматора 6 в этом случае формируется двоичньй код величины

.

которьй равен удвоенному значению преобразованного числа.

Последовательньй двоичньй код преобразованного числа с выхода сумматора 6 записывается, начиная с младшего разряда, в регистр 3 сдвига под действием тактовых импульсов поступающих с выхода элемента 30 И блока 12 управления.

Спутся 2 И. + 1 такт после запуска

преобразователя цикл преобразования

заканчивается и в регистре 3 сдвига

фиксируется двоичньй код преобразо;ванного числа. Разрядность регистра

282908

3 сдвига 2п +1 выбрана так, чтобы младший разряд двоичного кода преобразованного числа (второй разряд удвоенного значения преобразованного 5 числа) в конце цикла преобразования находился в первом разряде регистра 3 сдвига.

Блок 12 управления (фиг.2) вырабатывает сигнал окончания цикла пре- 10 образования следующим образом.

После запуска преобразователя генератор 27 одиночных импульсов выра- батывает одиночньй импульс, которьй

устанавливает триггер 28 в единичное )5 состояние. Тактовые импульсы с-прямого выхода генератора 25 тактовых импульсов начинают поступать через элемент 30 И, открытый сигналом прямого выхода триггера 28, на вход де- 20 лителя 26 частоты, имеющего коэффициент деления равньй п . Спустя и тактов после запуска преобразователя на выходе делителя 26 частоты формируется импульс, которьй устанавли- 25 вает триггер 29 в единичное состояние и спустя время задержки элемента 33 задержки, равное периоду следования тактовых импульсов, поступает на вход элемента 32 И, закрытого сигна-. лом инверсного выхода триггера 29. Единичньй сигнал прямого выхода триггера 29 поступает по выходу 39 на вход сброса формирователя 8 дополнительного кода, устанавливая его в исходное состояние.

Элемент 31 И формирует из сигналов прямого выхода триггера 28 и инверсного выхода триггера 29 импульс- ньй сигнал, действующий в течение первых ц тактов работы преобразова- 0 теля на втором входе элемента 16 И и управляющем входе вычитателя 7. Сигнал логической единицы на управляющем входе вычитателя 7 обеспечивает выполнение операции вычитания, 5 которая завершается, как только на управляющем входе вычитателя 7 устанавливается сигнал логического нуля.

Спустя 2 h тактов после запуска преобразователя на выходе делителя 0 26 частоты формируется второй импульс, которьй сбрасывает триггер 29 в нулевое состояние и спустя такт через элемент 33 задержки и элемент 32 И, открытьй сигналам инверсного 5 выхода триггера 29, поступает на нулевой вход триггера 28, устанавливая его в нулевое состояние спустя такт после запуска преобразова30

теля. Триггер 28 в нулевом состоянии блокирует элемент 30 И, и выдача тактовых импульсов блоком 12 управления прекращается.

Импульс, сформированньм на выходе элемента 32 И блока 12 управления, поступает также на нулевые входы тригеров 1А и 15, устанавливая их в нулевые состояния.

Таким образом, спустя 2н+1 такт после запуска преобразователя триггеры 14;, 15 и триггеры 28, 29 блока 12 управления устанавливаются в нулевые состояния и цикл преобразования заканчивается.

Формула изобретения

Преобразователь кода системы ос- таточнык классов в позиционный код, содержащий первьм, второй и третий регистры сдвига, блок умножения, сум матор-вычитатель, сумматор, формиро- .ватель дополнительного кода, переключатель основания, переключатель диапазона, коммутатор, первый и второй триггеры, первьм, второй, третий и четвертый элементы И, первый и второй элементы задержки и блок управления, -включающий генератор тактовых импульсов, генератор одиночных импульсов, делитель частоты, первый триггер, три элемента И и элемен задержки, вход которого соединен с выходом делителя частоты, вход которого соединен с выходом первого элемента И, к первому входу которого подключен прямой выход генератора тактовых импульсов, инверсный выход которого соединен с тактовым входом генератора одиночных импульсов, вход запуска которого, являющийся входом блока управления, соединен с входом запуска устройства, выход генератора одиночных импульсов подключен к первому выходу блока управления и единичному входу первого триггера, выход которого подключен к второму входу первого элемента И, первые входы второго и третьего элементов И объединены, первый выход блока управления подключен к первым входам первого и второго элементов И устройства и управляющим входам регистров сдвига, второй выход блока управлени соединен с тактовыми входами первого и второго регистров сдвига, информационные входы которых являются пер

0

5

5

5

0

5

0

S

0

выми и вторыгчи входами устройства, информационные входы третьего регистра сдвига соединены с соответствую- вдими выходами переключателя диапазона, выходы переключателя основания подключены к первым входам блока умножения, второй вход которого соединен с выходом третьего элемента И устройства,первьй вход которого подключен к выходу формирователя дополнительного кода, выход блока умножения соединен с первым входом сумма- тора-вычитателя, второй вход которого подключен к выходу первого элемента задержки, а выход сумматора-вычи- тателя соединен с первым входом сумматора, второй вход которого подключен к выходу коммутатора, а выход - к входу последовательной записи третьего регистра сдвига, выход которого соединен с первым входом коммутатора и первым входом четвертого элемента И, выход которого через второй элемент задержки подключен к второму входу коммутатора, управляющий вход которого соединен с прямым вькодом второго триггера, прямой выход первого триггера подключен к первому управляющему входу сумматора- вычитателя, нулевые входы триггеров объединены, а единичные входы подключены к выходам соответствующих элементов И, отличающийся тем, что, с целью повышения быстродействия, в него введены блок сравнения кодов, вычитатель и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, а в блок управления введен второй триггер, счетньй вход которого соединен с выходом делителя частоты, инверсный выход подключен к первому входу второго элемента И, второй вход которого соединен с выходом элемента задержки, выход второго элемента И подключен к нулевому входу первого триггера, выход которого соединен с вторым входом третьего элемента И, выходы первого, третьего и второго элементов И и прямой выход второго триггера являются соответственно вторым, третьим, четвертым и пятым выходами блока управления и подключены соответственно к тактовому входу третьего регистра сдвига, к второму входу третьего элемента И устройства и управляющему входу вычитателя, к нулевым входам триггеров и к входу сброса формирователя дополнительного кода, управляющий вход которого объе11

динен с вторым управляющим входом сумматора-вычитателя и подключен к инверсному выходу первого триггера, прямой выход которого соединен с вторым входом четвертого элемента И, выход формирователя дополнительного подключен к выходу вычитателя, первый вход которого объединен с входом первого элемента задержки и подключен к выходу второго регистра сдвига, второй ВХОД вычитателя

23

2829012

соединен с выходом первого регистра сдвига, второй вход первого элемента И подключен к выходу блока сравнения кодов, первые и вторые входы кото- 5 рого объединены с информационными входами соответствующих регистров сдвига, входы первых разрядов которых объединены с входами элемента ИСКПЮ- ЧАЩЕЕ ИЛИ, выход которого подключен 10 к второму входу второго элемента И.

Фаг./

2«

фиг, Z

Редактор Н. Киштулинец

Составитель О. Ревинский

Техред Н.Бонкало Корректор М. Самборская

Заказ 2298/59Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в позиционный код | 1988 |

|

SU1624699A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Квадратор | 1987 |

|

SU1501049A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых преобразователях вычислительных систем. Цель изобретения - повьпиение быстродействия. Преобразователь содержи три регистра сдвига, блок умножения, сумматор- вычитатель, сумматор, формирователь дополнительного кода, переключатель основания, переключатель диапазона, коммутатор, два триггера, четыре элемента И, два элемента задержки и блок управления, включакнций в себя генератор тактовых импульсЬв, генератор одиночных импульсов, делитель частоты, первый триггер, три элемента И и элемент задержки. Благодаря введению блока сравнения кодов, вычита- теля и элемента ИСКПЮЧАЩЕЕ ШШ, а также второго триггера в блок управления один цикл преобразования длится 2 п +1 тактов, где h- количество разрядов представления остатков а. и 3 по основаниям Р, остаточных классов. и Р системы 2 ил. i (Л С 00 1C

| Преобразователь кода из системы остаточных классов в позиционный код | 1980 |

|

SU924695A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-04-30—Публикация

1984-09-15—Подача