1

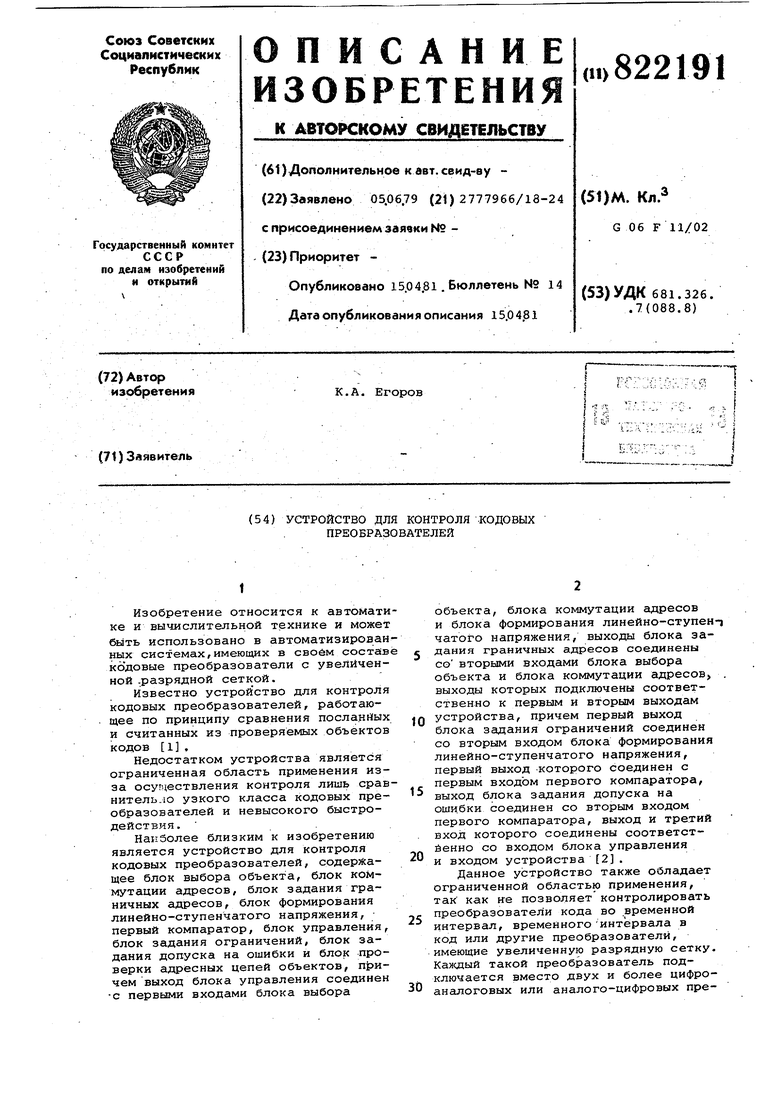

Изобретение относится к автоматике и вычислительной технике и может быть использовано в автоматизированных системах,имеющих в своём состав кбдовые преобразователи с увеличенной .разрядной .

Известно устройство для контроля кодовых преобразователей, работающее по принципу сравнения посланных и считанных из проверяемых объектов кодов 1.

Недостатком устройства является ограниченная область применения изза осуществления контроля лишь сравнитель.ю узкого класса кодовых преобразователей и невысокого быстродействия.

Наиболее близким к изобретению является устройство для контроля кодовых преобразователей, содержащее блок выбора объекта, блок коммутации адресов, блок задания граничных адресов, блок формирования линейно-ступенчатого напряжения, первый компаратор, блок управления, блок задания ограничений, блок задания допуска на ошибки и блок проверки адресных цепей объектов, пркчем выход блока управления соединен с первыми входами блока выбора

объекта, блока коммутации адресов и блока формирования линейно-ступен-j чатого напряжения, выходы блока задания граничных адресов соединены со вторыми входами блока выбора объекта и блока коммутации адресов, . выходы которых подключены соответственно к первым и вторым выходам устройства, причем первый выход

0 блока задания ограничений соединен со вторым входом блока формирования линейно-ступенчатого напряжения, первый выход -которого соединен с первым входом первого компаратора,

5 выход блока задания допуска на ошибки соединен со вторым входом первого компаратора, выход и третий вход которого соединены соответственно со входом блока управления

0 и входом устройства 2 .

Данное устройство также обладает ограниченной областью применения, так как не позволяет контролировать

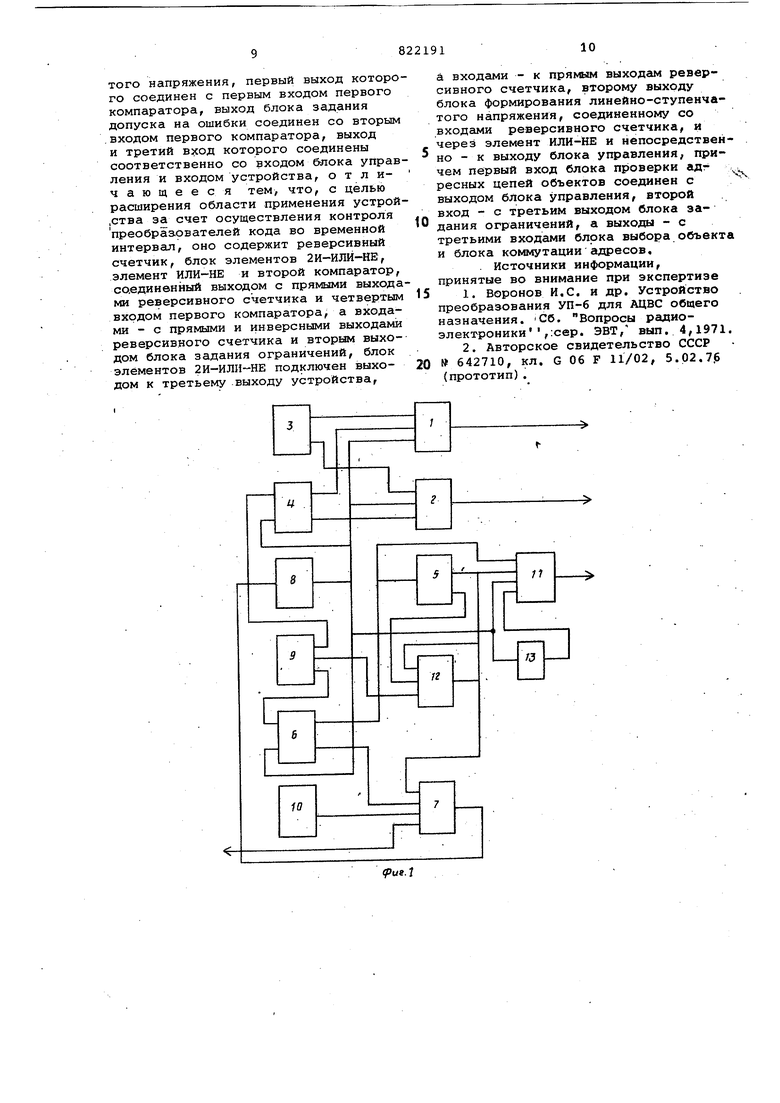

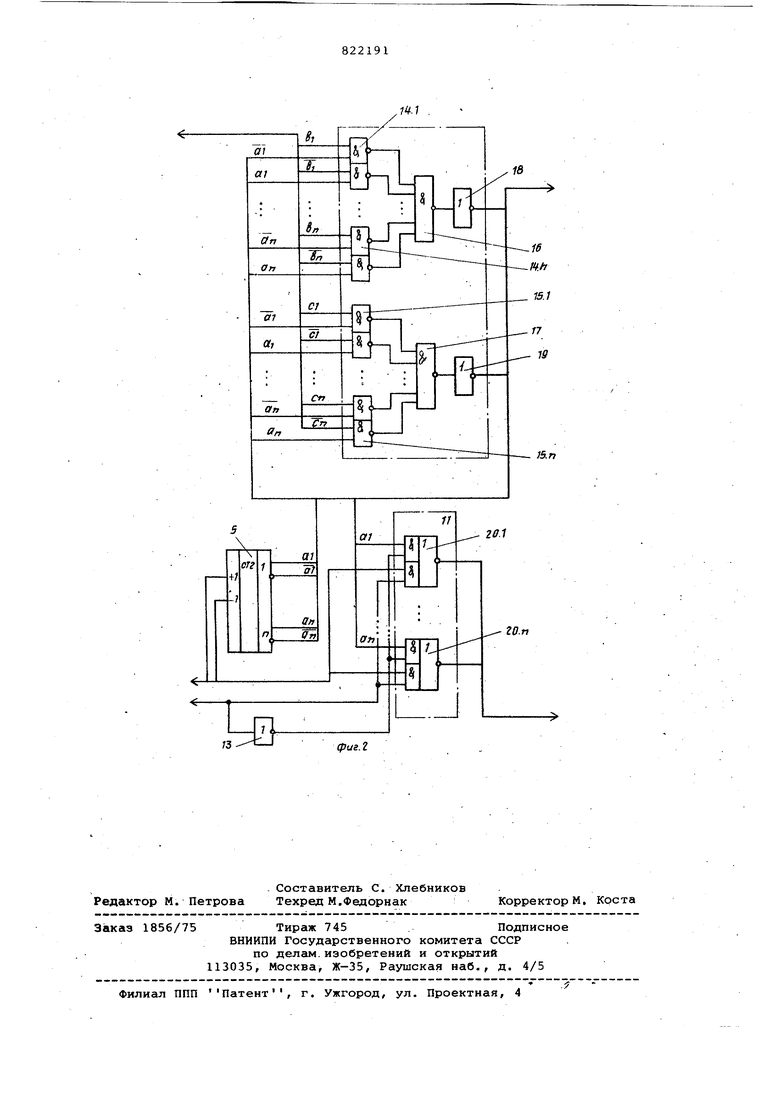

с преобразователи кода во временной интервал, временногоинтервала в код или другие преобразователи, имеющие увеличенную разрядную сетку. Каждый такой преобразователь подключается вместо двух и более цифро0 аналоговых или аналого-цифровых преобраэователей и требует формирования сигналов, соответствующих линейно в6,эрастающёму и линейно убывающему напряжениям увеличенного масштаба при условии обращения к нескольким раэным каналам,что нельзя осуществить в данном устройстве. Устройство также имеет специальный существенно отли.чный от , рабочего, режим контроля адресных цепей объектов, который основан .на выдаче прямого или обратного кода в зависимости от адреса канала и порядкового -номера обращения, В этом режиме часто, возникают ситуации посылки в проверяемый канал , при двух последова- тель«ых обращениях сначала , а потом, обратного кодов или наоборот что может привести к большому скачку напряжения на выходе цифроаналогового преобразователя и к перевозбуждению выходного усилителя на значитель но большее время, чем в рабочем режи ме. Кроме того, длительность отработки перепада напряжения, поступающего с выхода цифроансшогового на ,вход ана1лого-цифрового преобразователя следящего типа, пропорциональн величине скачка. Все это приводит к необходимости контроля адресных- . цепей объектов либо в меньшем диапазоне частот, чем при обычном рабо.чем режиме, либр на небольшом.участ ке шкалы преобразователей, что не, всегда приводит к выявлению неисправностей. Осуществление такого способа проверки адресных цепей требует значительного дополни те-льного оборудования. Цель изобретения - расширение области- применения устройства за счет осуществления контроля преобра зователей кода во временной интервгш, повьлиениедостоверности и упро щение контроля адресных.цепей объек тов. . . ; Данная цель достигается тем, что в устройство, содержащее блок выбо раОбъекта, блок коммутации адресов блок эгщаиия граничных адресов,, блок формирования линейно-ступенчат го напряжения, первый компаратор, . блок управления, блок задания ограничений, блок задания допуска на ошибки и блок проверки адресных цепей объектов, причем выход блока управления соединен с первыми входа ми блока выбора объекта, блока коммутации адресов и блока формировани линейно-ступенчатого напряжения, выходы блока задания граничных ад. ресов соединены .со вторыми входами Олока выбора объекта и блока коммут ции гшресов, выходы которых подключены соответственно к первым и вторым выходам устройства, причем перв выход блока задания ограничений соединен со вторым входом блока формирования линейно-ступенчатого напряжения, первый выход которого, соединен с первым входом первого компаратора, выход блока задания допуска на ошибки соединен со вторым входом первого компаратора, выход и ретий вход которого соединены соответственно со входом блока управления и входом устройства, в-вёдены реверсивный счетчик, блок элементов 2И-ИЛИ-НЕ, элемент ИЛИ-НЕ и второй компаратор,соединенный выходом с прямыми выходами реверсивдого снетчика и .четвертым входом первого компарато-. ра. а входами - с прямыми и инверсными выходами реверсивного счетчика -И вторым выходом блока задания ограничений, блок элементов- 2И-ИЛИ-НЕ подключен выходом к третьему выходу устройства, а уходами - к .прямым выходам реверсивного счетчика, второму выходу блока формирования . линейно-ступенчатого напряжения, соединенному со, в.х-одами реверсивного счетчика, и через;,элемент ИЛИ-НЕ и непосредственно - к выходу блока управления, причем первый вход блока проверки адресных цепей объектов соединён с выходом блока управления, второй вход - с третьим выходом блока задания ограничений, а выходы - с третьими входами блока выбора объекта и блока коммута- . ции адресов. На фиг. 1 приведена блок-схема .устройства для контроля кодовых преобразователей; на фиг. 2 - пример схемного раскрытия узлов устройства, осуществляющих контроль преобразователей кода во временной интервал и временного интервала в код, имеющих разрядную сетку двой.ного масштаба. . . Устройство для контроля кодовых преобразователей содержит блок 1 выбора .объекта, блок 2 коммутации адресов, блок 3 задания граничных адресов, блок 4 проверки адресных . цепей объектов, реверсивный счётчик 5, блок 6 формирования линейнб-сту-, пенчатого напряжения, первый компаратор 7, блок 8. управления, блок 9 задания ограничений, блок 10 задат ния допуска на ошибки блок 11 элементов 2И-ИЛИ.-НЕ, второй компаратор 12, элемент 1.3 ИЛИ-НЕ. Компаратор 12 состоит из элементов 14.114.П, каждый из которых представляет собой сдвоенный логический элеMgar 2И-НЕ. реализующий функции и (i 1, п); элементов 2 И -.НЕ 15.1 -15. п, каждый кот орых реализует функции и (1 1,п); элементов 16 и 17, на которых осуществляется конъюнкция и- инверсия выходных сигналов соответственно с элементов 14,1-14.п и 15.115,п; логических элементов ИЛИНЕ 18 и 19, на которых реализуется инверсия сигналов с выходом элемен тов 16 и 17. Выходы элементов -18 и соединяются со входом первого комп ратора. Блок 11 состоит из элементов 20 20.п, выполняющих логическую функци 2И-ИЛИ-НЕ. К верхним совпаде ния элементов 20;1-20.п подсоединяются прямые выходы счетчика 5, а к нижним - выходы блока 6.Вторые вхо .верхних и. нижних схем совпадения элементов 20.1-20. п соединяются .с блоком 8 непосредственно и. через эл мент. 13 ИЛИ-НЕ. Выходы элементов . 20.1-20.п являются выходами устрой .ства. ... функциональные назначения назва ных блоков следующие. В-блоке 1 происходит дешифрация и формирование сигналов обращения к контролируеьфлм объектам, а выход блока 1 являет ся первым выходом устройства и соединен со всеми объ тами. В блоке 2 формируются сигналы выбора адреса канала в объекте, а выход блока 2 - это второй выход устройства1 и соединен с адресньми шинами всех объектов. Граничные адреса проверяемых каналов задаютс блоком 3, выходы которого соединены с блоками 1 и 2. Контроль адресов преобразователей производится блоком 4, выходы которого соединены с блоками 1 и 2. Реверсивный счетчик 5 своими прямыми .выходами связа со входами блока 11, первого и втор го компаратора, а HHBe iCHUMH выходами - со входом второго компаратора. В блоке 6 происходит формирование кодов, соответствующих линейно-ст-упенчатому напряжению, причем один из выходов блока :6. сдединен do входами реверсивного счетчик .и блок.а 11, а другой - со входом первого компаратора, в котором про изводится сравнение с зал анной точностью посланных и из объектов кодов. Выход первого компа ратора соединен со. входо.м блока 8, а один из входов является входом устройства. Блок 8 управления организует работу всего устройства и; связан по выходу с блоками 1, 2, 4, 6 и 11 и элементом 13 ИЛИ-НЕ, выход которого соединен с одним из входов блока 11. В блоке 9 определяются пределы формирования линейно-ступенчатого напряжения, причем выходы блока 9 соединены с блоками 4 и 6 и вторым компаратором. Точность сравнения посланных и принятых из объектов.кодов задается блоком 10, выход которого соединен с одним из входов первого компаратора. Блок 11, ВЫПОЛНЯЮ1ЦКЙ логи ческие функции 2И-ЙЛИ-НЕ, соединен выходг1ми с .выходами устройства, которые подключаются к информационным входам всех объектов. Второйкомпаратор реализует функцию сравнения кода в счетчике 5 с предельными ;значениями, заданными в блоке 9 и связан выходрм со входом первого крмларатора. Реверсивный счетчик. 5 связан шинами сложения (фиг, 2) И вычитания со старшим разрядом счетчика формирования кодов в блоке 6, что дает возможность получить линейно изменяющиеся коды увеличенного масштаба. Разрядность -счетчика 5 равна стандартной разрядной сетке в системе преобразующих устройств.п. Прямые выходы счетчика, обозначены идентификаторами а,,а2/ г а и их инверсии К компаратору 12 подключаются из блока 9 предельные знг1чения: .макг симальное значение кода ,t..Ьп и его инверсия Ъ jbj ,,. ,Ъп и мини,6„и мальное значение ,с I, ,... инверсия 5, С f . . с г,, а также чика 5 прякие и инверсные выходы. Работа устройства при контроле аналого-цифровых и цифроаналог-овых преобразователей происходит следующим образом. По сигналу из блока 8 начальный адрес и «омёр объекта из блока 4 направляются в блоки 1 и 2, где дешифруются и передаются в объект. Сигналом из блока управления кодд.сформированныйв блоке б, передается в блок 11 И далее в выбранный канал объекта.. Блок управления модифицирует адрес в блоке-4 и направляет код б51ока 6 по новому адресу в объекте. Данная процедура повторяется до совпадения текущед о гщреса с конечным, заданным в блоке 3. После осуществления цифроаналогового преобразова:ния во. всех контролируемых каналах. устройство повторно, в той же последовательности, перебирает все адреса каналов в объектах. При этом после .каждого обращения к выбранному каналу в компараторе 7 происходит сравнение кода, поступившего с объекта, с кодом в блоке 6. Если разница между кодами превышает допуск, заданный в блоке 10, то работа устройства прерывается. Индикация основных регистров дает возможность обнаружить номер текущего кангша и характер неисправности в объекте. . после обращения ко всем ангшогрифровым каналам устройство осуществяет переход к следующему коду, на котором производится проверка, т.е. одифицирует код в блоке б. Диапазон изменения кодрв в блоке 6, соответствующих линейно-ступ енчатому наряжению, задается блоком 9. Работа устройства при проверке реобразователей кода во временной нтервал и временного интервала в од происходит следующим образом.

Выбор и передача адреса начального канала осуществляется аналогично общему режиму проверки. По сигналу -логической блока 8, посланному на вход элемента 13, код,сформированный в блоке .6, через элементы 2И-ИЛИ-НЕ блока 11 поступает в первый канал выбранного преобразователя.

После модификации адресов, которая также производится аналогично общему режиму контроля, блок 8 меняет сигнал на входе элемента 13 ka

О

При этом

уровень логического

на выходные шины блок.а 11, а значит и во второй канал выбранного преобразователя, поступит код со счетчика 5.

Далее устройство перебирает все номера преобразователей, заданных в блоке 3 таким образом, что в первые каналы этих преобразователей поступает информация из блока 6, а во вторые каналы из блока 5. Это достигается последовательной сменой уровней управления на входе элемента 13.

После Осуществления двойного преобразования кода во временной интервал и временного интервала в код устройство повторно, в той же последовательности, перебирает адреса все контролируемых преобразователей. Информация из объектов с ошибкой преобразования поступает на вход компаратора 7. Код, поступающий из первых каналов выбранных преобразователей, сравнивается с кодом, сформированным в блоке 6, код из вторых каналов - q кодом в счетчике 5. Если результат сравнения кодов превосходит допустимую ошибку, заданную в блоке 10, то блок 8 вырабатывает сигнал прерывания.

После проверки всех преобразователей на данном коде блок 8 уве + 1

личивает, при сигнале на шине

или уменьшает, при сигнале на шине , формируемые в блоке 6 и счетчике 5 и производит описанный контроль уже на новом коде.

Смена режимов сложения и вычитания в счетчике 5 и блоке 6 происходит автоматически следующим образом.

При равенстве кодов в счетчике 5 (сигнал на выходе элемента 18) и счетчике формирования кодов в блоке б максимальному коду, заданному в блоке 9, блок 8 разрешает прохождение с 1гнала реверсивного сложения на шины -1 блока 6 и счетчика 5, а при равенстве кодов в счетчике 5 (сигнал на выходе элемента 19) и счетчике формирования кодов в блоке 6 минимальному коду блока 9 блок 8 переключает сигнал реверсивного слосчетчика 5 и

+ 1

жения на шины блока 6.

Таким образом, устройство осуществляет полную функциональную проверку преобразователей кода во временной интервал и временного интервала в код, каждый из которых требует обращения к двум стандартным каналам, как при возрастании, так и при уменьшении кодов по закону линейно-ступенчатого напряжения двойного масштаба.

Контроль адресных цепей объектов в устройстве производится на основе двойной модификации адресов за счет включения блока 4. Устройство изменяет адреса в блоке 4 таким образом, что в каждый текущий цикл проверки линейно изменяющиеся коды выдаются только по одному адресу в объекте, а информация в других каналах данног объекта остается зафиксированной. Так, в первом цикле коды поступают в первый канал объекта, во втором цикле - во второй, в третьем - в третий и т.д. При неисправности адресных цепей посланный и считанные из объекта коды различны, и устройство останавливается по несразэнению кодов в компараторе 7. Номера неисправных каналов фиксируются системой индикации устройства.

Возможность проверки преобразователей кода во временной интервал и временного интервала в код, кроме обычных цифроаналоговых и аналогоцифровых преобразователей, расширяет область применения устройства и позволяет применять его в современных автоматизированных системах, полностью освобождая при этом от функци контроля, наладки и ремонта преобразователей универсальные электронные вычислительные машины.

Формула изобретения

Устройство для контроля кодовых преобразователей, содержащее блок выбора объекта, блок коммутации ад-, ресов, блок задания граничных адресов, блок формирования линейно-ступенчатого напряжения, первый компа.ратор, блок управления, блок задания ограничений, блок задания допуска на ошибки и блок проверки адресных цепей объектов, причем выход ;блока управления соединен с первыми входами блока вь1бора о&ьек-га, блока коммутации гщресов и блока формирования линейно-ступенчатого напряжения, выходы блока задания граничных адресов соединены со вторыми входами блока выбора объекта и блока коммутации адресов, выходы которых подключены соответственно к первым и вторым выходам устройства, причем первый выход блока задания ограничений соединен со вторым входом блока формирования линейно-ступенчатого напряжения, первый выход которого соединен с первым входом первого компаратора, выход блока задания допуска на ошибки соединен со вторым .входом первого компаратора, выход и третий вход которого соединены соответственно со входом блока управления и входом устройства, отличающееся тем, что, с целью расширения области применения устрой,ства за счет осуществления контроля преобразователей кода во временной интервал, оно содержит реверсивный счетчик, блок элементов 2И-ИЛЙ-НЕ, элемент ИЛИ-НЕ и второй компаратор, со.единенный выходом с прямыми выходами реверсивного счетчика и четвертым входом первого компаратора, а входами - с прямыми и инверсными выходами реверсивного счетчика и вторым выходом блока задания ограничений, блок элементов 2И-ИЛН НЕ подключен выходом к третьему .выходу устройства.

а входами - к прямым выходам реверсивного счетчика, второму выходу блока формирования линейно-ступенчатого напряжения, соединенному со входами реверсивного счетчика, и через элемент ИЛИ-НЕ и непосредственно - к выходу блока управления, причем первый вход блока проверки адг

чЧ ресных цепей объектов соединен с выходом блока управления, второй вход - с третьим выходом блока за0дания ограничений, а выходы - с третьими входами блока выбора объекта и блока коммутации адресов.

. Источники информации, принятые во внимание при экспертизе

5

1.воронов И.С. и др. Устройство преобразования УП-б для АЦВС общего назначения. Сб. Вопросы радиоэлектроники ,:сер. ЭВТ, вып. 4,1971.

2.Авторское свидетельство СССР

642710, кл. G 06 F 11/02, 5.02.7,6

0 (прототип).

фаг. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля систем преобразователей информации | 1980 |

|

SU978152A1 |

| Устройство для профилактического контроля блоков цифро-аналогового преобразования | 1976 |

|

SU642710A1 |

| КОММУТАТОР ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1995 |

|

RU2103716C1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Стабилизатор-регулятор переменного напряжения | 1987 |

|

SU1501009A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Стенд для испытания энергоустановок электромобилей | 1985 |

|

SU1255890A1 |

| Устройство для адресной передачи сигналов тревоги в системе пожарной сигнализации | 1991 |

|

SU1836707A3 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Устройство для контроля состояния информационно-измерительной системы | 1986 |

|

SU1314342A1 |

Авторы

Даты

1981-04-15—Публикация

1979-06-05—Подача