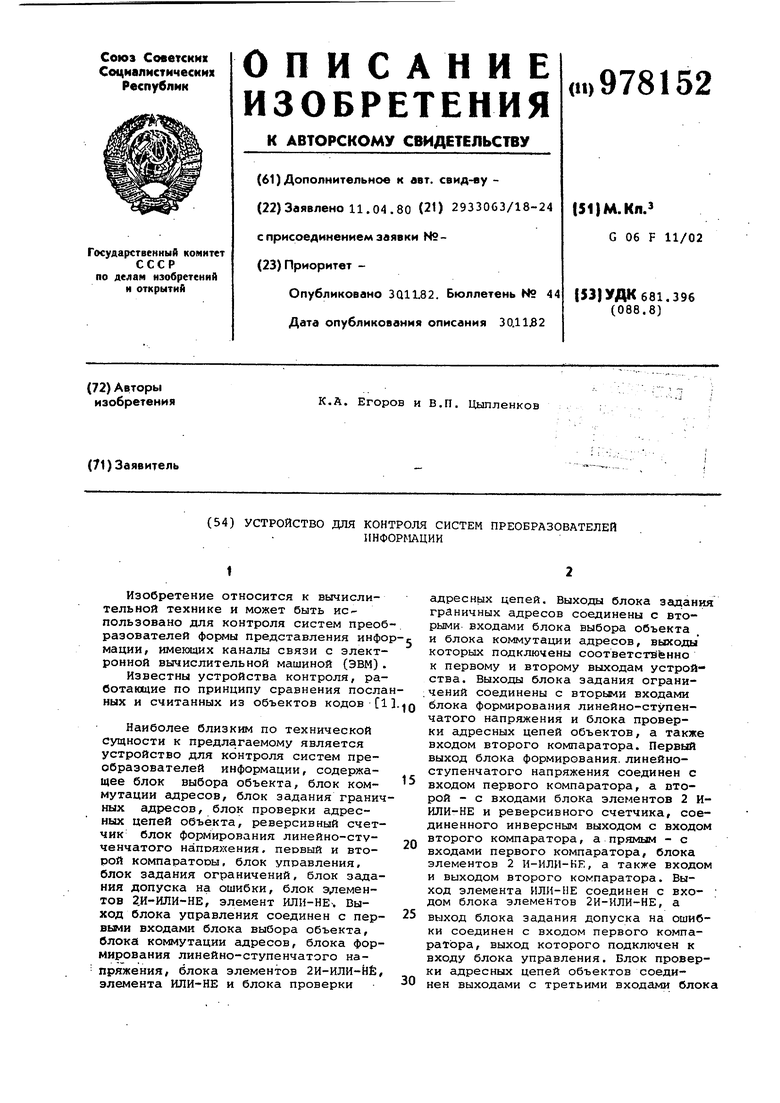

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СИСТЕМ ПРЕОБРАЗОВАТЕЛЕЙ Изобретение относится к вычислительной технике и может быть использовано для контроля систем преоб разователей фоЕмиы представления инфо мации, имеющих каналы связи с электронной вычислительной машиной (ЭВМ). Известны устройства контроля, работающие по принципу сравнения посла ных и считанных из объектов кодов 1 Наиболее близким по технической сущности к предлагаемому является устройство для контроля систем преобразователей информации, содержащее блок выбора объекта, блок коммутации адресов, блок задания гранич ных адресов, блок проверки адресных цепей объекта, реверсивный счетчик блок формирования линейно-стученчатого напряжения, первый и второй компараторы, блок управления, блок задания ограничений, блок задания допуска на ошибки, блок э/гементов 2.И-ИЛИ-НЕ, элемент Ш1Н-НЕ-. Выход блока управления соединен с первыми входами блока выбора объекта, блока коммутации адресов, блока формирования линейно-ступенчатого напряжения/ блока элементов 2И-ИЛИ-НЁ, элемента ИЛИ-НЕ и блока проверки

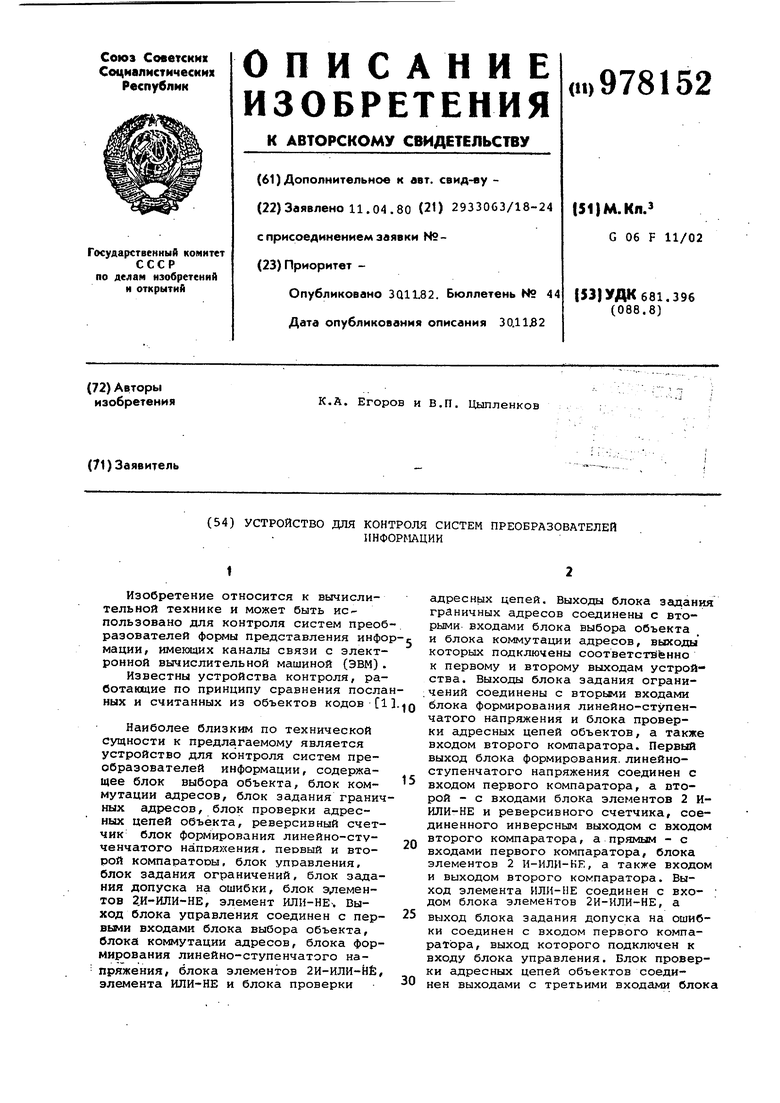

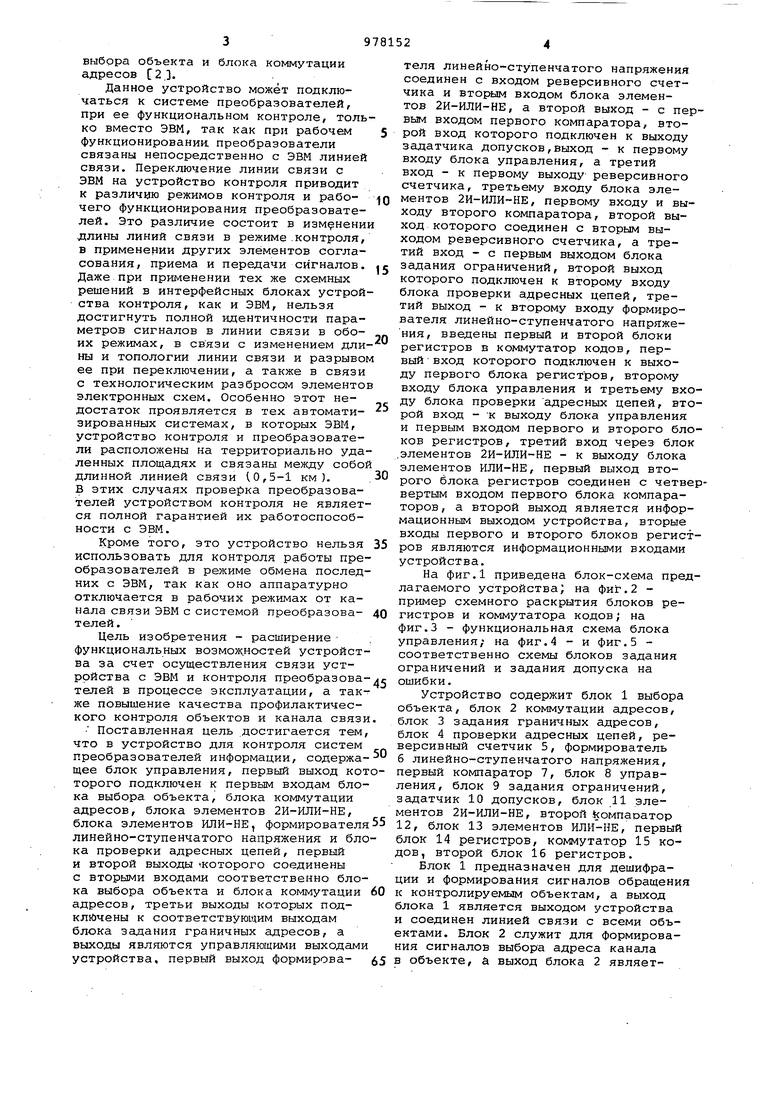

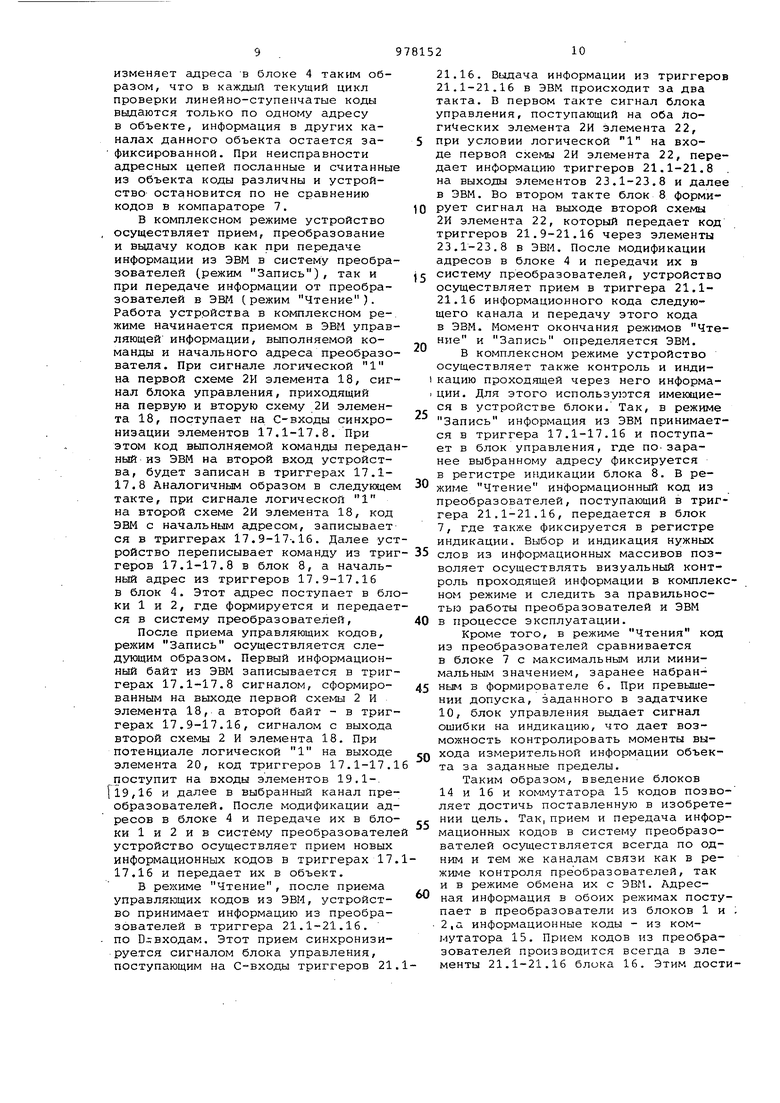

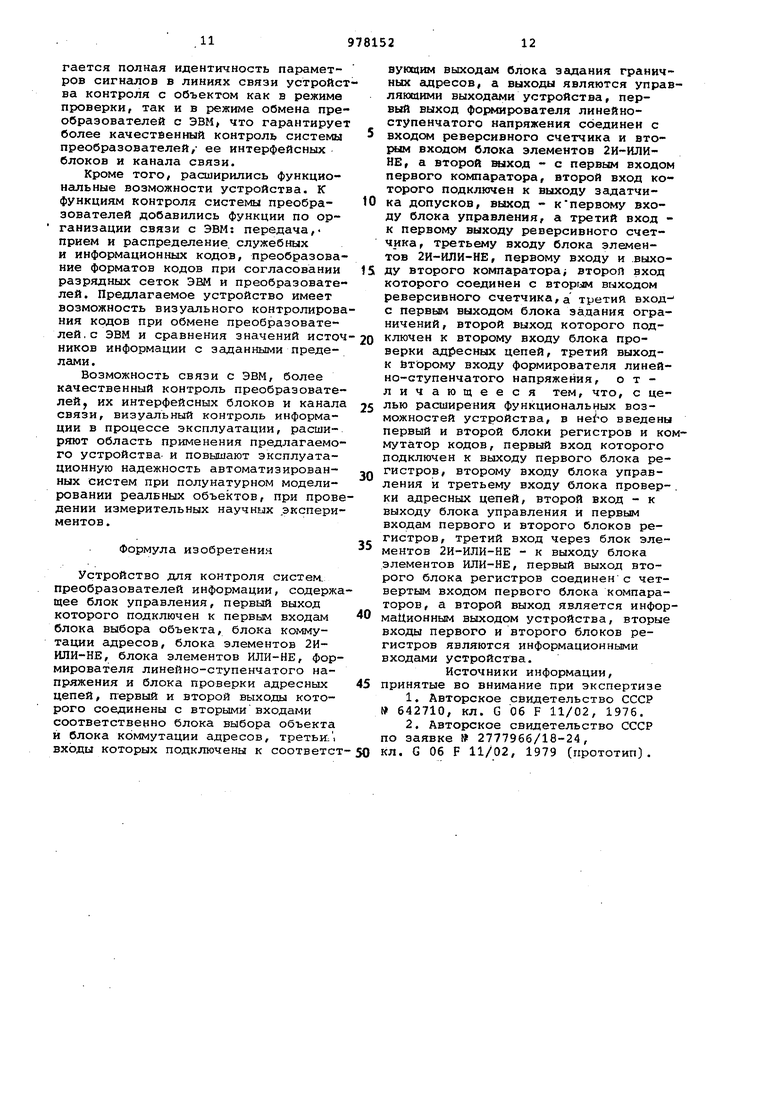

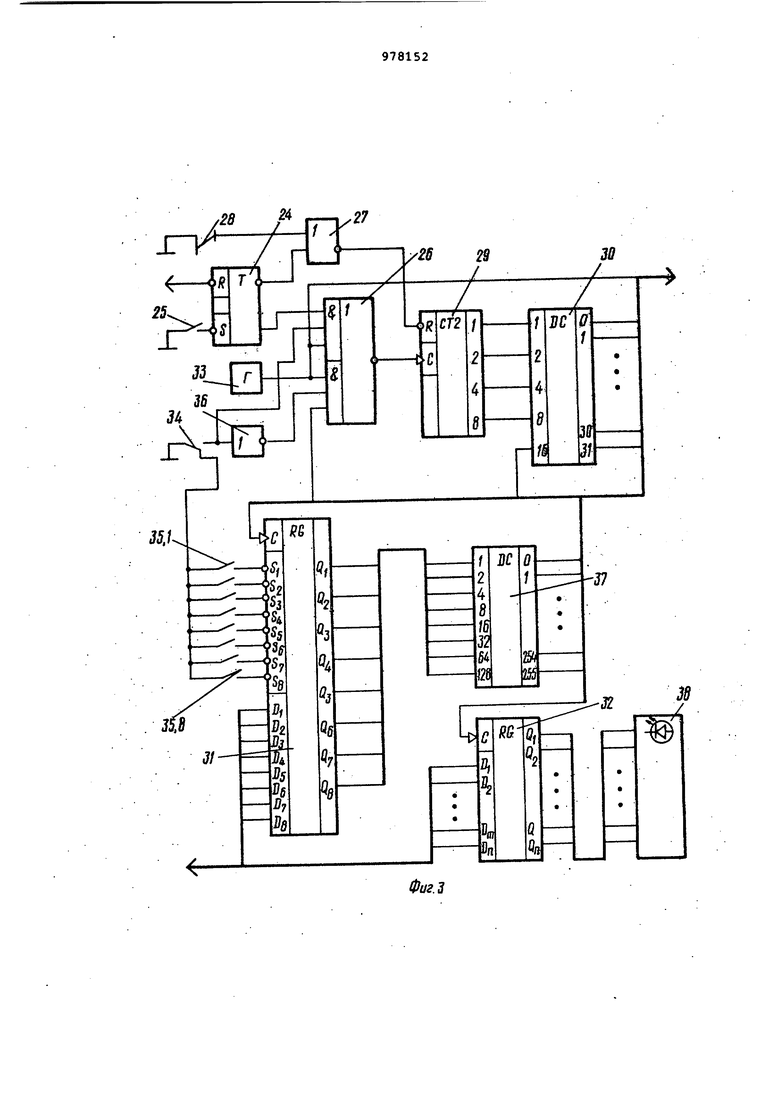

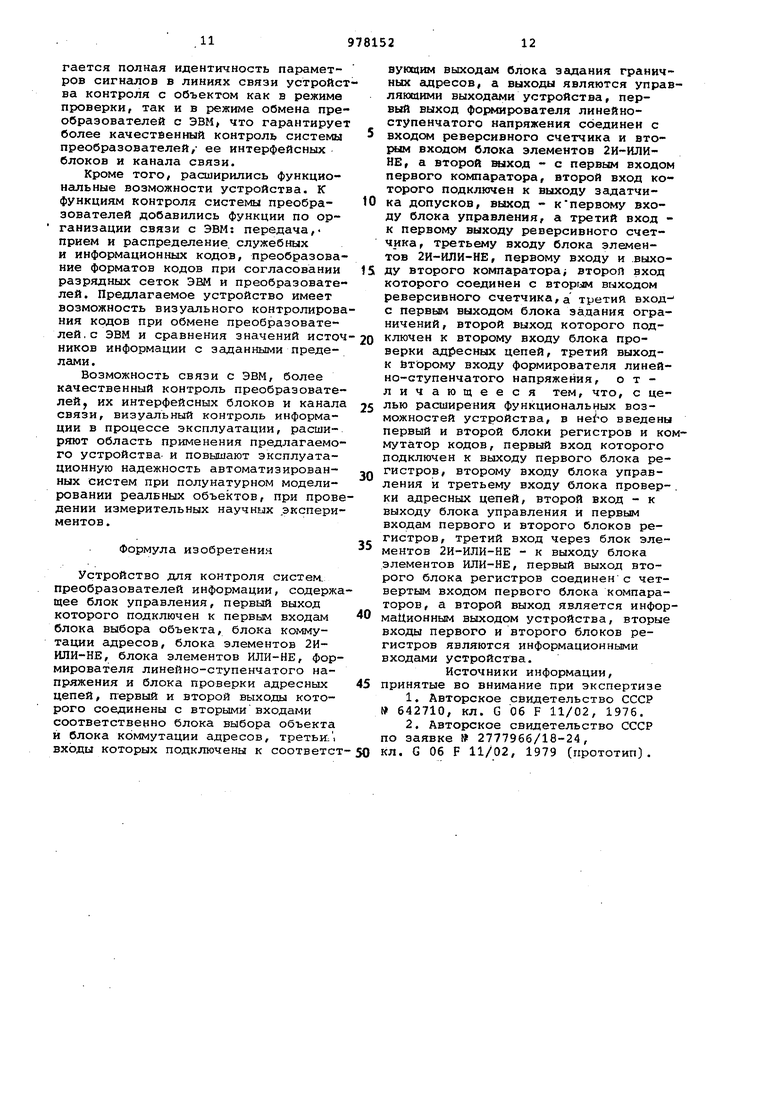

ИНФОРМАЦИИ адресных цепей. Выходы блока задания граничных адресов соединены с вторыми входами блока выбора объекта и блока коммутации адресов, выходы которых подключены соответственно к первому и второму выходам устройства. Выходы блока задания ограничений соединены с вторыми входами блока формирования линейно-ступенчатого напряжения и блока проверки адресных цепей объектов, а также входом второго компаратора. Первый выход блока формирования, линейноступенчатого напряжения соединен с входом первого компаратора, а второй - с входами блока элементов 2 ИИЛИ-НЕ и реверсивного счетчика, соединенного инверсным выходом с входом второго компаратора, а прямым - с входами первого компаратора, блока элементов 2 Н-ИЛИ-КЕ, а также входом и выходом второго компаратора. Выход элемента ИЛН-ПЕ соединен с вхо- ; дом блока элементов 2И-ИЛИ-НЕ, а выход блока задания допуска на ошибки соединен с входом первого компаратора, выход которого подключен к входу блока управления. Блок проверки адресных цепей объектов соединен выходами с третьими входами блока выбора объекта и блока коммутации адресов С2.. Данное устройство может подключаться к системе преобразователей, при ее функциональном контроле, толь ко вместо ЭВМ, так как при рабочем функционировании преобразователи связаны непосредственно с ЭВМ линией связи. Переключение линии связи с ЭВМ на устройство контроля приводит к различию режимов контроля и рабочего функционирования преобразователей. Это различие состоит в изменении длины линий связи в режиме .контроля, в применении других элементов согласования, приема и передачи сигналов. Даже при применении тех же схемных решений в интерфейсных блоках устройства контроля, как и ЭВМ, нельзя достигнуть полной идентичности параметров сигналов в линии связи в обоих режимах, в связи с изменением длины и топологии линии связи и разрывом ее при переключении, а также в связи с технологическим разбросом элементо электронных схем. Особенно этот недостаток проявляется в тех автомати зированных системах, в которых ЭВМ, устройство контроля и преобразователи расположены на территориально уда ленных площадях и связаны между собой длинной линией связи 0,5-1 км). В этих случаях проверка преобразователей устройством контроля не является полной гарантией их работоспособности с ЭВМ. Кроме того, это устройство нельзя использовать для контроля работы преобразователей в режиме обмена последних с ЭВМ, так как оно аппаратурно отключается в рабочих режимах от канала связи ЭВМ с системой преобразователей. Цель изобретения - расширение функциональных возможностей устройст ва за счет осуществления связи устройства с ЭВМ и контроля преобразователей в процессе эксплуатации, а также повышение качества профилактического контроля объектов и канала связи Поставленная цель достигается тем что в устройство для контроля систем преобразователей информации, содержа щее блок управления, первьдй выход кот торого подключен к первым входам блока выбора объекта, блока коммутации адресов, блока элементов 2И-ИЛИ-НЕ, блока элементов ИЛИ-НЕ, формирователя линейно-ступенчатого напряжения и бло ка проверки адресных цепей, первый и второй выходы (Которого соединены с вторыми входами соответственно блока выбора объекта и блока коммутации адресов, третьи выходы которых подключены к соответствующим выходам блока задания граничных адресов, а выходы являются управляющими выходами устройства, первый выход формирователя линейно-ступенчатого напряжения соединен с входом реверсивного счетчика и вторым входом блока элементов 2И-ИЛИ-НЕ, а второй выход - с первым входом первого компаратора, второй вход которого подключен к выходу задатчика допусков,выход - к первому входу блока управления, а третий вход - к первому выходу реверсивного счетчика, третьему входу блока элементов 2И-ИЛИ НЕ, первому входу и выходу второго компаратора, второй выход которого соединен с вторым выходом реверсивного счетчика, а третий вход - с первым выходом блока задания ограничений, второй выход которого подключен к второму входу блока проверки адресных цепей, третий выход - к второму входу формирователя линейно-ступенчатого напряжения, введены первый и второй блоки регистров в коммутатор кодов, первый вход которого подключен к выходу первого блока регистров, второму входу блока управления и третьему входу блока проверки адресных цепей, второй вход - К выходу блока управления и первым входом первого и второго блоков регистров, третий вход через блок .элементов 2И-ИЛИ-НЕ - к выходу блока элементов ИЛИ-НЕ, первый выход второго блока регистров соединен с четвервертым входом первого блока компараторов , а второй выход является информационным выходом устройства, вторые входы первого и второго блоков регистров являются информационными входами устройства. На фиг.1 приведена блок-схема предлагаемого устройства; на фиг.2 пример схемного раскрытия блоков регистров и коммутатора кодов; на фиг.З - функциональная схема блока управления; на фиг.4 - и фиг.З соответственно схемы блоков задания ограничений и задания допуска на ошибки. Устройство содержит блок 1 выбора объекта, блок 2 коммутации адресов, блок 3 задания граничных адресов, блок 4 проверки адресных цепей, реверсивный счетчик 5, формирователь 6 линейно-ступенчатого напряжения, первый компаратор 7, блок 8 управления, блок 9 задания ограничений, задатчик 10 допусков, блок .11 элементов 2И-ИЛИ-НЕ, второй Компаратор 12, блок 13 элементов ИЛИ-НЕ, первый блок 14 регистров, коммутатор 15 кодов, второй блок 16 регистров. Блок 1 предназначен для дешифрации и формирования сигналов обращения к контролируемым объектам, а выход блока 1 является выходом устройства и соединен линией связи с всеми объектами. Блок 2 служит для формирования сигналов выбора адреса канала в объекте, а выход блока 2 является вторым выходом устройства и соединен линией связи с адресными шинами всех объектов. Граничные адреса проверяемых каналов задаются блоком 3, выходы которого соединены с блоками 1 и 2. Контроль адресов преобразователей производится блоком 4, выходы которого соединены с блоками 1 и 2. Реверсивный счетчик 5 своими прямыми выходами связан с блоком 11, первым и вторь 4 компаратором, инверсными выходами - с входом второго компаратора. Формирователь б предназначен для формирования кодов, соответствующих линейноступенчатому напряжению, причем один из его выходов соединен с входами реверсивного счетчика и блока 11, а другой - с входом первого компаратора, в котором производится сравнение с заданной точностью посланных и принятых из объектов кодов Компаратор 7 соединен выходом с входом блока 8. Блок 8 управления служит для организации работы всего устройства .и связан по выходу с блоками 1,2,4,6,11,14-16 и элементом 13 выход которого соединен с одним из входов блока 11. блок 9 предназначен для задания пределов формировани линейно-ступенчатого напряжения, при чем выходы блока 9 соединены с блока ми 4 и 6 и вторым компаратором. Точность сравнения посланных и принятых из объектов кодов задается задатчиком 10, выход которого соединен с од ним из входов первого компаратора. Блок 11, выполняющий логические функ ции 2И-ИЛИ-НЕ, соединен выходом с входом коммутатора 15 кодов, который подключен выходом к третьему выходу устройства, связанному линией связи с информационными входами системы преобразователей. Блок 14 предназна чен для приема, преобразования и хранения информации, одним из входо соединен с вторым входом устройства подключенному к выходу ЭВМ. Выход блока 14 соединен с входами блоков 4,8 и 15. Второй компаратор 12 реал зует функцию сравнения кода в счетч ке 5 с предельными значениями, заданными в блоке 9 и связан выходом с входом первого компаратора. Блок 16, предназначенный для приема и преобразования кодов объекта в код ЭВМ, связан с одним из входов с пер вым входом устройства, а выходами с входом первого компаратора и четв тым выходом устройства, подключенHbBvi к информационным входам ЭВМ. На фиг.2 приведен пример схемного раск тия блока 14 для приема и преобразо вания 8-разрядного двоичного параллельного кода в 16-разр5вдный двоичный параллельный код. Входной регис состоит из триггеров 17.1-17.16 тип D и элемента 18, состоящего из двух логических элементов 2И. Информационные входы D-триггеров 17.1-17.16 (шины 1-8J соединяются с вторым входом .устройства, причем входы D-тригrelpoB 17.1 и 17.9, 17.2 и 17.10 и и т.д. попарно запараллелены. Входы синхронизации С-триггеров 17.1-17.8 соединяются с выходом первой схемы 2И элемента 18, а входы С-триггеров 17.9-17.16 соединяются с выходом второй схемы 2И элемента 18. К входам элемента 18 из блока 8 подведены три управляющие шины. Выходы триггеров 17.1-17.16 (шины 1-16) соединяются с входгши ко№ утатора 15 кодов, с блоками 8 и 4. Коммутатор 15 кодов состоит из элементов 19.1-19.16 2И-ИЛИ-НЕ и элемента 20 ИЛИ-НЕ. К первым схемгш совпадения элементов 19.1-19.8 подсоединен выход блока 11 (шины 1-16), а к схемам совпадения - выход блока 14 (шины 1-16). Управление прохождением информации через элементы 19.1-19.16 осуществляется блоком 8 по шине, связанной с первыми схемами совпадения элементов 19.119.16 и входом элемента 20, который выходом подключен к вторым схемам совпадения элементов 19.1-19,16. Выходы элементов 19.1-19.16 (шины 116) подключены к третьему выходу устройства, который соединен линией связи с информационными входами системы преобразователей. Блок 16,пример схемного раскрытия которого для приема и преобразования 16-разрялного двоичного параллельного кода в 8-разрядный представлен на фиг.2, состоит из триггеров 21.1-21,16 типа D, элемента 22, включающего в себя два логических элемента 211, и элементов 23.1-23.8 2И-ИЛИ-НЕ. Информационные входы 0-триггеров 21.1-21.16 подключены к первому входу устройства, который соединен линией связи с информационными выходами системы преобразователей, а С-входы синхронизации запаралле- лены и связаны с выходом блока управления. Выходы триггеров 21.1-21.16 подключены к входу блока 7, кроме того выходы триггеров 21.1-21.8 соединены с первыми схемами совпадения элементов 23,1-23.8, а выходы триггеров 21.9-21.16 - с вторыми схемами совпадения этих же элементов. Выход первой схемы 2И элемента 22 соединен с входами первых схем совпадения элементов 23.1-23.8, а выход второй схемы 2и элемента 22 с входами вторых схем совпадения элементов 23.1-23.8-К входу элемента 22 подключены три управляющие шины блока управления. Выходы элементов 23.1-23.8 подключены к четвертому выходу устройства, соединенному линией связи с ЭВП.

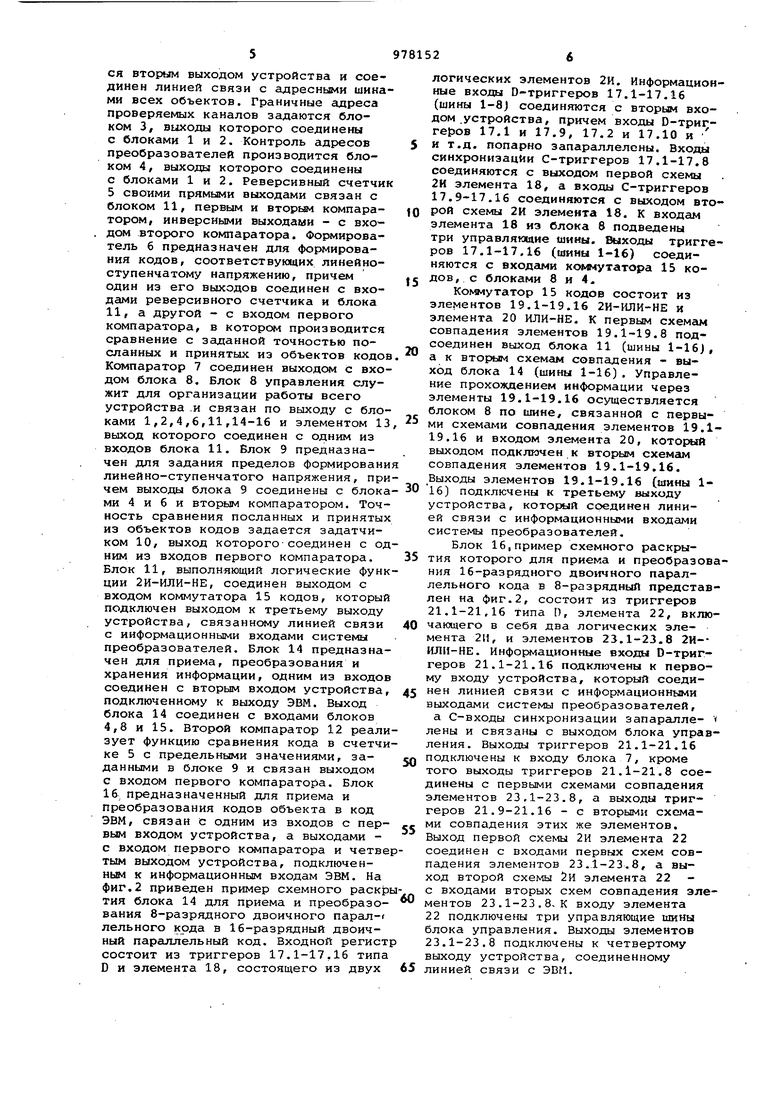

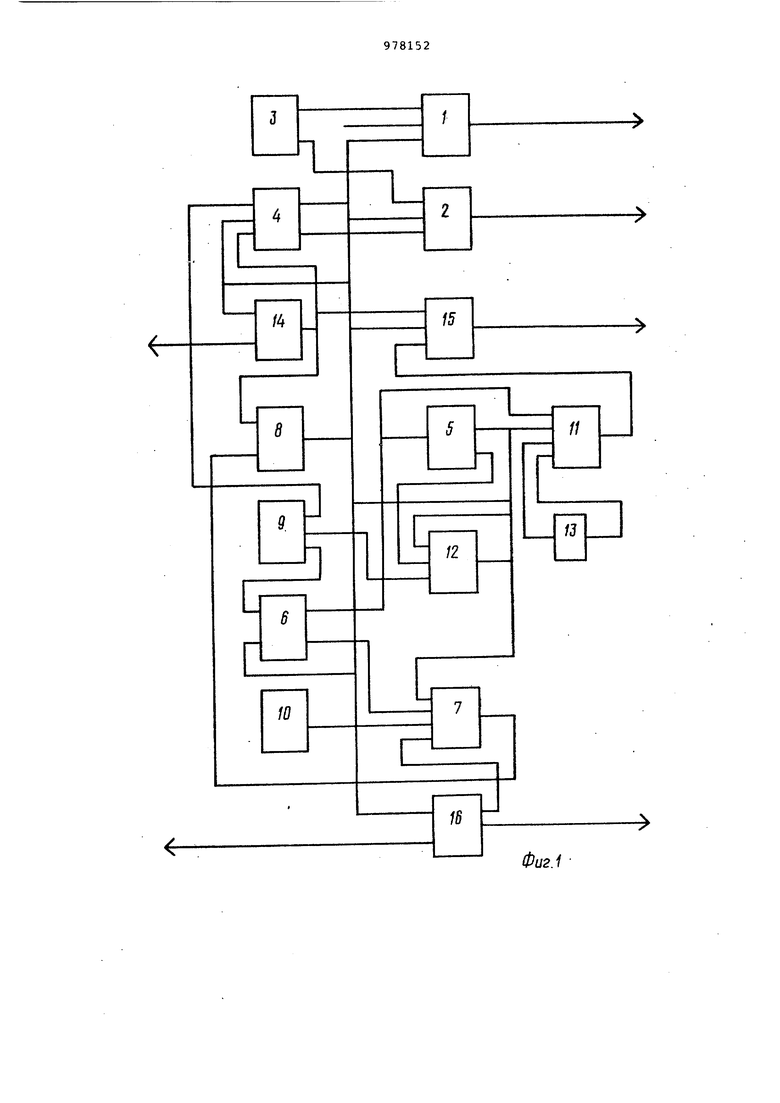

Блок управления состоит из следующих функциональных элементов и связей. Триггер 24 пуска связан 5 входом с контактом пуска 25, R входом - с первым компараторсЬм 7 прямым выходом с элементом 26 2И. ИЛИ-НЕ, инверсным выходом с элементом 27 2ИЛИ-НЕ. Элемент 27 соединен входом с контактом 28 Останов, а выходом - с R входом счетчика 29, который Ствходом подключен к выходу элемента 26, а выходами - к входам схемы 30 выработки сигналов синхронизации блоков устройства. Выходы схемы 30 подключены к выходу блока управления и к входам синхронизации С-регистров 31 и 32. Генератор 33, синхронизирующий работу всего устройства, связан с входами элемента 26 и выходом блока 8. Переключатель 34 комплексного и автономного режима работы устройства подключает общую шину (земля) в автономном режиме и контактам 35.1-35.8, служащим для записи команды управления по входам S в регистр 31. Кроме того, переключатель 34 связан через элементы 36 ИЛИ-НЕ и непосредственно с входами элемента 26. Регистр 31 служит для приема команды по входам D1-D8 из блока входного регистра 14 и своими выходами соединен с дешифратором 37, выходы которого подключены к выходу блока 8, к элементу 26 и схеме 30. Регистр 32 индикации предназначен для приема инфомационного слова из блока 14 по Dвходам. Выходы регистра 32 соединены с матрицей 38 элементов индикации на светодиодах.

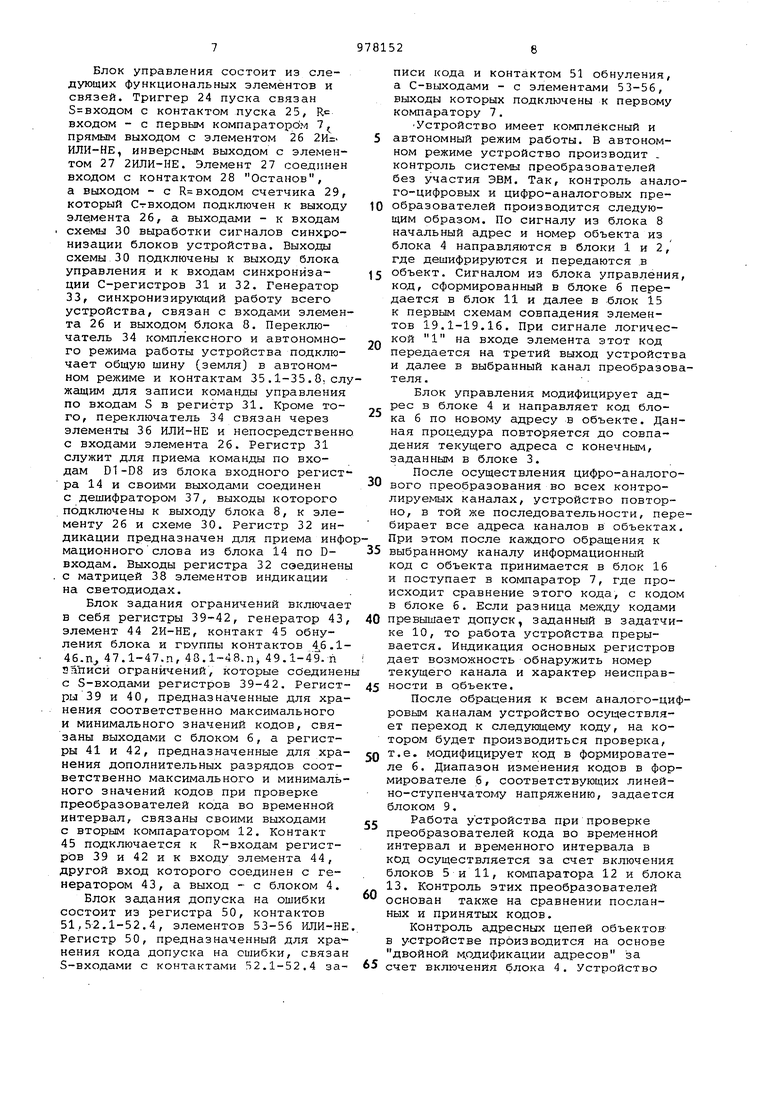

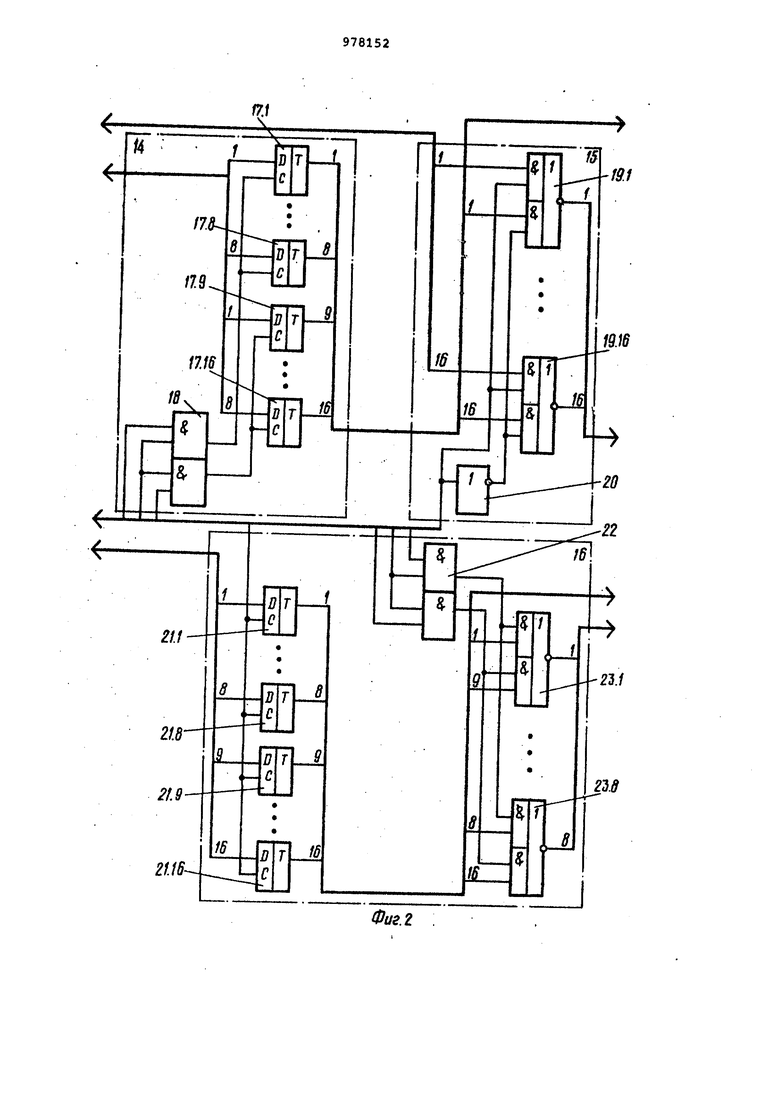

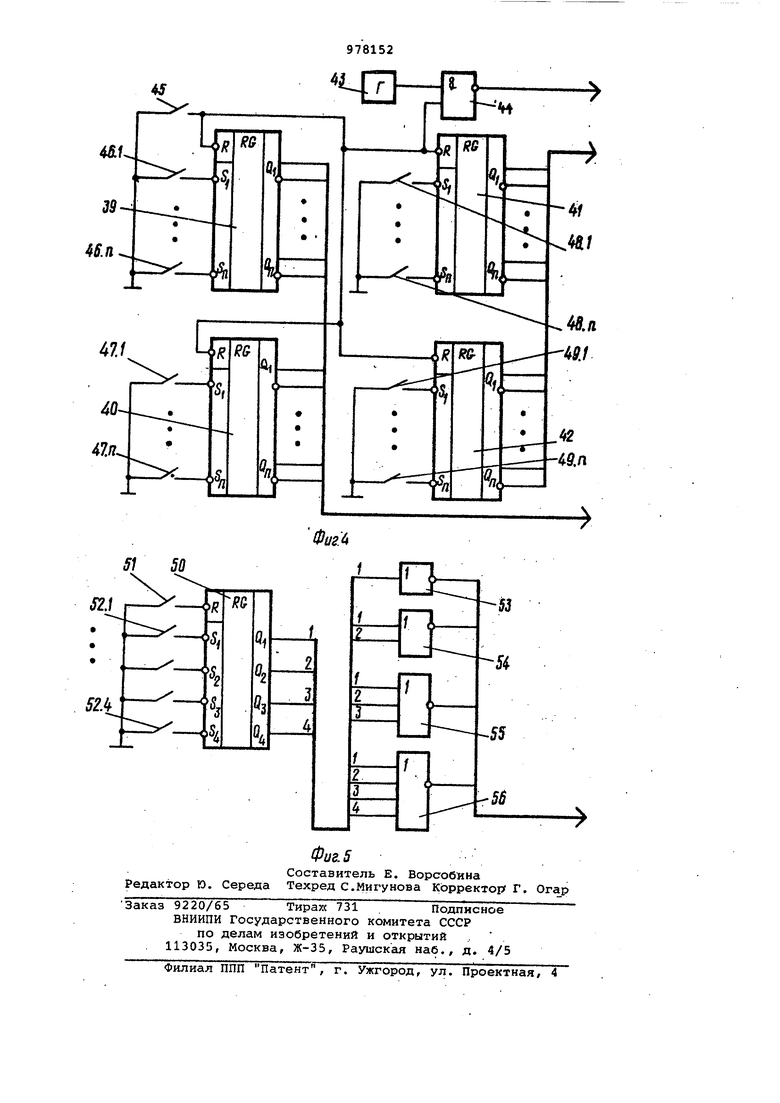

Блок задания ограничений включает в себя регистры 39-42, генератор 43, элемент 44 2И-НЕ, контакт 45 обнуления блока и группы контактов .146.п 47.1-47.п, 48.1-48.Bj 49.1-49.п Записи ограничений , которые соединен с S-входами регистров 39-42. Регистры 39 и 40, предназначенные для хранения соответственно максимального и минимального значений кодов, связаны выходами с блоком 6, а регистры 41 и 42, предназначенные для хранения дополнительных разрядов соответственно максимального и минимального значений кодов при проверке преобразователей кода во временной интервал, связаны своими выходами с вторым компаратором 12. Контакт 45 подключается к R-входам регистров 39 и 42 и к входу элемента 44, другой вход которого соединен с генератором 43, а выход - с блоком 4.

Блок задания допуска на ошибки состоит из регистра 50, контактов 51,52,1-52.4, элементов 53-56 ИЛИ-НЕ Регистр 50, предназначенный для хра нения кода допуска на ошибки, связан S-входами с контактами 52.1-52.4 записи кода и контактом 51 обнуления, а С-выходами - с элементами 53-56, выходы которых подключены к первому компаратору 7.

Устройство имеет комплексный и автономный режим работы. В автономном режиме устройство производит контроль системы преобразователей без участия ЭВМ. Так, контроль аналого-цифровых и цифро-аналоговых преобразователей производится следующим образом. По сигналу из блока 8 начальный адрес и номер объекта из блока 4 направляются в блоки 1 и 2, где дешифрируются и передаются в объект. Сигналом из блока управления код, сформированный в блоке 6 передается в блок 11 и далее в блок 15 к первым схемам совпадения элементов 19.1-19.16. При сигнале логической 1 на входе элемента этот код передается на третий выход устройств и далее в выбранный канал преобразовтеля.

Блок управления модифицирует адрес в блоке 4 и направляет код блока 6 по новому адресу в объекте. Данная процедура повторяется до совпадения текущего адреса с конечным, заданным в блоке 3.

После осуществления цифро-аналогового преобразования во всех контролируемых каналах, устройство повторно, в той же последовательности, пербирает все адреса каналов в объектах При этом после каждого обращения к выбранному каналу информационный код с объекта принимается в блок 16 и поступает в компаратор 7, где происходит сравнение этого кода, с кодо в блоке 6. Если разница между кодами превышает допуск, заданный в задатчике 10, то работа устройства прерывается. Индикация основных регистров дает возможность обнаружить номер текущего канала и характер неисправности в объекте.

После обращения к всем аналого-цировым каналам устройство осуществляет переход к следующему коду, на котором будет производиться проверка, т.е. модифицирует код в формирователе 6. Диапазон изменения кодов в формирователе 6, соответствующих линейнo-cтyпeнчaтo Гy напряжению, задается блоком 9.

Работа устройства при проверке преобразователей кода во временной интервал и временного интервала в код осуществляется за счет включения блоков 5 и 11, компаратора 12 и блок 13. Контроль этих преобразователей основан также на сравнении посланных и принятых кодов.

Контроль адресных цепей объектов в устройстве производится на основе двойной кодификации адресов за счет включения блока 4. Устройство

изменяет адреса -в блоке 4 таким образом/ что в каждый текущий цикл проверки линейно-ступенчатые коды ВЕЛдаются только по одному адресу в объекте, информация в других каналах данного объекта остается зафиксированной. При неисправности адресных цепей посланные и считанные из объекта коды различны и устройство остановится по не сравнению кодов в компараторе 7.

В комплексном режиме устройство осуществляет прием, преобразование и выдачу кодов как при передаче информации из ЭВМ в систему преобразователей (режим Запись), так и при передаче информации от преобразователей в ЭВМ (режим Чтение). Работа устройства в комплексном режиме начинается приемом в ЭВМ управляющей информации, выполняемой команды и начального адреса преобразователя. При сигнале логической 1 на первой схеме 2И элемента 18, сигнал блока управления, приходящий на первую и вторую схему 2И элемента 18, поступает на С-входы синхронизации элементов 17.1-17.8. При этом код выполняемой команды переданный из ЭВМ на второй вход устройства, будет записан в триггерах 17.117.8 Аналогичным образом в следующем такте, при сигнале логической 1 на второй схеме 2И элемента 18, код ЭВМ с начальным адресом, записывает ся в триггерах 17.9-17-. 16. Далее устройство переписывает команду из триггеров 17.1-17.8 в блок 8, а начальный адрес из триггеров 17.9-17.16 в блок 4. Этот адрес поступает в блоки 1 и 2, где формируется и передается в систему преобразователей,

После приема управляющих кодов, режим Запись осуществляется следующим образом. Первый информационный байт из ЭВМ записывается в триггерах 17.1-17.8 сигналом, сформированным на выходе первой схемы 2 И элемента 18, а второй байт - в триггерах 17.9-17.16, сигналом с выхода второй схемы 2 И элемента 18. При потенциале логической 1 на выходе элемента 20, код триггеров 17.1-17.1 поступит на входы элементов 19.1-. fl9,16 и далее в выбранный канал преобразователей. После модификации адресов в блоке 4 и передаче их в блоки 1 и 2 и в систему преобразователе устройство осуществляет прием новых информационных кодов в триггерах 17 17.16 и передает их в объект.

В режиме Чтение, после приема управляющих кодов из ЭВМ, устройство принимает информацию из преобразователей в триггера 21.1-21.16. по П входам. Этот прием синхронизируется сигналом блока управления, поступающим на С-входы триггеров 21

21.16. Выдача информации из триггеров 21.1-21.16 в ЭВМ происходит за два такта. В первом такте сигнал блока управления, поступающий на оба Логи 1еских элемента 2И элемента 22, при условии логической 1 на входе первой схемы 2И элемента 22, передает информацию триггеров 21.1-21.8 на выходы элементов 23.1-23.8 и далее в ЭВМ. Во втором такте блок 8 формирует сигнал на выходе второй схемы 2И элемента 22, который передает код триггеров 21.9-21.16 через элементы 23.1-23.8 в ЭВМ. После модификации адресов в блоке 4 и передачи их в систему преобразователей, устройство осуществляет прием в триггера 21.121.16 информационного кода следующего канала и передачу этого кода в ЭВМ. Момент окончания режимов Чтение и Запись определяется ЭВМ.

0

В комплексном режиме устройство осуществляет также контроль и индиIкацию проходящей через него информаI ции. Для этого используются имеющиеся в устройстве блоки. Так, в режиме

5 Запись информация из ЭВМ принимается в триггера 17.1-17.16 и поступает в блок управления, где по-заранее выбранному адресу фиксируется в регистре индикации блока 8. В ре0жиме Чтение информационный код из преобразователей, поступающий в триггера 21.1-21.16, передается в блок 7, где также фиксируется в регистре индикации. Выбор и индикация нужных

5 слов из информационных массивов позволяет осуществлять визуальный контроль проходящей информации в комплексном режиме и следить за правильностью работы преобразователей и ЭВМ

0 в процессе эксплуатации.

Кроме того, в режиме Чтения код из преобразователей сравнивается в блоке 7 с максимальным или минимальным значением, заранее набранньп 1 в формирователе 6. При превыше5нии допуска, заданного в задатчике 10, блок управления выдает сигнал ошибки на индикацию, что дает возможность контролировать моменты выхода измерительной информации объек0та за заданные пределы.

Таким образом, введение блоков 14 и 16 и комдмутатора 15 кодов позволяет достичь поставленную в изобретении цель. Так, прием и передача инфор5мационных кодов в систему преобразователей осуществляется всегда по одним и тем же каналам связи как в режиме контроля преобразователей, так и в режиме обмена их с ЭВМ. Адрес0ная информация в обоих режимах поступает в преобразователи из блоков 1 и . 2,й информационные коды - из коммутатора 15. Прием кодов из преобразователей производится всегда в элементы 21.1-21.16 блока 16. Этим достигается полная идентичность параметров сигналов в линиях связи устройства контроля с объектом как в режиме проверки, так и в режиме обмена преобразователей с ЭВМ что гарантирует более качественный контроль системы преобразователей,- ее интерфейсных блоков и канала связи.

Кроме того, расширились функциональные возможности устройства. К функциям контроля системы преобразователей добавились функции по организации связи с ЭВМ: передача,прием и распределение служебных и информационных кодов, преобразование форматов кодов при согласовании разрядных сеток ЭВМ и преобразователей. Предлагаемое устройство имеет возможность визуального контролирования кодов при обмене преобразователей, с ЭВМ и сравнения значений источников информации с заданными пределами.

Возможность связи с ЭВМ, более качественный контроль преобразователей, их интерфейсных блоков и канала связи, визуальный контроль информации в процессе эксплуатации, расширяют область применения предлагаемого устройства, и повышают эксплуатационную надежность автоматизированных систем при полунатурном моделировании реальных объектов, при проведении измерительных научных .экспериментов.

Формула изобретения

Устройство для контроля систем, преобразователей информации, содержащее блок управления, первый выход которого подключен к первым входам блока выбора объекта, блока коммутации адресов, блока элементов 2ИИЛИ-НЕ, блока элементов ИЛИ-НЕ, формирователя линейно-ступенчатого напряжения и блока проверки адресных цепей, первый и второй выходы которого соединены с вторыми входами соответственно блока выбора объекта и блока коммутации адресов, третьи , входы которых подключены к соответствующим выходам блока задания граничных адресов, а выходы являются управляющими выходами устройства, первый выход формирователя линейноступенчатого напряжения соединен с 5 входс реверсивного счетчика и вторым входом блока элементов 2И-ИЛИНЕ, а второй выход - с первым входом первого компаратора, второй вход которого подключен к выходу задатчиO ка допусков, выход - кпервому входу блока управления, а третий вход к первому выходу реверсивного счетчика , третьему входу блока элементов 2И-ИЛИ-НЕ, первому входу и выхо5 ДУ второго компаратора; второй вход которого соединен с вторглм выходом реверсивного счетчика, а третий входс первым выходом блока задания ограничений , второй выход которого подключен к второму входу блока проверки ад1 есных цепей, третий выходк йтЬрому входу формирователя линейно-ступенчатого напряжения, отличающееся тем, что, с целью расширения функциональных возможностей устройства, в введены первый и второй блоки регистров и коммутатор кодов, первый вход которого подключен к выходу первого блока регистров, второму входу блока управления и третьему входу блока провер-, ки адресных цепей, второй вход - к выходу блока управления и первым входам первого и второго блоков регистров, третий вход через блок элементов 2И-ИЛИ-НЕ - к выходу блока элементов ИЛИ-НЕ, первый выход второго блока регистров соединен с четвертым входом первого блока компараторов, а второй выход является инфор0 маЦионным выходом устройства, вторые входы первого и второго блоков регистров являются информационными входами устройства.

Источники информации,

5 принятые во внимание при экспертизе

1.Авторское свидетельство СССР 642710, кл. G 06 F 11/02, 1976.

2.Авторское свидетельство СССР по заявке 2777966/18-24,

0 кл. G 06 F 11/02, 1979 (прототип).

Фиг.1

Фиг. г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроляКОдОВыХ пРЕОбРАзОВАТЕлЕй | 1979 |

|

SU822191A1 |

| Устройство для отображения полутонового изображения на экране телевизионного приемника | 1988 |

|

SU1522273A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1629910A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1762280A2 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Стенд для испытания энергоустановок электромобилей | 1985 |

|

SU1255890A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

Авторы

Даты

1982-11-30—Публикация

1980-04-11—Подача