узел подготовки вида проверки, соетоящий из второго буферного регистра, второго блока элементов И, второго и третьего формирователей одиночных импульсов, сдвигового регист формирования управляющих сигналов, второго элемента И и второго RS-три гера, узел формирования управляющих сигналов опроса, состоящий из блока элементов ИЛИ, третьего блока элементов И, сдвигового регистра опроса и третьего элемента И, блок задержки и пятьш элемент ИЛИ, соединенный первым входом с выходом втор го формирователя одиночных импульсов и управляющим входом второго буферного регистра, вторым входом - с выходом третьего формирователя одиночных импульсов и первым входом второго блока элементов И, третьими входами - с первой группой выходов блока элементов ИЛИ и информационными выходами устройства, четвертыми входами - с второй группой выходов блока элементов ИЛИ и управляющими входами коммутатора, а выходом - с управляющим входом блока задержки, . тактовьй вход которого подключен к выходу формирователя тактовых импуль сов, выхбд - к первым входам второго и третьего элементов И, а информацио 1ный вход - к выходам первого блока элементов И, подсоединенных к первым входам третьего блока элементов И, первьм входам блока индикации, вторым входам второго блока эле ментов И и третьего элемента РШИ, первые входы первого блока элементов И соединены с выходом первого буферного регистра, вторые входы - с выходами сдвигового регистра формирования вида проверки, выход последнего разряда которого связан с третьим входом первого элемента ИЛИ, а тактовый вход - с первым выходом формирователя тактовых импульсов, подключенного входом тактирования к выходу формирователя тактовых импульсов, а первым и вторым входами управления к выходам третьего и четвертого элементов Ш1И, первый вход четвертого (элемента ИЛИ связан с четвертым выходом блока формирователей импульсов управления, а второй - с выходом первого формирователя одиночных импульсов, второй выход формирователя импульсов сдвига соединен с S-входом второго RS-триггера, подключенного выходом к второму входу третьего элемента И, третий вход которого связан с выходом формирователя тактовых импульсов, а выход - с тактовым входом сдвигового регистра управляющих сигналов, соединенного первым и вторым выходами с управляющими входами второго и третьего формирователей одиночных импульсов, тактовые входы которого связаны с выходом формирователя тактовых импульсов, третий выход сдвигового регистра управления сигналов соединен с R-входом второго RS-тригГера, четвертьй выход с вторым входом второго элемента ИЛИ, третий вход второго элемента И подключен к выходу формирования сигнала конца преобразования преобразователя кода, инфорь ационные выходы которого соединены с вторыми входами блока индикации,.вход управления с вторым выходом блока элементов 2К-ИЛИ, тактовый вход - с выходом формирователя тактовых импульсов, адресные входы с вьгходами формирователя адресных сигналов, выход первого RS-триггера соединен с третьим входом третьего элемента И, подключенного выходом к тактовому входу сдвигового опроса, связанного выходами с вторыми входами третьего блока элементов И, а выходом последнего разряда - с вторым входом первого элемента И, выходы третьего блока элементов И соединены с входами блока элементов ИЛИ, третий выход которого связан с входом опроса блока элементов 2И-ИЛИ, четвертый выход с четвертым входом первого элемента ИЛИ, пятьй выход - с тактовьм входом формирователя адресных сигналов, второй вход блока элементов 2И-Ш1И соединен с выходом компаратора, первым входом связанного с выходом блока усилителей, вторым входом - с первым эыходом блока эталонных напряжений, управляющие входы блока усилителей и блока эталонных напряжений соединены с выходом второго буферного регистра, информационные входы блока усилителей подключены к выходам коммутатора, а второй выход блока эталонных напряжений - к выходу задания воздействий коммутатора. Изобретение относится к автоматике и вычислительной технике, в частности к устройствам проверки и контроля целостности электрических цепей (Измерения их сопротивлений и проварки функционирования радиоэлементов, входящих в проверяемое электронное устройство. Известно устройство для контроля цифровых блоков, которое содержит блок ввода , блок управления, блок сравнения, блок индикации, коммутатор, блок памяти, пять регистров, дешифратор и задатчик нагрузки l . Недостатком устройства является сложность структурного и схемного построения, требующего для реализации значительного количества оборуд вания и больших материальных затрат Известно также устройство для контроля монтажныхсоединений, содержащее последовательно соединенны блок управления, генератор импульсов, счетчик импульсов, дешифратор и коммутатор, выход которого подклю чен к входам блоков ввода и вывода программы, выходы которого соединен с входами блока управления, элементы неравнозначности, одни входы которых соединены с выходами блока вв да программ, а выходы - с входами блока вывода программы 2j , I Недостатком данного устройства является невысокая надежность конт роля, так как он осуществляется сра нением с эталоном, и ошибка по несравнению не анализируется качестве но. Наиболее близким по технической сущности к изобретению является уст ройство для проверки электрического монтажа, содержащее узел связи с контролируемым объектом, входы кото рого подключены к соответствующим выходам коммутатора и соответствующ информационным входам коммутатора опроса, адресный вход которого подключен к выходу счетчика точек и первым входам буферного регистра и узла ввода-вывода, адресный регистр дешифратор, счетчик цепей, регистр количества точек, схемы сравнения, генератор импульсов, соединенный с узлом управления, который соединен со схемой сравнения, счетчиком точек, счетчиком цепей, адресным регистром и узлом ввода-вывода sj Недостатком известного устройства является невозможность проверки сопротивлений радиоэлементов, входящих в контролируемый блок. Так, например, наличие сопротивления в проверяемой цепи, составляющее десятки Ом, регистрируется как неисправность, т.е. обрыв цепи. Кроме того, отсутствует возможность осуществления проверки во включенном состоянии объекта, что необходимо, например, для проверки релейных блоков с нормально разомкнутыми контактами. Указанные недостатки приводят к снижению достоверности проверки электрического монтажа, увеличению времени процесса проверки так как известное устройство требует затраты на разработку, изготовление рабочих программ, что экономически не выгодно при организации проверки монтажа узлов с малоемким монтажом и малой серии изготовления. Целью изобретения является повышение достоверности результатов контроля электрического монтажа за счет проверки контролируемого блока во включенном состоянии. I Указанная цель достигается тем, что в устройство для контроля электрического монтажа, содержащее блок индикации, формирователь тактовых импульсов, соединенный с входами тактирования первого формирователя. одиночных импульсов и блока формирователей импульсов управления, четьфе информационных входа которого связаны с соответствующими выходами клавиатуры, шинами адреса соединенной с информационными входами формирователя адресных сигналов и регистра адреса, а шинами вида проверки с информационными входами первого буферного регистра, управляющими входами формирователь адресных CHI- налов, регистр адреса и первый буферньш регистр подключены соответственно к первому, второму и третьему выходам блока формирователей импульсов управления, четвертым выходом соединенного с первым входом первого элемента ИЛИ узла формирования прерываний, состоящего из первого RSтриггера, второго элемента ИЛИ и первого элемента И, соединенного выходом с информационным входом первого формирователя одиночных импульсов и вторым входом первого элемента ИЛИ,

выход которого подключен к R-входу первого триггера, S-входом связанного с выходом второго элемента ИЛИ, которьй первым входом соединен с первым выходом узла анализа результата проверки, состоящего из блока элементов 2И-ШПРи первого блока сравнения выход которого подключен к первому входу блока элементов 2И-ИЛИ, а первый вход совместно с информационными входами коммутатора связан с входом устройства, второй вход первого -блока сравнения соединен с выходом формирователя эталонного числа, управляющим входом связанного с выходом первого буферного регистра, а информационным - с выходом формирователя адресных сигналов, являющегося выходом адреса управления устройства, с адресным входом коммутатора и первым входом второго блока сравнения, вторым входом соединенного с (ВЫХОДОМ «регистра адреса, а выходом с первым, входом первого элемента И, введены узел измерения, состоящий из блока усилителей, компаратора и блока эталонных напряжений, преобразователь кода, узел формирования сигналов вида проверки, состоящий из третьего и четвертого элементов ИЛИ, формирователя импульсов сдвига, сдвигового регистра формирования вида проверки и первого блока элементов И узел подготовки вида проверки, состоящий из второго буферного регистра второго блока элементов И, второго и третьего формирователей одиночных импульсов, сдвигового регистра формирования управляющих сигналов, второго элемента И и второго RS-тригге- , ра, узел формирования сигналов опроса, состоящий из блока элементов ШШ третьего блока элементов И, сдвигового регистра опроса и третьего элемента И, блок задержки и пятый элемент ИЛИ, соединенный первым входом с выходом второго формирователя одиночных импульсов и управляющим входом второго буферного регистра,, вторым входом - с выходом третьего формирователя одиночных импульсов и первым входом второго блока элементов И, третьими входами - с первой гуппой выходов блока элементов ИЛИ и информационными выходами устройства, четвертыми входами - с второй группой выходов блока элементов ИЛИ и управляющими входами коммутатора.

а выходом - с управляющим входом блока задержки, тактовый вход которого подключен к выходу формирователя тактовых импульсов, выход - к первым входам второго и третьего элементов И, а информационный вход к выходам первого блока элементов И подсоединенных к первым входам третьего блока элементов И, первым входам блока индикации, вторым входам второго блока элементов И и третьего элемента ИЛИ, первые входы первого блока элементов И соединены с выходом первого буферного регистра, вторые входы - с выходами сдвигового регистра формирования вида проверки, выход последнего разряда которого связан с третьим входом первого элемента ИЛИ, а тактовый вход - с первым выходом формирователя импульсов сдвига, подключенного входом тактирования к выходу формирователя тактовых импульсов, а первым и вторым входами управления - к выходам третьего и четвертого элементов ИЛИ, первый вход четвертого элемента ИЛИ связан с четвертым выходом формирователя импульсов управления, а второй вход - с выходом первого формирователя одиночных импульсов, второй выход формирователя импульсов сдвига соединен с S-входом второго RS-триггера, подключенного выходом к второму входу третьего элемента И, третий вход Которого связан с виходом формирователя тактовых импульсов,, а выход - с тактовым входом сдвигового регистра управляющих сигналов, соединенного первым и вторым выходами с управляющими входами второго и третьего формирователей одиночных импульсов, тактовые входы которого связаны с выходом формирователя тдктовых импульсов, третий выход сдвигового регистра управляющих сигналов соединен с R-входом второго RS-триггера, четвертый выход - с вторым входом второго элемента ИЛИ, третий вход

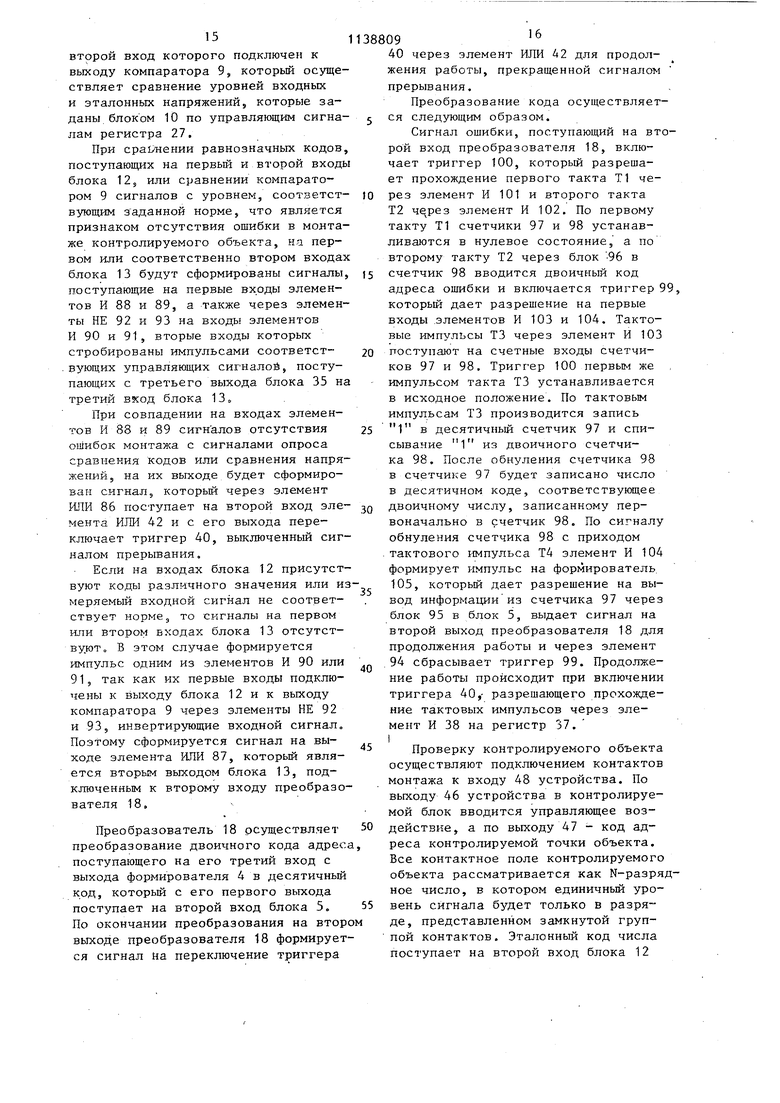

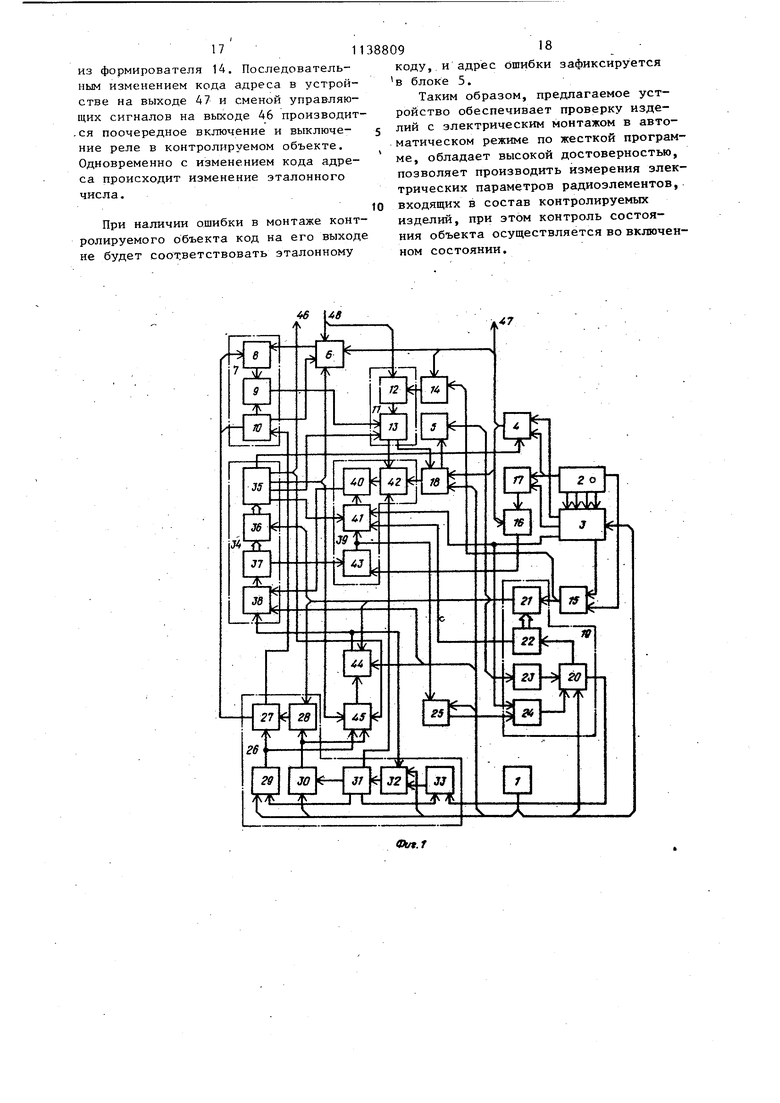

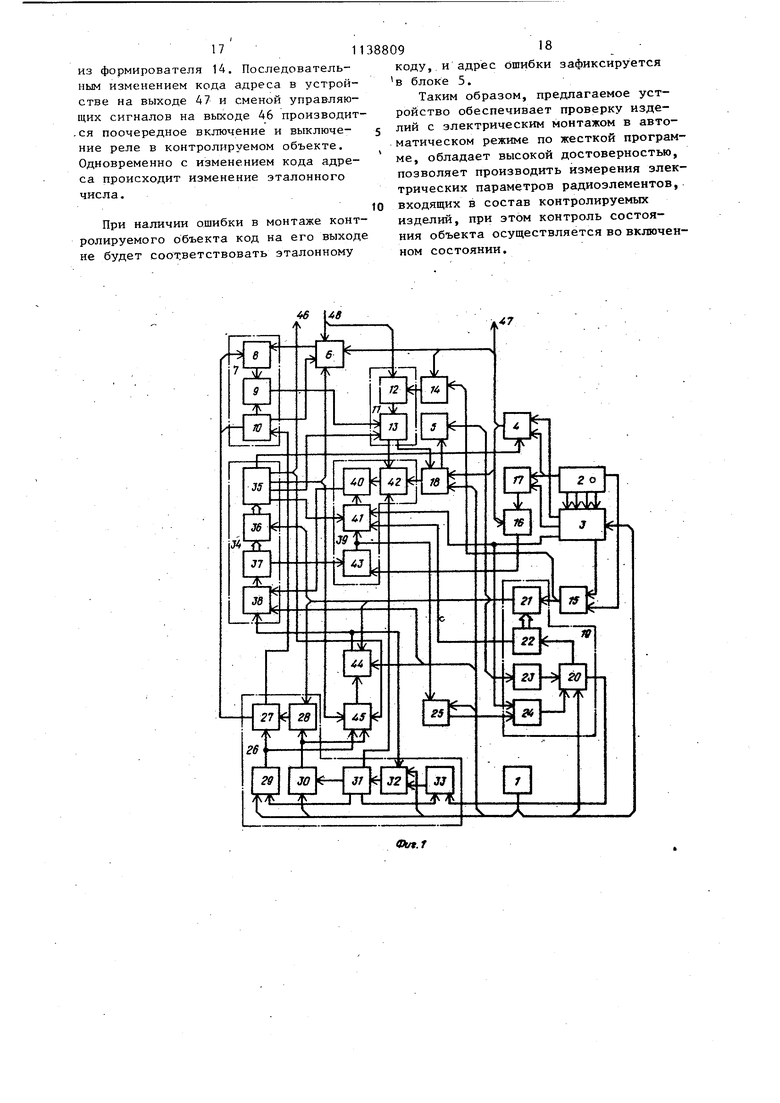

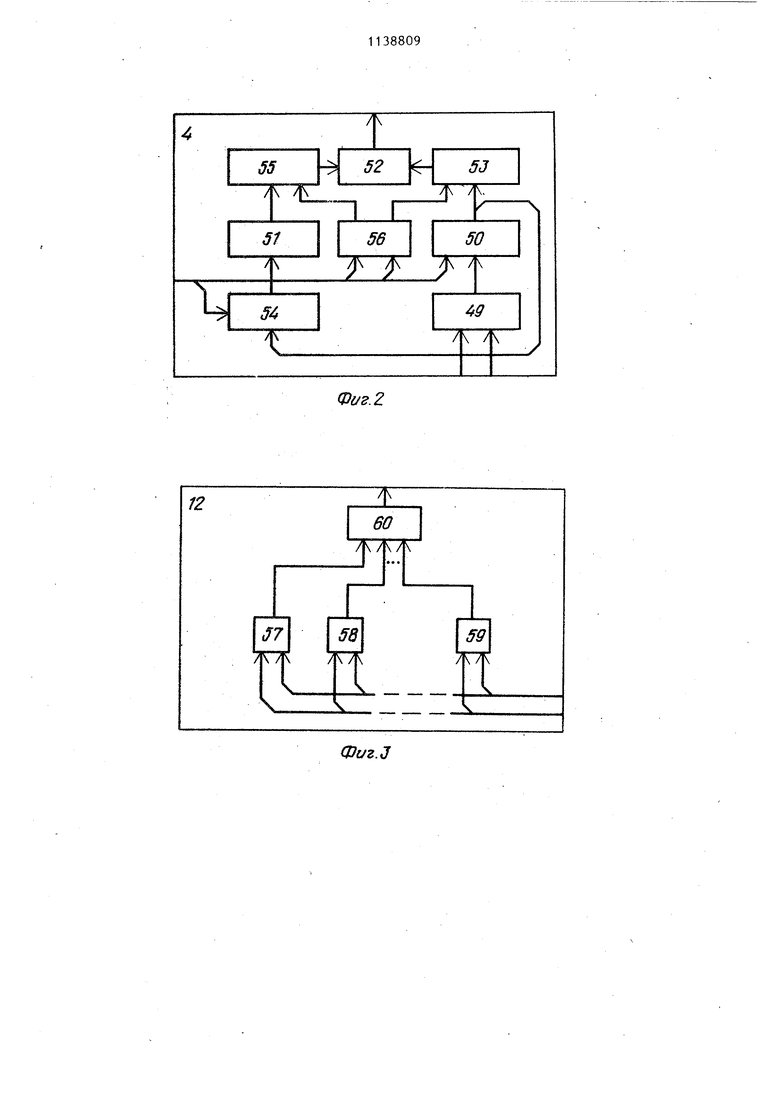

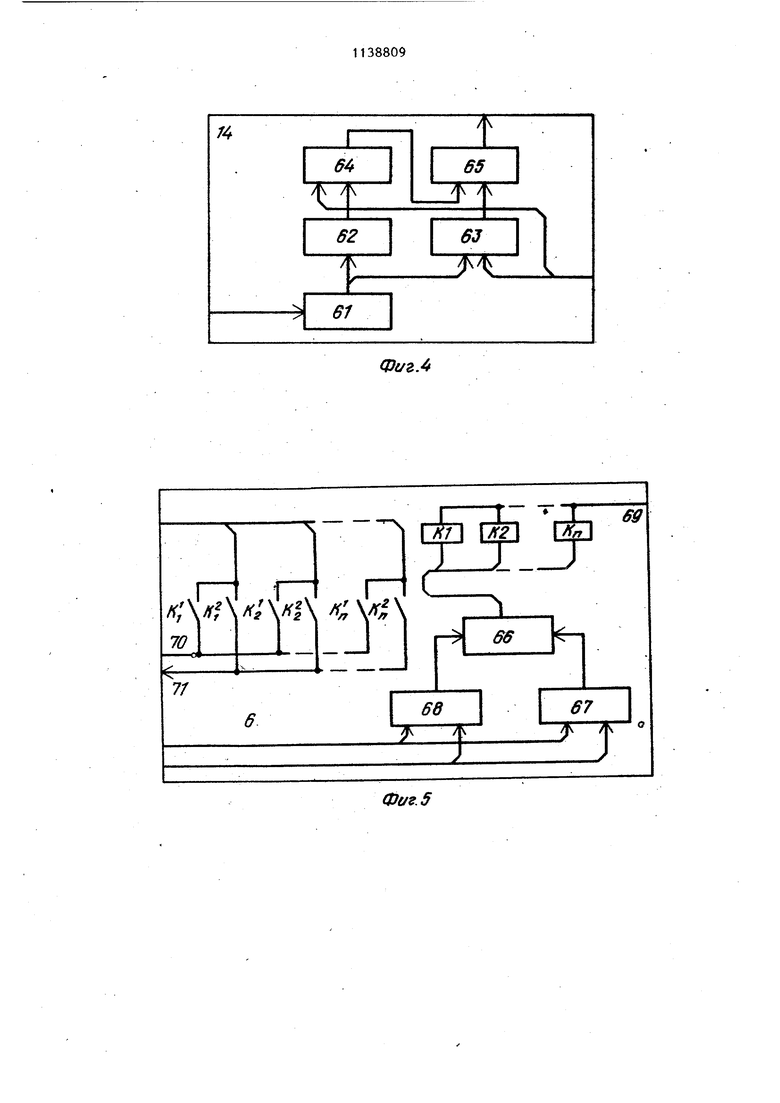

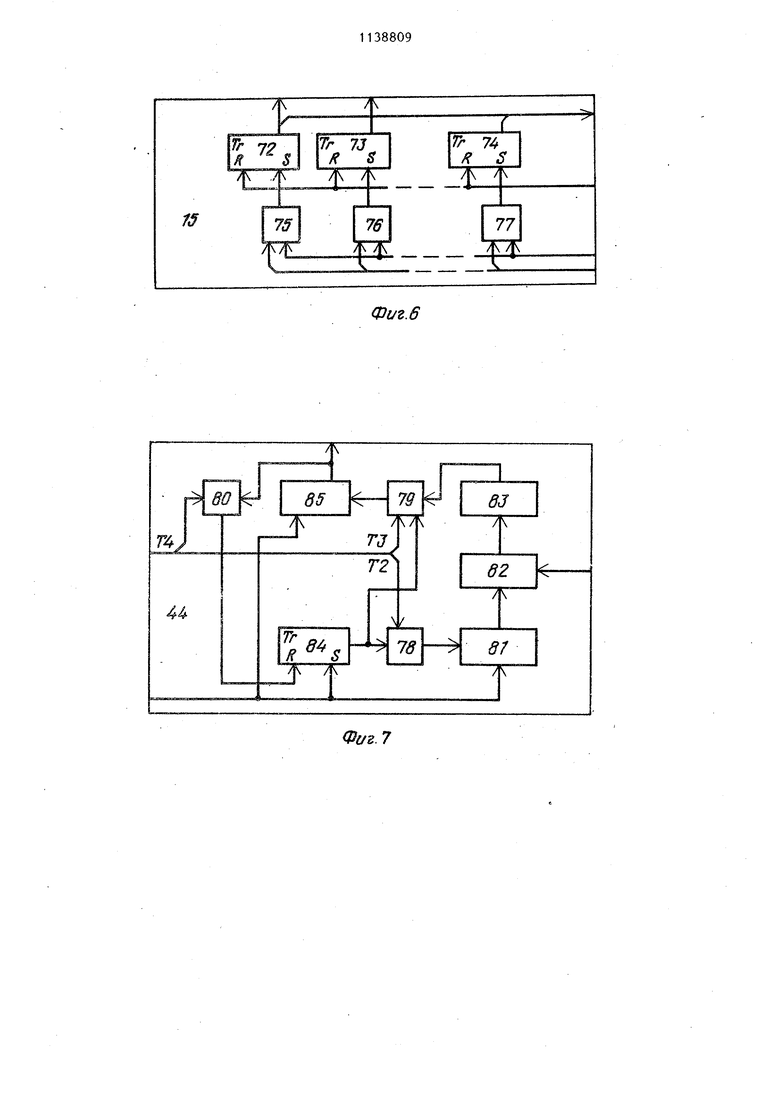

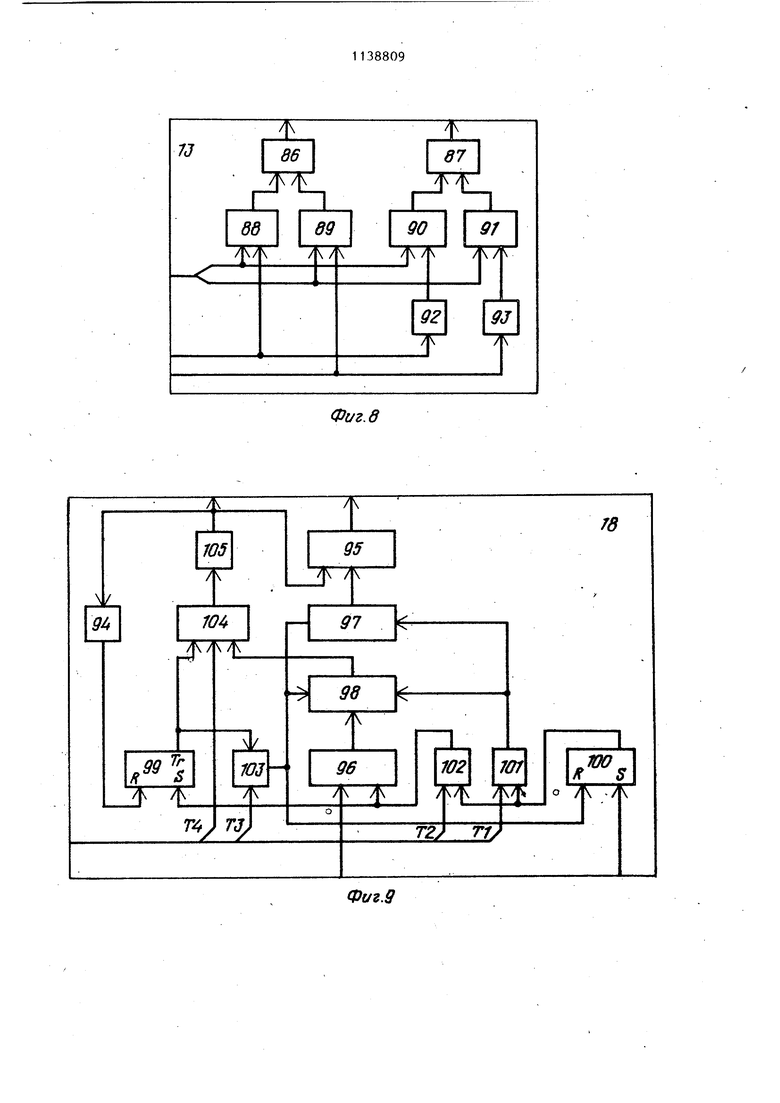

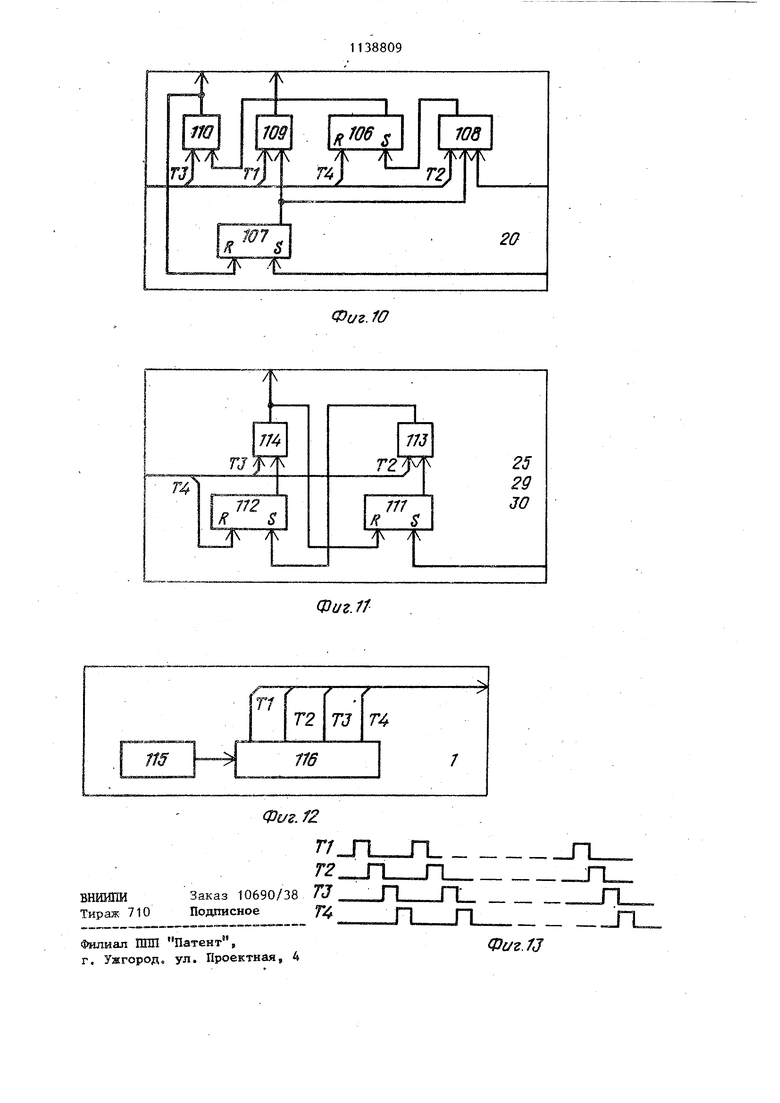

второго элемента И подключен к выходу формирования сигнала конца преобразования преобразователя кода, информационные выходы которого соединены с вторыми входами блока индикации, вход управления - с вторым выходом блока элементов 2И-ИЛИ, тактовый вход - с выходом формирователя тактовых импульсов, адресные входы с выходами формирователя адресных 5 , сигналов, выход первого RS-триггера соединен с третьим входом третьего элемента И, подключенного выходом к тактовому входу сдвигового регистра опроса, связанного выходами с вторыми входами третьего блока элементов И, а выходом последнего разряда - с вторым входом первого элемента И, выходы третьего блока элементов И соединены с входами блока элементов ИЛИ, третий выход которого связан с входом опроса блока элементов 2И-ИЛИ четвертый выход - с четвертым входом первого элемента ИЛИ, пятый выход с тактовым входом формирователя адресных сигналов, второй вход блока элементов 2И-ИЛИ - с выходом компаратора, первым входом связанного с выходом блока усилителей, вторым, вхо дом - с первым выходом блока эталонных напряжений, управляющие входы блока усилителей и блока эталонных напряжений соединены с выходом второ го буферного регистра, информационные входы блока усилителей подключены к выходам коммутатора, а второй выход блока эталонных напряжений к входу задания воздействий коммутатора. На фиг. 1 представлена схема устройства; на фиг. 2 - схема формирова теля адресных сигналов; на фиг. 3 схема блоков сравнения; на фиг. 4 схема формирователя эталонных чисел на фиг. 5 - схема коммутатора; на фиг. 6 - схема первого буферного регистра; на фиг. 7 - схема блока задержки; на фиг. 8 - схема блока анализа результатов проверки; на фиг.9 схема преобразователя кода; на фиг. 10 - схема формирователя импул сов сдвига; на фиг. 11 и 12 - схема формирователя тактовых импульсов; на фиг. 13 - временная диаграмма ра боты формирователя тактовых импульсов. I Предлагаемое устройство содержит (фиг. 1) формирователь 1 тактовых импульсов, клавиатуру 2, блок 3 формирователей импульсов управления, формирователь А адресных сигналов, блок 5 индикации, коммутатор 6, узел 7 измерения, который содержит блок усилителей, компаратор 9 и блок 10 эталонных напряжений, уз.ел 11 анализа результатов проверки, который содержит первый блок 12 сравнения и бло 13 элементов 2И-ИЛИ, формирователь 09 14 эталонного числа, первый буферный регистр 15-, второй блок 16 сравнения, регистр 17 адреса, преобразователь 18 кода, узел 19 формирования сигналов вида проверки, который содержит формирователь 20 импульсов сдвига, первый блок 21 элементов И, сдвиговый регистр 22 формирования вида проверки, третий элемент ИЛИ 23 и четвертый элемент ИЛИ 24, первьм формирователь 25 одиночных импульсов, узел 26 подготовки вида проверки, который содержит второй буферный регистр 27, блок 28 элементов И, второй 29 и третий 30 формирователи одиночных импульсов, сдвиговый регистр 31 формирования управляющих Сигналов, второй элемент И 32 и второй RS-триггер 33, узел 34 формирования сигналов опроса, который содержит блотс 35 элементов 11ПИ, третий блок 36 элементов И, сдвиговый регистр 37 опроса, третий элемент 38 И, узел 39 прерывания, который содержит первый RS-триггер 40, первый 41 и второй 42 элементы ИЛИ и первый элемент И 43, блок 44 задержки, пятый элемент ИЛИ 45, первый выход 46, второй выход 47 и вход 48 устройства. Формирователь 4 адресных сигналов (фиг. 2) содержит блок 49 элементов И, счетчик 50, регистр 51, блок 52 элементов ИЛИ, блоки 53-55 элементов И и триггер 56. Первый 12 и йторой 26 блоки сравнения (фиг. 3) состоят из элементов 57-59 сравнения и элемента И 60. Формирователь 14 эталонного числа (фиг. 4) содержит дешифратор 61, блок 62 элементов НЕ, блоки 63 и 64 элементов И и блок 65 элементов ШШ. Коммутатор 6 (фиг. 5) содержит регистр 66, дешифраторы 67 и 68, шину 69 источника питания, шины 70 и 71. Первый буферный регистр 15 (фиг.6) содержит триггеры 72-74 и элементы И 75-77. Блок 44 задержки (фиг. 7) содер- жит элементы И 78-80, счетчик 81, блок 82 элементов И, элемент ИЛИ 83, триггеры 84 и 85, Узел 11 анализа результатов проверки (фиг. В) содержит элементы ИЛИ 86 и 87, элементы И 88-91,. элементы НЕ 92 и 93. преобразователь 18 кода (фиг.9) содержит элемент 94 задержки, блоки 95 и 96 элементов И, счетчики 97 и 98, триггеры 99 и 100, элементы И 101-104 и формирователь 105 одиночных импульсов. Формирователь 20 импульсов сдвиг содержит (фиг. 10) триггеры 106 и 107 и элементы И 108-110, Формирователи 25, 2.9 и 30 одиноч ных импульсов содержат (фиг. 11) триггеры 111 и 112 и элементы И 113 и 114. Формирователь тактовых импульсов (фиг. 12) состоит из генератора 115 импульсов и сдвигающего регистра 11 который формирует четыре тактовых импульса Т1, Т2, ТЗ и Т4. Коммутатор 6 (фиг. 5) содержит также группу реле и группу соответствую1щих контактов. Клавиатура 2 выполнена на перекл чателях, например, типа П2К (содерж группу переключателей для задания кода адреса по пятому выходу, группу переключателей для задания видов проверки по шестому выходу и группу переключателей для формирования оди ночных импульсов с первого - четвер того выходов). На фиг. 1-12 цепи источников пит ния элементов схемы устройства и це пи установки нулевого состояния эле ментов памяти (триггеров) условно не показаны. На функциональных схемах устройс на связи с разветвлением рассчитаны на группу различных сигналов. Так, например, сигналы видов проверки, объединенные линией связи с выхода блока 21, формируются различными . элементами, входящими в состав блока, содержащего количество цепей связи, соответствующих разрядности регистра 15, Устройство работает следукщим об разом. Виды проверок, начальный и конеч ный адрес точ-ек контролируемого объ екта устанавливаются соответствующими переключателями на клавиатуре 2 и вводятся в блоки устройства включением переключателей, которые управляют формированием импульсов по входам блока 3. Импульсом с первого выхода блока 3 вводится начальный адрес проверки в формирователь 4. Импульсом 098 с второго выхода блока 3 в регистр 17 вводмтся адрес последней точки конт ролируемого объекта. Импульсом с третьего выхода блока 3 в регистр 15 вводятся виды проверок, которым подлежит контролируемый объект. Каждьй вид проверки условно характеризуется включением соответствующего триггера в регистре 15. Видами проверок в устройстве, например, могут быть проверки наличия цепи, проверка разобщенности цепей, измерение сопротивления цепи (резисторов, диодов и т.д.), причем смена диапазона измерения рассматривается как смена вида проверки. Проверка контролируемого объекта может производиться по всем видам проверки и части из них. Переход к следующему заданному виду осуществляется автоматически по окончании проверки в последней точке контролируемого объекта, заданные виды проверок запоминаются включенными триггерами 11-1k регистра 15. Сигнал одного триггера управляет только одним определенным видом проверки (на фиг. 6 условно показано только три , разряда). Вид проверки формируется при одновременном поступлении сигналов на два входа соответствующих элементов И блока 21. Регистр 22 обеспечивает продвижение единичного сигнала по разрядам в естественном, последовательном порядке, и единичньй сигнал может присутствовать на выходе только одного разряда, а сигнал вида проверки может быть сформирован на выходе только одного из элементов и блока 21, на входах которого, будет совпадение единичных сигналов, поступающих с выходов регистра 15. Работа блоков устройства синхронизируется тактовыми импульсами, ко-торые вьфабатывает формирователь 1. Для формирования импульсов сдвига в узле 19 формирования сигналов вида проверки используются все четыре тактовых импульса, которые поступают на первый вход формирователя 20. Импульс сдвига формируется элементом И 109, который управляется по одному из входов сигналом триггера 107, а на второй вход элементов И 109 поступает импульс такта Т1. Триггер 107 выполнен по схеме типа R-S, S-вход его является вторым входом формирователя 20, подключенного к выходу элемента ИЛИ 24, первьй вход которого подключен к четвертому выходу блока 3, а второй - к выходу формирователя 25. При включении соответствующего пе реключателя кнопкой Пуск в клавиа,туре 2 в блоке 3 формируется импульс который с четвертого выхода через Ьлемент ИЛИ 24 поступает на второй вход формирователя 20 и включает триггер 107, который дает сигнал решения на входы элементов И 108 109. По первому такту Т1 на выходе эле мента И 109 сформируется импульс, которьй поступит на вход регистра 22 и на выходе его первого разряда уста новится сигнал, соответствующий единичному уровню. Если вид проверки, которому соответствует первый разряд регистра 15, не задан, и его триггер установлен в нулевое (исходное) состояние, то первый элемент И в блоке 21 импульса не формирует. При этом формирователь 20 выра батывает т тульсы и производит сдвиг единичного сигнала в регистре 22 до тех пор, пока на выходе блока 21 не сформируется сигнал единичного уровня, соответствующий заданному виду проверки. Такой процесс работы сдвига длится до ггервого включенного триггера в регистре 15. При появлении единичного сигнала на выходе блока 21 он поступает на вход элемен, ИЛИ 23, выход которого подключен к третьему входу фор мирователя 20, и связанный с ним вт рой вход элемента И 108. При этом с приходом импульса на его .третий вход по второму такту Т2 включается триггер 106, который дает разрешение прохождению третьего такта ТЗ через элемент И 110, импульс с выхо которого устанавливает триггер 107 в исходное положение. Таким оброзом процесс сдвига в регистре 22 прекращается, и на выходе блока 21 устанавливается сигнал заданного вида проверки. Триггер 106 устанавливает ся в исходное положение импульсом по четвертому такту Т4. Одновременно с установкой тригге ра 107 в исходное положение импульс по третьему такту ТЗ с выхода элемента И 110 через второй выход формирователя 20 поступает на первый вход триггера 33 узла 26, который осуществляет подключение блоков устройства, необходимых для выполнения процесса проверки контролируемого блока по заданному виду проверки. Процесс подготовки осуществляется следующим образом. Включенный триггер 33 выдает сигнал разрешения на второй вход элемента И 32, на третий вход которого поступает единичный уровень сигнала с выхода триггера 85 блока 44, В исходном состоянии устройства триггер 85 установлен в положение, в котором на его выходе, являющемся вькодом блока 44, установлен единичный уровень сигнала. По такту Т1, который поступает с выхода формирователя 1 на первый вход элемента И 32, на его выходе формируется импульс, который поступает на вход четырехразрядного сдвигового регистра 31, первый выход которого управляет формирователем 29. Импульс с выхода формирователя 29, поступающий на первый вход регистра 27, устанавливает триггеры, входящие в его состав, исходное состояние , и они отключают ранее включенные усилители блока 8 и блоки 10. Одновременно импульс с выхода формирователя 29 поступает на первый вход элемента ШШ 45, с выхода которого импульс по второму входу .включает. блок 44. При этом триггер 85 переключается и на третьем входе элемента И 32 устанавливается запрещающий сигнал, и тактовьш импульс Т1 не формируется на его выходе. Формирование задержки осуществляется следующим образом. При поступлении импульса ни второй вход блока 44 счетчик 81 устанавливается в нулевое состояние, и включается триггер 84, который дает разрешение на первые вподы элементов И 78 и 79, на вторые входы которых поступают тактовые импульсы Т2 и ТЗ соответственно. Элемент И 79 закрыт по третьему входу сигналом с выхода элемента ИЛИ 83. Второй такт Т2 формирует импульс на выходе элемента И 78, которьш поступает на счетньй вход счетчика-81, сигналы с выхода разрядов которого поступают на первые входы блока 82, на вторые входы которо11го подаются сигналы вида проверки. Когда счетчик 81 установится в поло жение, при котором код на его выход будет соответствовать времени, заданному включенным видом проверки по вторым входам блока 82, на .выход его сформируется сигнал готовности и через элемент ИЛИ 83 даст разрешение на третий вход элемента И 79 для формирования импульса по третье му такту ТЗ, поступающему на его второй вход, при этом триггер 85 вернется в исходное состояние. Элемент И 80 по четвертому такту Т4 сформирует импульс, устанавливающий триггер 84 в исходное положение, пр котором работа счетчика 81 запрещена. С выхода триггера 85 поступает разрешение на формирование импульса вторым элементом И 32, которьй переключит регистр 31 в слехтующее положение, при котором сигнал с его второго выхода включит сЬормирователь 30, импульс с выхода которого через блок 28 включит соответствующие триггеры регистра 27 и произведет коммутацию соответствующих входов и выходов в блоке 8 и в блок 10, необходимых для выполнения опер ций по данному виду проверки. Одновременно импульс с выхода формирователя 30 поступает на второ вход элемента ИЛИ 45 и с его выхода обеспечивает формирование задержки управляющих сигналов в блоке 44. Фо мирование временных задержек при проведении подготовительных операци узлом 26 необходимо для того, чтобы избежать аварийных ситуаций в устройстве, которые могут возникнуть при переключении источников опорного напряжения в блоке 10 и установке на выходе устройства напряжений, несанкционированных данным видом проверки. После формирования временной задержки, вновь включается элемент И 32, импульсы с выхода которого по ступают на вход регистра 31, импуль с третьего выхода которого через первый вход элемента ИЛИ 42 включае триггер 40, а импульс с четвертого выхода регистра 31 устанавливает триггер 33 в исходное, нулевое состояние и запрещает формирование импульсов элементом И 32. На этом подготовка устройства к работе по з данному виду проверки закончится. 0912 Включенный триггер 40 устанавливает сигнал разрешения на третьем входе элемента И 38, на втором входе которого присутствует сигнал разрешения с триггера 85 блока 44. С приходом импульса по такту Т1 происходит совпадение единичных уровней сигналов на его входах, элемент И 38 вырабатьшает импульс на вход регистра 37, выход последнего разряда которого служит для формирования сигнала перехода на элемент И 43 после выполнения последней операции в заданном виде проверки. Импульсы с перовых выходов регистра 37 поступают на первые входы блока 36, на второй вход которого поступают сигналы вида проверки с выхода блока 21. При совпадении на входах блока 36 сигнала вида проверки и сигнала с выхода одного из ра.зрядов регистра 37 на его выходе формируется сигнал, который поступает на вход блока 35. Выход блока 36 представляет собой группы выходов элементов И, которые собраны по функциональньм значениям и соединены с входами элементов ИЛИ, входящих в Состав блока 35, По первому выходу блока 35 формируются управляющие сигналы для управления контролируемым объектом, по второму выходу - сигналы, управляющие коммутатором 6. Выполнение операций по управляющим сигналам первого и второго выходов блока 35 требуют времени больше, чем время операции сдвига на один разряд регистра 37, поэтому сигналы этих выходов осуществляют включение блока 44 по третьему и четвертому входам элемента ИЛИ 45, При включении задержки осуществляется запрет на формирование сдвигающего импульса по первому входу элемента PI 38, что обеспечивает время для выполнения операций, заданных сигналами с первого и второго выходов блока 35. Четвертый выход блока 35 формирует сигнал прерывания работы устройства, дальнейший .ход работы которого зависит от результатов выполнения предыдущих операций. С третьего выхода блока 35 формируются сигнал опроса результата узлом 7 и сигнал опроса результата сравнения кодов блоком 12, которые поступают на третий вход блока 13. По пятому выходу блока 35 формируются управляющие сигналы, которые поступают на третий вход формирователя 4, формирующие импульс адреса, импульсы переключения триггера 56, которьш управляет блоками 53 и 55 при формировании адресных сигналов с выхода счетчика 50 или регистра 5.1 и сигнал перевода кода адреса из счетчика 50 через блок 54 в регистр 51. Прерывание работы устройства достигается за счет прекращения последующего формирования управляющих сигналов при переключении первого триггера 40 в узле 39, выход которого при этом имеет сигнал нулевого уровня и закрывает по третьему входу элемент И 38, обеспечивающий формирование сдвигающего импульса на входе регистра 37. Прерывание формирования управляющих сигналов первым элементом ИЛИ 41 осуществляется в следующих случаях: по первому В7ШДУ импульсом с четвертого выхода блока 3 при пуске устройства, когда еще не сформированы сигналы видов проверки, при этом устройство и контролируемый блок защищены от аварийных ситуаций; по второму входу сигналом с выход элемента И 43, когда на его входах происходит совпадение сигналов конечного адреса проверки с выхода блока 16 и сигнала с последнего разряда регистра 37, в этом случае формирователем 26 формируется сигнал, который через второй вход элемента ИЛИ 24 включает формирователь 20 дл формирования следующего вида проверки;по третьему входу элемента ИЛИ 4 формируется сигнал прерывания при поступлении сигнала с последнего ра ряда регистра 22, который сигнализи рует конец проверки контролируемого объекта; по четвертому входу формируется сигнал прерьшания с четвертого выхода блока 35 для выполнения операции сравнения. Работа всех сдвиговых регистров устройства осуществляется в кольцевом режиме, при котором запись единицы в первый разряд производится сигналом с выхода последнего разряда. Начальная запись единицы в первый разряд из сдвиговых регистров осуществляется сигналом начальной, нулевой установки, цепь которой на функциональных схемах условно не показана. Формирование сигнала конечного адреса с выхода блока 16 достигается на основе сравнения равнозначных кодов адреса, одним из которых является текущий адрес проверки контролируемого объекта, поступающий на второй вход, и код адреса, который поступает на первый вход с выхода регистра 17, который заносится в него перед началом проверки контролируемого объекта и характеризует количество контролируемых точек. Оценка правильности монтажа контролируемого объекта осуществляется измерением параметров выходных сигналов в контролируемой точке узлом 7 или сравнением кодов при помощи блока 12. В первом случае выходные точки в контролируемом объекте последовательно подключаются к информационному входу усилителей блока 8 узла 7 при помощи коммутатора 6, адрес точки при этом задается формирователем 4. Во втором случае все точки с установивщимися на них низкими и высокими уровнями сигналов принимаются за код числа на выходе контролируемого объекта, поступающий на первый вход блока 12, на второй вход которого поступает код эталонного числа с выхода формирователя 14. Основу формирователя 14 составляет дешифратор 61, сигналы с выхода которого в прямом и инверсном коде поступают через блоки 63 и 64 в блок 65, выход которого является выходом формирователя 14. Управление формированием эталонного числа осуществляется по второму входу формирователя 14 сигналами с выходов регистра 15. Сначала сигнал разрешения поступает на управляющий вход блока 64 с выхода триггера 72, который обеспечивает формирование эталонного числа в инверсном коде, а сигнал разрешения на формирование эталонного числа в прямом коде поступает от триггера 73 на управляющий вход блока 63. Выход блока 12 подключен к первому входу блока 13 элементов 2И-Ш1И, второй вход которого подключен к выходу компаратора 9, который осуще ствляет сравнение уровней входных и эталонных напряжений, которые заданы блоком 10 по управляющим сигна лам регистра 27. При сра1 нении равнозначных кодов поступающих на первый и второй входы блока 12, или сравнении компаратором 9 сигналов с уровнем, соответствующим з аданной норме, что является признаком отсутствия ошибки в монтаже контролируемого объекта, на первом или соответственно втором входах блока 13 будут сформированы сигналы поступающие на первые входы элементов И 88 и 89, а также через элементы НЕ 92 и 93 на входы элементов И 90 и 91, вторые входы которых стробированы импульсами соответствующих управляющих сигналов, поступающих с третьего выхода блока 35 н третий вкод блока 13 При совпадении на входах элементов И 88 и 89 сигналов отсутствия ошибок монтажа с сигналами опроса сравнения кодов или сравнения напряжений, на их выходе будет сформирован сигнал, который через элемент ИЛИ 86 поступает на второй вход элемента ИЛИ 42 и с его выхода переключает триггер 40, выключенный сигналом прерывания. Если на входах блока 12 присутствуют коды различного значения или и меряемый входной сигнал не соответствует норме, то сигналы на первом или втором входах блока 13 отсутствуют. В этом случае формируется импульс одним из элементов И 90 или 91, так как их первые входы подключены к выходу блока 12 и к выходу компаратора 9 через элементы НЕ 92 и 93, инвертирующие входной сигнал. Поэтому сформируется сигнал на выходе элемента ИЛИ 87, которьй является вторым выходом блока 13, подключенным к второму входу преобразователя 18. Преобразователь 18 осуществляет преобразование двоичного кода адрес поступающего на его третий вход с выхода формирователя Д в десятичный код, которьй с его первого выхода поступает на второй вход блока 5. По окончании преобразования на втор выходе преобразователя 18 формирует ся сигнал На переключение триггера 09 40 через элемент ИЛИ 42 для продолжения работы, прекращенной сигналом прерывания. Преобразование кода осуществляется следующим образом. Сигнал ошибки, поступающий на второй вход преобразователя 18, включает триггер 100, который разрешает прохождение первого такта Т1 через элемент И 101 и второго такта Т2 элемент И 102. По первому такту Т1 счетчики 97 и 98 устанавливаются в нулевое состояние, а по второму такту Т2 через блок -96 в счетчик 98 вводится двоичный код адреса ошибки и включается триггер 99, который дает разрешение на первые входы элементов И 103 и 104, Тактовые импульсы ТЗ через элемент И 103 поступают на счетные входы счетчиков 97 и 98. Триггер 100 первым же , импульсом такта ТЗ устанавливается в исходное положение. По тактовым импульсам ТЗ производится запись 1 в десятичньш счетчик 97 и списывание 1 из двоичного счетчика 98. После обнуления счетчика 98 в счетчике 97 будет записано число в десятичном коде, соответствующее двоичному числу, записанному первоначально в счетчик 98. По сигналу обнуления счетчика 98 с приходом тактового импульса Т4 элемент И 104 формирует импульс на формирователь. 105, который дает разрешение на вывод информации из счетчика 97 через блок 95 в блок 5, выдает сигнал на второй выход преобразователя 18 для продолжения работы и через элемент 94 сбрасывает триггер 99. Продолжение работы происходит при включении триггера 40,- разрешающего прохождение тактовых импульсов через элемент И 38 на регистр 37. Проверку контролируемого объекта осуществляют подключением контактов монтажа к входу 48 устройства. По выходу 46 устройства в контролируемой блок вводится управляющее воздействие, а по выходу 47 - код адреса контролируемой точки объекта. Все контактное поле контролируемого объекта рассматривается как N-разрядное число, в котором единичньй уровень сигнала будет только в разряде, представленном замкнутой группой контактов. Эталонный код числа поступает на второй вход блока 12 1711 из формирователя 14. Последовательиым изменением кода адреса в устройстве на выходе 47 и сменой управляющих сигналов на вьосоде 46 производит,ся поочередное включение и выключение реле в контролируемом объекте. Одновременно с изменением кода адреса происходит изменение эталонного числа. При наличии ошибки в монтаже контролируемого объекта код на его выходе не будет соответствовать эталонному 98 коду, и адрес Ошибки зафиксируется в блоке 5. Таким образом, предлагаемое устройство обеспечивает проверку изделий с электрическим монтажом в автоматическом режиме по жесткой программе, обладает высокой достоверностью, позволяет производить измерения электрических параметров радиоэлементов, входящих в состав контролируемых изделий, при этом контроль состояния объекта осуществляется во включенном состоянии.

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Устройство для задания тестов | 1985 |

|

SU1290265A1 |

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Устройство для контроля электрического монтажа | 1987 |

|

SU1455347A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРИЧЕСКОГО МОНТАЖА, содержащее блок индикации, формирователь тактовых импульсов, соединенный с входами тактирования первого формирователя одиночных импульсов и блока формирователей импульсов управления, четыре информационных входа которого связаны с соответствующими выходами клавиатуры, щинами адреса соединенной с информационными входами формирователя адресных сигналов и регистра адреса, а шинами вида проверки - с информационными входами первого буферного регистра, управляющими входами формирователь адресных сигналов, регистр адреса и первый буферный регистр подключены соответственно к первому, второму и третьему выходам блока формирователей импульсов управления, четвертым выходом соединенного с первым входом первого элемента ИЛИ узла формирования прерываний, состоящего из первого RS-триггера, второго элемента ИЛИ и первого элемента И, соединенного выходом с информационным входом первого формирователя одиночных импульсов и вторым входом элемента ИЛИ, выход которого подключен к R-входу первого триггера, 8 входом связанного с выходом второго элемента ИЛИ, который первым входом соединен с первым выходом узла анализа результата проверки, состоящего из блока элементов 2И-ИЛИ и первого блока сравнения, выход которого подключен к первому входу блока элементов 2И-ИЛИ, а первьш вход совместно с информационными входами коммутатора связан с входом устройства, второй вход первого блока сравнения соединен с вы(Л ходом формирователя эталонного числа, управляющим входом связанного с выс ходом первого буферного регистра, а информационным - с выходом формирователя адресных сигналов, являющегося выходом адреса управления устройства, 1с адресным входом коммутатора и первым входом второго блока сравнения, вторым входом соединенного с выходом DO регистра адреса, а выходом - с 00 00 первым входом первого элемента И, отличающееся тем, что, о с целью повышения достоверности ре-, зультатов контроля, в устройство введены узел измерения, состоящий из блока усилителей, компаратора и блока эталонных напряжений, преобразователь кода, узел формирования сигналов вида проверки, состоящий из третьего и четвертого элементов ИЛИ, формирователя импульсов сдвига, сдвигового регистра формирования вида проверки и первого блока элементов И,

Фе/г.

Фиг. 5

Фиг.7

Фиг.6

Фиг, 6

Фиг.9

Фиг. Ю

TJJ

/ч

74

.г

Фиг.П

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля монтажных соединений | 1975 |

|

SU598026A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Интегральная электроника в измерительных приборах | |||

| Л., Энергия, 1974, с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU105A1 |

| Способ окисления боковых цепей ароматических углеводородов и их производных в кислоты и альдегиды | 1921 |

|

SU58A1 |

Авторы

Даты

1985-02-07—Публикация

1983-07-21—Подача