Изобретение относится к автоматике и может быть использовано для управления шаговыми двигателями исполнительных устройств автоматизированной системы управления.

Известен коммутатор для управления шаговым двигателем (авт. св. СССР N 1471175, кл. G 05 B 19/40, 29.08.87; Телегин В.Д., Лакизо В.И., Нидников В. В. и др. Коммутатор для управления шаговым двигателем опублик. Бюл. N 13, 07.04.84. ), содержащий тактовую шину, шину реверса, блок памяти, связанный своими выходами со входами многоканального усилителя, реверсивный двоичный счетчик, двоичный счетчик и генератор импульсов. Разрешающий вход генератора импульсов соединен со входом установки нуля двоичного счетчика и с тактовой шиной. Выход генератора импульсов соединен с тактовым входом двоичного счетчика, выход которого подключен к тактовому входу реверсивного двоичного счетчика. Коммутатор содержит также первый и второй элементы ИЛИ, шины управления и выбора коэффициента пересчета, соединенные соответственно со входами разрешения счета и задания модуля счета реверсивного двоичного счетчика, первую, вторую и третью шины выбора режима коммутации и шину включения шагового двигателя, соединенную с разрешающим входом блока памяти. Первый и второй адресные входы блоки памяти подключены к выходам первого и второго разрядов реверсивного двоичного счетчика, третий и четвертый адресные входы соединены соответственно с выходами первого и второго элементов ИЛИ, первые входы которых соединены с выходами соответственно третьего и четвертого разрядов реверсивного двоичного счетчика, вторые входы подключены соответственно к первой и второй шинам выбора режима коммутации, а третья шина выбора режима коммутации соединена с пятым адресным входом блока памяти.

Недостатком известного коммутатора является недостаточная точность позиционирования, обусловленная отсутствием дробления шага.

Известен коммутатор для управления шаговым двигателем (авт. св. СССР N 1709271, кл. G 05 B 19/40, 16.02.90, Еременко В.Д. Коммутатор для управления шаговым двигателем, Бюл. N 14 опублик. 30.01.92.) - прототип и содержит генератор импульсов, двоичный счетчик и двоичный реверсивный счетчик, блок памяти, первый и второй элементы ИЛИ, многоканальный выходной усилитель, тактовую шину, шины управления, выбора коэффициента пересчета (сброса), реверса, шины выбора режимов коммутации, шину включения шагового двигателя, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, RS-триггер и одновибратор. Выходы блока памяти соединены со входами многоканального усилителя. Разрешающий вход генератора импульсов соединен со входом установки нуля двоичного счетчика и с тактовой шиной, выход - с тактовым входом двоичного счетчика, выход которого подключен к тактовому входу реверсивного двоичного счетчика. Шины управления и выбора коэффициента пересчета соединены соответственно со входами разрешения счета и задания модуля счета (сброса) реверсивного двоичного счетчика. Шины включения шагового двигателя соединены с разрешающим входом блока памяти. Первый и второй адресные входы блока памяти подключены к выходам первого и второго разрядов реверсивного двоичного счетчика, третий и четвертый адресные входы соединены соответственно с выходами первого и второго элементов ИЛИ, первые входы которых соединены с выходами соответственно третьего и четвертого разрядов реверсивного двоичного счетчика, вторые входы подключены соответственно к первой и второй шинам выбора режима коммутации, а третья шина выбора режима коммутации соединена с пятым адресным входом блока памяти. Вход одновибратора соединен с тактовым входом двоичного реверсивного счетчика, а инверсный выход с S-входом RS-триггера, R-выход, которого соединен с тактовой шиной устройства и первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом RS-триггера, а выход соединен с разрешающим входом генератора импульсов.

Недостатком данного коммутатора является недостаточная точность позиционирования, обусловленная отсутствием дробления шага.

Задачей технического решения является создание коммутатора для управления шаговым двигателем с повышенной точностью позиционирования.

Технический результат, заключающийся в повышении точности позиционирования, достигается тем, что коммутатор для управления шаговым двигателем, содержащий генератор импульсов, первый двоечный реверсионный счетчик, входа реверса и сброса которого соединены соответственно с входами реверса и сброса коммутатора, выхода первого и второго разрядов с соответствующими адресными входами первого элемента памяти, третий, четвертый, пятый и шестой выходы которого соединены с соответствующими входами многоканального выходного усилителя, выходы которого подключены к соответствующим обмоткам шагового двигателя, снабжен вторым реверсивным двоичным счетчиком, вторым и третьим элементами памяти, двумя цифроаналоговыми преобразователями, двумя усилителями, двумя интегрирующими и RC-цепями, двумя компараторами и четырьмя логическими элементами И-НЕ, а многоканальный выходной усилитель снабжен первым и вторым дополнительными выходами, которые соединены с инвертирующими входами соответственно первого и второго компараторов и с выходами соответственно первый и второй интегрирующих RC-цепей, входы которых подключены к выходу генератора импульсов, тактовый вход коммутатора соединен с тактовыми входами двоичных реверсивных счетчиков, входы реверса, разрешения счета и сброса второго из которых соединены соответственно с входом реверса, входом разрешения счета и входом сброса коммутатора, выходы первого-четвертого разрядов соединены с соответствующими адресными входами второго и третьего элементов памяти, а выход переполнения - с входом разрешения счета первого двоичного реверсивного счетчика, выход первого разряда которого соединен с пятыми адресными входами второго и третьего элементов памяти, выходы третьего и четвертого разрядов - с соответствующими адресными входами первого элемента памяти, разрешающей вход которого соединен с его пятым адресным входом, разрешающими входами второго и третьего элементов памяти и общей шиной, а первый, второй, седьмой и восьмой выходы соединены с первыми входами соответственно первого, второго, третьего и четвертого логических элементов И-НЕ, выходы которых соединены соответственно с первым, вторым, седьмым и восьмым входами многоканального выходного усилителя мощности, первый-шестой выходы второго и третьего элементов памяти соединены соответственно с первым-шестым входами соответственно первого и второго цифроаналоговых преобразователей, первый и второй выходы которых соединены с соответствующими входами соответственно первого и второго усилителей, выходы которых соединены с неинвертирующими входами соответственно первого и второго компараторов, выход первого из которых соединен со вторыми входами первого и второго логических элементов И-НЕ, выход второго компаратора соединен со вторыми входами третьего и четвертого логических элементов И-НЕ.

Указанная совокупность признаков позволяет повысить точность позиционирования за счет введения электрического дробления шага при работе шагового двигателя (ШД).

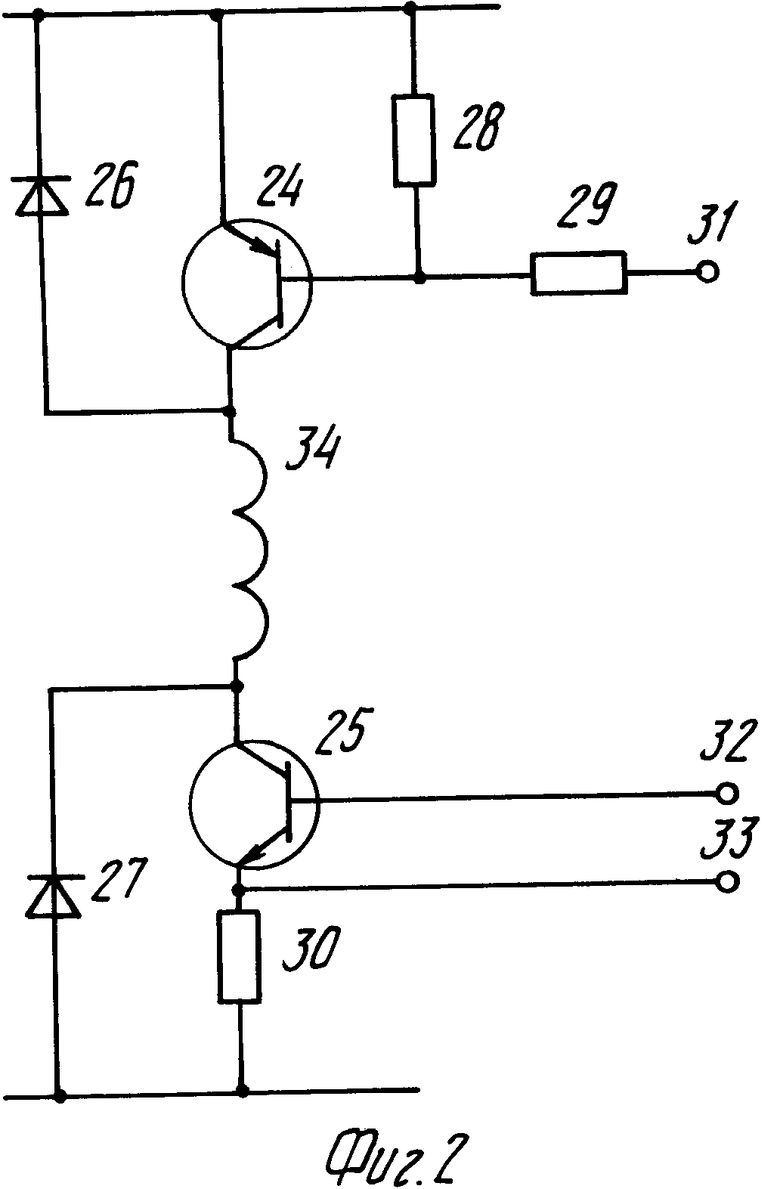

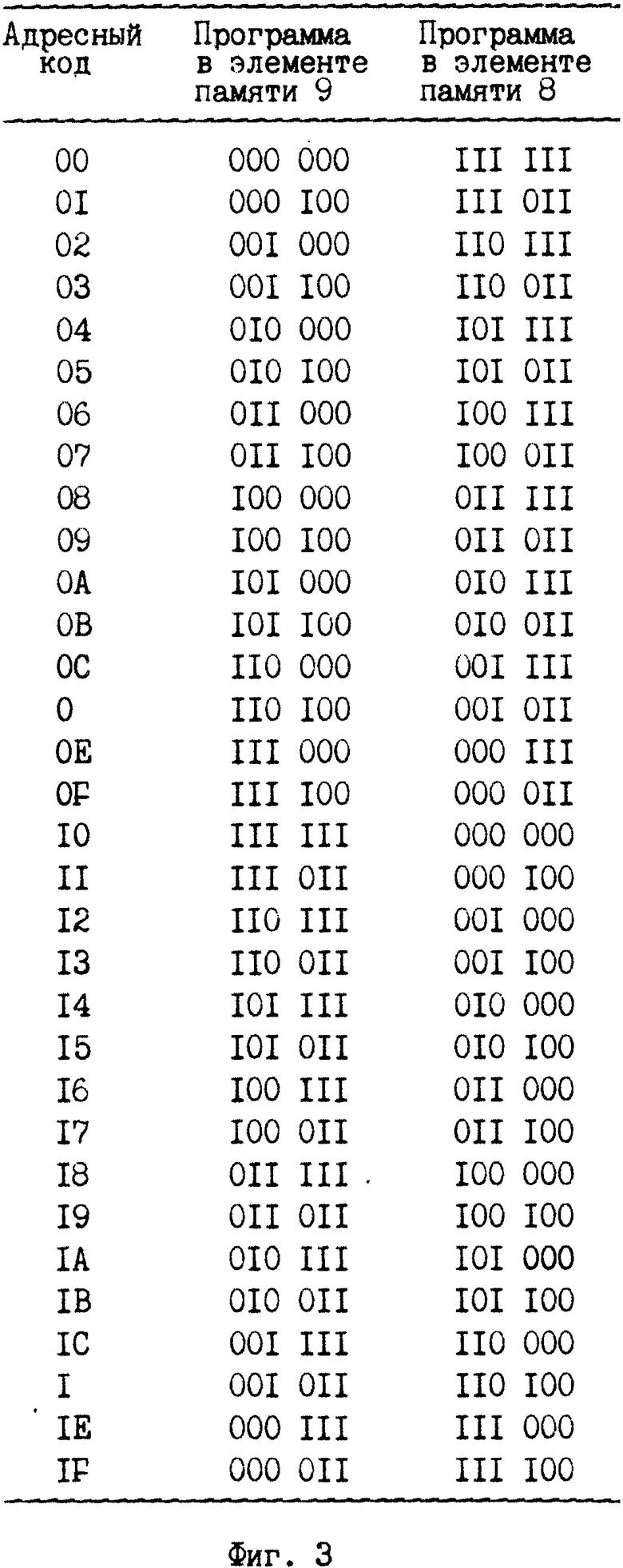

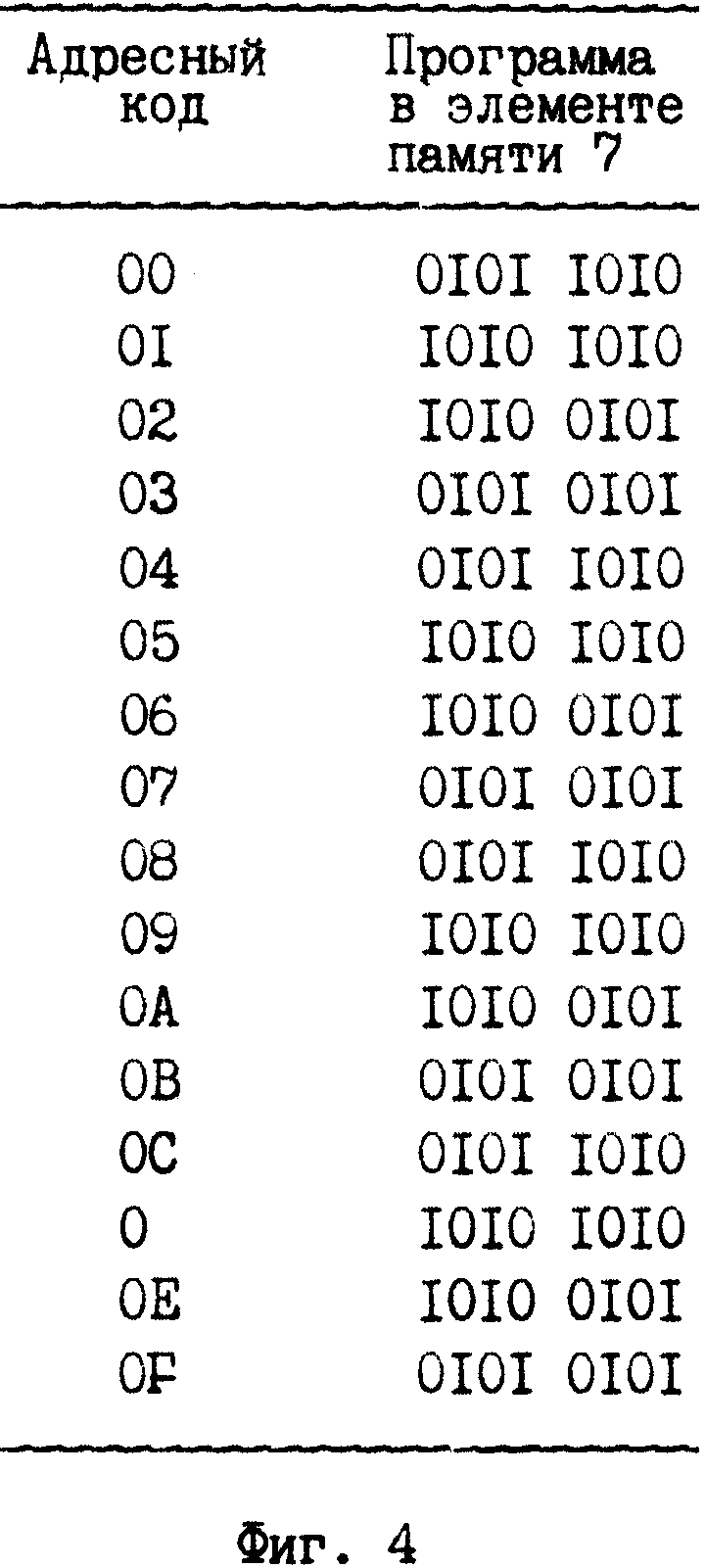

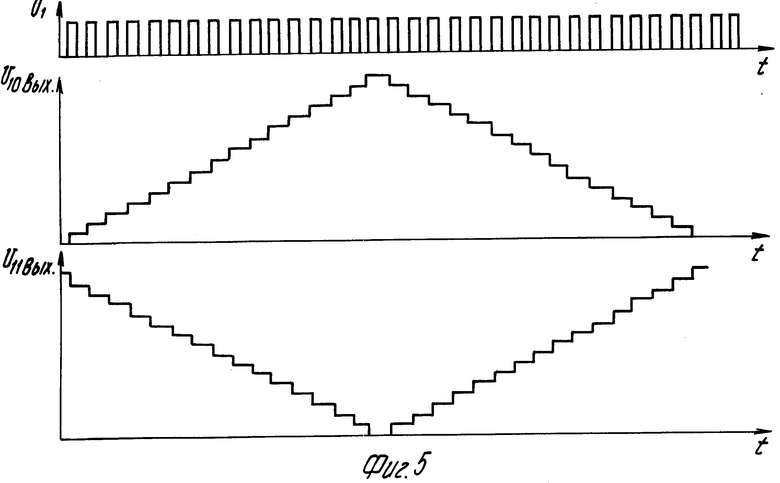

На фиг. 1 показана схема коммутатора для управления ШД; на фиг. 2 - электрическая принципиальная схема одного из каналов многоканального усилителя; на фиг. 3 и 4 - таблицы вариантов программирования элементов памяти; на фиг. 5 - эпюры выходных напряжений цифроналоговых преобразователей (ЦАП); на фиг. 6 - эпюры формирования фронтов выходных импульсов компараторов; на фиг. 7 - эпюры входных сигналов многоканального усилителя мощности; на фиг. 8 - эпюры сигналов на дополнительных выходах многоканального усилителя мощности; на фиг. 9 - эпюры сигналов на выходе RC-цепей и их суммирование с сигналами дополнительных выходов многоканального усилителя мощности.

Коммутатор для управления шаговым двигателем содержит (фиг. 1) тактовый вход 1, вход 2 реверса, вход 3 разрешения счета, вход 4 сброса, первый 5 и второй 6 двоичные реверсивные счетчики, первый 7, второй 8 и третий 9 элементы памяти, первый 10 и второй 11 цифроаналоговые преобразователи, генератор 12, первый 13 и второй 14 усилители, первую 15 и вторую 16 интегрирующие RC-цепи, первый 17 и второй 18 компараторы напряжения, первый 19, второй 20, третий 21 и четвертый 22 логические элементы 2И-НЕ, многоканальный выходной усилитель 23 мощности.

Тактовый вход 1 соединен с первыми входами первого 5 и второго 6 счетчиков, вторые и четвертые входы, которых соединены соответственно с входом 2 реверса и входом 4 сброса. Вход 3 разрешения счета соединен с третьим входом счетчика 6, пятый выход которого соединен с третьим входом счетчика 5, а первый, второй, третий и четвертый выходы соединены соответственно с первыми, вторыми, третьими и четвертыми входами второго 8 и третьего 9 элементов памяти. Первый выход счетчика 5 соединен с первым входом первого 7 и пятыми входами второго 8 и третьего 9 элементов памяти. Второй, третий и четвертый выходы счетчика 5 соединены соответственно со вторым, третьим и четвертым входами элемента 7 памяти. Первые, вторые, третьи, четвертые, пятые и шестые выходы второго 8 и третьего 9 элементов памяти соединены с первыми, вторыми, третьими, четвертыми, пятыми и шестыми входами соответственно первого 10 и второго 11 цифроаналоговых преобразователей. Первый и второй выходы цифроаналогового преобразователя 10 соединены с первым и вторым входами усилителя 13, выход которого соединен со вторым входом компаратора 17 напряжения. Первый и второй выходы цифроаналогового преобразователя 11 соединены с первым и вторым входами усилителя 14, выход которого соединен со вторым входом компаратора 18 напряжения. Выход генератора 12 соединен со входами первой 15 и второй 16 RC-цепей. Выход RC-цепи 15 соединен с первым входом компаратора 17 и первым дополнительным выходом многоканального усилителя 23. Выход RC-цепи 16 соединен с первым входом компаратора 18 и вторым дополнительным выходом многоканального усилителя 23. Выход компаратора 17 соединен с первыми входами первого 19 и второго 20 элементов 2И-НЕ, выходы которых соединены соответственно с седьмым и восьмым входами многоканального усилителя 23. Первый и второй выходы элемента 7 памяти соединены со вторыми входами соответственно первого 19 и второго 20 элементов 2И-НЕ, седьмой и восьмой выходы элемента 7 памяти соединены со вторыми входами соответственно третьего 21 и четвертого 22 элементов 2И-НЕ. Третий, четвертый, пятый и шестой выходы элемента 7 памяти соединены соответственно с третьим, четвертым, пятым и шестым входами многоканального усилителя 23.

Многоканальный усилитель 23 содержит четыре одинаковых двухвходовых транзисторных усилителя, каждый из которых состоит из (фиг. 2) транзисторов 24, 25, диодов 26, 27, резисторов 29, 28, 30, двух входов 31, 32 и выхода 33. Эмиттер транзистора 24, катод диода 26 и первый вывод резистора 28 соединены с шиной питания, второй вывод резистора 28 соединен с базой транзистора 24 и первым выводом, резистора 29. Анод диода 26 соединен с коллектором транзистора 24 и первым выводом обмотки 34 шагового двигателя. Второй вывод обмотки 34 шагового двигателя соединен с коллектором транзистора 25 и катодом диода 27. Эмиттер транзистора 25 соединен с первым выводом резистора 30 и выходом 33. Анод диода 27 и второй вывод резистора 30 соединены общей шиной. Второй вывод резистора 29 соединен с первым входом 31, а база транзистора 25 соединена со вторым входом 32 двухвходового усилителя. Входы 31 первого, второго третьего и четвертого двухвходовых усилителей являются соответственно первым, вторым, седьмым и восьмым входами усилителя 23, входы 32 - соответственно третьим, четвертым, пятым и шестым входами усилителя 23. Выходами двухвходовых усилителей служат коллекторы транзисторов 24, 25 к которым подключается фаза (обмотка) 34 шагового двигателя. Выходы 33 двухвходовых усилителей соединены с плюсовыми выводами диодов, минусовые выводы которых попарно соединены, образуя два дополнительных выхода усилителя 23 и через резисторы (на фиг. 1 не показаны) соединены с инвертирующими входами компараторов 17, 18. Поэтому многоканальный усилитель 23 имеет 8 входов и 10 выходов.

Коммутатор для управления шаговым двигателем работает следующим образом. На вход 3 разрешения счета и вход 4 сброса подаются низкие уровни напряжения (лог 0. На вход 2 реверса коммутатора подается потенциальный сигнал (лог 0 или лог 1), соответствующий порядку счета. Тактовые импульсы, поступающие на вход 1 коммутатора, после подачи управляющих сигналов на входы 2, 3, 4 принимаются на первые входы реверсивных двоичных счетчиков 5 и 6. Счетчик 6 отсчитывает поступающие на его тактовый вход импульсы, при этом записываемое в счетчик 6 двоичное число с каждым тактовым импульсом увеличивается или уменьшается на единицу в зависимости от уровня сигнала на входе 2 реверса коммутатора. Счет возрастает, пока на втором входе счетчика 6 имеется высокий уровень сигнала (лог 1). Если на второй вход счетчика 6 подается низкий уровень сигнала (лог 0), то содержимое счетчика 6 уменьшается. При наполнении счетчика 6 до максимального значения во время возрастания счета и при уменьшении содержимого счетчика 6 до нуля при убывании счета, на его пятом выходе появляется напряжение низкого активного уровни, которое, поступая на третий вход счетчика 5, будет разрешением счета этому счетчику и следующий тактовый импульс, поступающий на первые входы счетчиков 5 и 6 будет отсчитываться обоими счетчиками. Это происходит при каждом шестнадцатом тактовом импульсе. В процессе счета меняются уровни сигналов на выходах счетчиков 5 и 6. В зависимости от сочетания этих логических уровней на адресных входах элементов 7, 8, 9 памяти формируются двоичные коды, обеспечивающие считывание записанной там информации, причем каждому адресному коду на входе соответствует двоичный код на выходах элементов 7, 8, 9 памяти (фиг. 3, 4). Из схемы, приведенной на фиг. 1, видно, что считывание информации из элементов 8, 9 памяти производится со скоростью счетчика 6, а считывание информации из элемента 7 памяти производится со скоростью счета счетчика 5. В элементах 8 и 9 памяти записаны программы электрического дробления шага, а в элементе 7 памяти записана программа коммутации обмоток шагового двигателя (на фиг. 1 не показано). Из программы, приведенной в таблице на фиг. 3, видно, что двоичные коды, записаны в элементе 9 памяти, при возрастании адресного кода от нуля до пятнадцати (OF), равномерно возрастают от нуля до максимального значения, а при следующих шестнадцати тактах равномерно убывают от максимального значения до нуля. Двоичные коды, записанные в элементе 8 памяти, при возрастании адресного кода от нуля до пятнадцати равномерно убывают от максимального значения до нуля, а при следующих шестнадцати тактах равномерно возрастают от нуля до максимального значения. Считываемая из блоков 8, 9 памяти информация, поступает на цифровые входы цифроаналоговых преобразователей 10, 11 в виде двоичных кодов. В соответствии с принципом работы цифроаналогового преобразователя каждому двоичному коду на его цифровых входах соответствует определенное напряжение (Uвых) на выходах один и два. Изменение двоичного кода на цифровых входах цифроаналоговых преобразователей 10, 11 приводит к изменению их выходного напряжения. Поскольку входные цифровые коды изменяются ступенчато и равномерно (фиг. 3), то на первом и втором выходах цифроаналоговых преобразователей 10, 11 образуются сигналы ступенчатой формы, которые показаны на эпюре фиг. 5. Ступенчатые сигналы на выходах цифроаналоговых преобразователей соответствуют программам, записанным в элементах 8, 9 памяти. С выходов цифроаналоговых преобразователей 10, 11 ступенчатые сигналы поступают на первые и вторые входы усилителей 13, 14. Усилители 13, 14 усиливают по амплитуде эти ступенчатые сигналы, не меняя их формы. С выходов усилителей 13, 14 ступенчатые аналоговые сигналы поступают на неинвертирующие входы компараторов 17, 18 напряжения.

На входы интегрирующих RC-цепей 15, 16 поступают прямоугольные импульсы с генератора 12. Постоянная времени RC-цепей 15, 16 больше длительности импульса генератора 12, поэтому такой RC-цепи свойственно приблизительно линейное увеличение выходного напряжения при воздействии на вход прямоугольного импульса и такое же линейное уменьшение после прекращения импульса. Частота генератора 12 прямоугольных импульсов на два порядка выше частоты тактовых импульсов на входе 1 коммутатора, поэтому на каждую ступеньку аналогового ступенчатого сигнала на неинвертирующих входах компараторов 17, 18 приходится по несколько импульсов с RC-цепей 15, 16 на инвертирующих входах. Форма входных сигналов RC-цепей 15, 16 представлена на эпюре фиг. 9. На инвертирующие входы компараторов 17, 18 поступают также электрические сигналы с дополнительных выходов усилителя 23, форма которых представлена на эпюре фиг. 8, а процесс формирования описан ниже. В результате на инвертирующих входах компараторов 17, 18 происходит электрическое суммирование этих сигналов с сигналами с выхода RC-цепей 15, 16. Электрическое суммирование происходит во время длительности одной ступеньки сигнала с дополнительного выхода усилителя 23 и показана на эпюре фиг. 9. В результате сравнения входных сигналов компараторов 17, 18 на выходах их образуются прямоугольные импульсы, фронты которых формируются в момент равенства сигналов на входах компараторов. На эпюре фиг. 6 показано формирование фронтов прямоугольных импульсов на выходах компараторов 17, 18 для трех ступенек (уровней) ступенчатого сигнала с выхода усилителей 13, 14. На эпюре фиг. 6 видно, что скважность прямоугольных импульсов на выходах компараторов 17, 18 меняется. Это изменение происходит ступенчато, равномерно, в соответствии с программой, записанной в элементах 10, 11 памяти.

С выхода компаратора 17 прямоугольные импульсы поступают на первые входы логических элементов 19, 20 на вторые входы которых соответственно поданы сигналы с первого и второго выходов элемента 7 памяти и при разрешающих логических уровнях (лог 1) сигналов на этих входах прямоугольные импульсы проходят на выход логических элементов 19, 20, откуда поступают на первый и второй вход усилителя 23 мощности.

С выхода компаратора 16 прямоугольные импульсы поступают на первые входы логических элементов 21, 22, на вторые входы которых соответственно поданы сигналы с седьмого и восьмого выходов элемента 7 памяти и при разрешающих логических уровнях (лог 1) сигналов на этих входах прямоугольные импульсы проходят на выход логических элементов 21, 22, откуда поступают на седьмой и восьмой входы многоканального усилителя 23 мощности. Таким образом, на первый, второй, седьмой и восьмой входы многоканального усилителя 23 мощности поступают прямоугольные импульсы с изменяющейся скважностью, а на третий, четвертый, пятый и шестой входы - логические уровни, управляющие включением обмоток шагового двигателя с третьего, четвертого, пятого и шестого выходов элемента 7 памяти.

Многоканальный усилитель 23 мощности содержит четыре одинаковых двухвходовых усилителя, принципиальная электрическая схема одного из которых приведена на фиг. 2. Выходами двухвходовых усилителей служат коллекторы транзисторов 24, 25, к которым подключается фаза (обмотка) 34 шагового двигателя. Выходы 33 двухвходовых усилителей соединены с плюсовыми выводами диодов, минусовые выводы которых попарно соединены, образуя два дополнительных выхода усилителя 23 и через резисторы (на фиг. 1 не показаны) соединены с инвертирующими входами компараторов 17, 18.

Сигналы на дополнительных выходах усилителя 23 имеют форму, приведенную на эпюре фиг. 8 и формируются следующим образом. Транзисторы 24, 25 двухвходового усилителя (см. фиг. 2) работают в ключевом режиме. Когда на третий вход усилителя 23 (вход 32 фиг. 2) с третьего выхода элемента 7 памяти поступает прямоугольный импульс, открывающий транзистор 25, на первый вход усилителя 23 (вход 31 фиг. 2) поступает пачка прямоугольных импульсов с выхода первого 19 логического элемента 2И-НЕ, причем длительность пачки импульсов на входе 31 равна длительности импульса на входе 32 и совпадает с ним по времени (см. программы фиг.3, 4). Эпюры сигналов на входах 31, 32 приведены на фиг. 7. Импульсы в пачке на входе 31 сформированы компаратором 17, как показано на эпюре фиг. 6 и через логический элемент 19 2И-НЕ поступают на вход 31. Скважность импульсов в пачке изменяется ступенчато и равномерно. Это происходит в момент смены двоичных кодов на цифровых входах цифроаналогового преобразователя 10 в процессе выполнения программы в элементе 9 памяти. Ступенчатое и равномерное изменение скважности импульсов в пачке на входе 31 так же ступенчато и равномерно изменяет ток в фазе (обмотке) 34 шагового двигателя. Поэтому сигналы, формируемые на выходе 33 (фиг. 2) двухвходового усилителя и, следовательно, на дополнительном выходе усилителя 23 имеют ступенчатую форму.

Сигналы с дополнительных выходов усилителя 23 (фиг. 1) через резисторы (на фиг. 1 не показаны) поступают на инвертирующие входы компараторов 17, 18. Во время длительности одной ступеньки ступенчатого сигнала это оказывает стабилизирующее действие на ток в фазе шагового двигателя (ШД), что повышает точность позиционирования коммутатора.

Сигналы на дополнительные выходы усилителя 23 мощности поступают с выходов 33 двухвходовых усилителей (фиг. 2). Поэтому форма напряжения на дополнительных выходах усилителя 23 и форма тока в обмотках ШД совпадают. Ток в обмотках ШД изменяется ступенчато и равномерно, что приводит к ступенчатому и равномерному изменению соотношению токов в обмотках (фазах) ШД, т.е. электрическому дроблению шага. Коэффициент дробления равен 16. Двоичные коды, записанные в элементах 8, 9 памяти, возрастают и убывают равномерно в процессе считывания, соответствующие им уровни аналоговых сигналов на выходах цифроаналоговых преобразователей 10, 11 (фиг. 1) тоже изменяются ступенчато и равномерно, поэтому изменение скважности прямоугольных импульсов на выходах компараторов 17, 18 и соответствующее этому изменение соотношения токов в обмотках ШД производится ступенчато и равномерно. Этим достигается равномерное электрическое дробление шага ШД и высокая точность позиционирования.

Коммутатор для управления шаговым двигателем может использоваться в области автоматики, в частности в точных исполнительных механизмах с линейным шаговым приводом при компьютерном управлении.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММНЫЙ ТАЙМЕР | 2001 |

|

RU2215367C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ПАРАМЕТРОВ | 1999 |

|

RU2180450C2 |

| ЯЧЕЙКА ПАМЯТИ | 2002 |

|

RU2222100C2 |

| ЯЧЕЙКА ПАМЯТИ | 2001 |

|

RU2214037C2 |

| ТАЙМЕР | 2001 |

|

RU2199177C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМИ ЗАМКАМИ | 2001 |

|

RU2198276C1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 2001 |

|

RU2207717C2 |

Изобретение относится к автоматике. Достигаемый технический результат - повышение точности позиционирования. Коммутатор содержит тактовый вход 1, вход 2 реверса, вход 3 разрешения счета, вход 4 сброса, двоичные реверсивные счетчики 5, 6, элементы 7, 8, 9 памяти, цифроаналоговые преобразователи 10, 11, генератор 12 импульсов, усилители 13, 14, интегрирующие RC - цепи 15, 16, компараторы 17, 18 напряжения, элементы 19, 20, 21, 22, 2И-НЕ, многоканальный усилитель 23. 9 ил.

Коммутатор для управления шаговым двигателем, содержащий генератор импульсов, первый двоичный реверсивный счетчик, входы реверса и сброса которого соединены соответственно с входами реверса и сброса коммутатора, выходы первого и второго разрядов с соответствующими адресными входами первого элемента памяти, третий, четвертый, пятый и шестой выходы которого соединены с соответствующими входами многоканального выходного усилителя, выходы которого подключены к соответствующим обмоткам шагового двигателя, отличающийся тем, что он содержит второй реверсивный двоичный счетчик, второй и третий элементы памяти, два цифроаналоговых преобразователя, два усилителя, две интегрирующие RC-цепи, два компаратора и четыре логических элемента И - НЕ, а многоканальный выходной усилитель снабжен первым и вторым дополнительными выходами, которые соединены с инвертирующими входами соответственно первого и второго интегрирующих RC-цепей, входы которых подключены к выходу генератора импульсов, тактовый вход коммутатора соединен с тактовыми входами двоичных реверсивных счетчиков, входы реверса, разрешения счета и сброса второго из которых соединены соответственно с входом реверса, входом разрешения счета и входом сброса коммутатора, выходы первого - четвертого разрядов соединены с соответствующими адресными входами второго и третьего элементов памяти, а выход переполнения с входом разрешения счета первого двоичного реверсивного счетчика, выход первого разряда которого соединен с пятыми адресными входами второго и третьего элементов памяти, выходы третьего и четвертого разрядов с соответствующими адресными входами первого элемента памяти, разрешающий вход которого соединен с его пятым адресным входом, разрешающими входами второго и третьего элементов памяти и общей шиной, а первый, второй, седьмой и восьмой выходы соединены с первыми входами соответственно первого, второго, третьего и четвертого логических элементов И НЕ, выходы которых соединены соответственно с первым, вторым, седьмым и восьмым входами многоканального выходного усилителя мощности, первый шестой выходы второго и третьего элементов памяти соединены соответственно с первым шестым входами соответственно первого и второго цифроаналоговых преобразователей, первый и второй выходы которых соединены с соответствующими входами соответственно первого и второго усилителей, выходы которых соединены с неинвертирующими входами соответственно первого и второго компараторов, выход первого из которых соединен с вторыми входами первого и второго логических элементов И НЕ, выход второго компаратора соединен с вторыми входами третьего и четвертого логических элементов И НЕ.

| SU, авторское свидетельство, 1471175, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| SU, авторское свидетельство, 1709271, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1998-01-27—Публикация

1995-06-29—Подача