(54) МУЛЬТИПЛЕКСНЫЙ КАНАЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультиплексный канал | 1977 |

|

SU750469A1 |

| Мультиплексный канал | 1973 |

|

SU525079A1 |

| Блок-мультиплексный канал | 1977 |

|

SU691841A1 |

| Мультиплексный канал | 1975 |

|

SU561955A1 |

| Мультиплексный канал | 1979 |

|

SU860044A2 |

| Мультиплексный канал с диагностикой неисправностей | 1974 |

|

SU516033A1 |

| Мультиплексный канал | 1974 |

|

SU525941A1 |

| Мультиплексный канал многопроцессорной вычислительной системы | 1973 |

|

SU521559A1 |

| Мультиплексный канал | 1978 |

|

SU750473A1 |

| Мультиплексный канал | 1978 |

|

SU752318A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах для ввода-вывода информации.

Известны мультиплексные каналы для обмена данными между оперативным запоминающим устройством цифровой вычислительной машины к устройствами ввода-вывода, содержащее блоки сопряжения с центральным процессором, оперативной памятью и внешними устройствами, регистры подканала, управления и информации, блоки модификации адресов, блок местной памяти и блок контроля интерфейса 1.

Недостаток этих каналов состоит в больших аппаратурных затратах.

Наиболее близким к данному изобретению по технической сущности является мультиплексный канал,, содержащий блок сопряжения с процессором, выход которого соединен с первым входом регистра управления, второй вход которого соединен с первым входом регистра информации и выходом блока сопряжения d внешними устройствами, вход которого соединен с первым и третьим выходами регистра управления, первым выходом регистра информации и первыми выходами блока сопряжения с процессором и блока местной памяти, второй вход которого через блок управления обращениями соединен со вторым выходом регистра управления, третий выход которого

через блок модификации адресов и счета данных соединен с третьим входом блока местной памяти, и первым входом блока сопряжения с оперативной памятью, второй вход которого соединен с выходом блока местной памяти, с третьим входом регистра

управления и вторым входом регистра информации, третий вход которого соединен ,с выходом блока сопряжения с оперативной памятью и с четвертым входом регистра управления, второй выход которого соединен с третьим входом блока местной памяти 2 Недостатком этого канала являмтся значительные аппаратурные затраты. В частности, в канале местная память предназначена для хранения управляющей информации: адресного слова канала и управляющего слова канала и буферизации данных для каждого из устройства ввода-вывода, подключенного к каналу. Отказ местной па- мяти приводит к полному отказу канала. Кроме того, в случаях, когда к кааналу

подключено число внешних устройств (ВУ), меньшее максимально допустимого, значительная часть местной памяти в работе не участвует.

Цель изобретения - сокращение объема оборудования канала и повышение надежности работы.

Поставленная цель достигается тем, что в мультиплексный канал, содержаш.ий блок сопряжения с процессором, первые вход и выход которого являются соответственно первыми входом и выходом канала, а вторые вход и выход - подключены соответственно к первым выходу и входу регистра управления, вторые выход и вход которого соединены соответственно с первыми входом и выходом блока сопряжения с внешними устройствами, вторые вход и выход которого являются вторыми входом и выходом канала, а третий вход и первый выход - подключены соответственно к первым выходу и входу регистра информации, соединенного вторыми входом и выходом соответственно с первыми выходом и входом блока сопряжения с оперативной памятью, вторые вход и выход и третий выход которого являются соответственно третьими входом и выходом и четвертым выходом канала, а первые выход и вход - подключены соответственно к третьим входу и выходу регистра управления, четвертым выходом соединенного со входом блока модификации адреса и счета данных, введен блок формирования исполнительного адреса, причем вьгходы блока модификации адресов и счета данных подключены соответственно к четвертому входу регистра управления и первому входу блока формирования исполнительного адреса, второй, третий и четвертый входы и выход KOTOpofo соединены соответственно с первым входом пятым выходом и вторым входом perHeipa управления и третьим входом блока напряжения с оперативной памятью, а также тем, что блок формирования исполнительн,ого адреса содержит два элемента ИЛИ регистр базового адреса и сумматор, подключенный первым входом через регистр базового адреса ко второму входу блока, вторым входом - через первый элемент ИЛИ к третьему и четвертому входам блока, а выходом - к первому входу второго элемента ИЛИ, второй вход выход которого являются соответственно первым входом и выходом блока.

Введение блока формирования исполнительного адреса позволяет отказаться от местной памяти канала и разместить управляющую информацию в оперативной памяти процессора. Адреснйе слова канала размещаются в ячейках оперативной памяти с адресами, представляющими сумму базового адреса, поступающего в канал из процессора и номера устройства ввода-вывода. Управляющие слова канала размещаются в ячейках оперативной памяти с адресами, указанными в адресных словах, а данные размещаются в ячейках с адресами, указанными в управляющих словах.

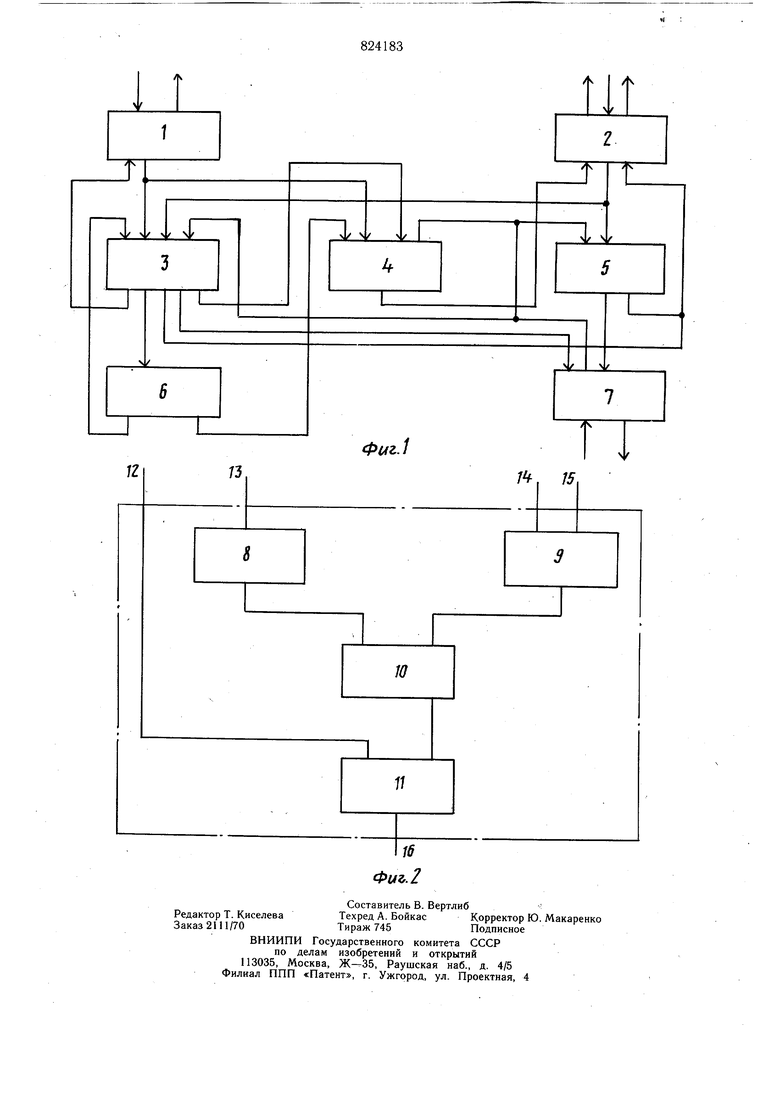

На фиг. 1 приведена блок-схема мультиплексного канала; на фиг. 2 - функциональнйя схема блока формирования исполнительного адреса.

Канал содержит блок 1 сопряжения с процессором, блок 2 сопряжения с оперативной памятью, регистр 3 управления, блок 4 формирования исполнительного адреса, регистр 5 информации, блок 6 модификации адреса и счета данных, блок 7 сопряжения с внешними устройствами.

Блок формирования исполнительь го адреса содержит регистр 8 базового адреса, первый элемент 9 ИЛИ, сумматор 10, второй элемент 11 ИЛИ, входы 12-15 и выход 16.

На вход 12 поступает адрес управляющего слова канала и адрес данных, на вход 13 базовый адрес, на входы 14 и 15 номер внешнего устройства из регистра управления и из блока сопряжения с внешними устройствами. На выходе 16 формируется исполнительный адрес.

Устройство работает следующим образом.

Базовый адрес поступает в канал при включении системы и меняется по инициативе процессора в случаях неисправности в соответствующем блоке оперативной памяти процессора.

Работа канала начинается с получения от процессора инструкции, которая приходит На блок сопряжения с процессором. Инструкция состоит из 32 разрядов (разряды 1-8 - код инструкция, разряды 17-19 - адрес канала, разряды - адрес внешнего устройства). Адрес внешнего устройства запоминается в регистре 3 управления и по адресу внешнего устройства через блок 7 производится начальная выборка внешнего устройства. Одновременно адрес внешнего устройства поступает в блок 4 формирования исполнительного адреса, где происходит суммирование адреса внешнего устройства с хранящимся там базовым адресом. По полученному адресу через блок 2 сопряжения с оперативной памятью выбирается адресное слово качала (АСК), которое содержит адрес управляющего слова канала (УСК) (разряды 1:-16). АСК. фиксируются в регистре 3. Далее по адресу, содержащемуся в АСК, через блоки 4 и 2 из оперативной памяти выбирается управляющее слово канала состоящее из 6i4 разрядов (разряды 1 -16 - счет данных, разряды 17-32 - адрес данных, 33-48 - адрес перехода, 49-56 - признаки, 57- 64 - код операции).

УСК фиксируется в регистре 3. Код операции черезблок 7 поступает во внешнее устройство и, если внещнее устройство готово выполнить операцию, начинается процедура обмена данными. По адресу данных, содержащемуся в УСК, через блок 2 из

оперативной памяти поступает информационное слово и фиксируется в регистре 5 информации. При операции «Писать, байт данных с регистра 5 через блок 7 поступает во внешнее устройство (ВУ). Одновременно блоком 6 производится модификация адреса данных и счета данных. При операции «Читать байт данных из внешнего устройства поступает через блок 7 в регистр 5, и блок 6 производит модификацию адреса и счет данных.

По окончании обмена байтом данных модифицированное УСК и АСК из регистра 3 управления, слова данных нз регистра 5 через блок 2 передаются в оперативную память. Дальнейшее обслуживание внешнего устройства по обмену данными производится по сигналу «Требование абонента, поступающему на блок 7 из внешнего устройства. По этому сигналу канал производит выборку внешнего устройства, в процессе которой из внешнего устройства на блок 4 поступает адрес выбранного ВУ. В блоке 4 адрес ВУ суммируется с хранящимся там базовым адресом и по результирующему адресу из оперативной памяти через блок 2 производится считывание соответствующего АСК. Далее процесс обмена байтом данных осуществляется в такой же последовательности, как было описано выше.

Таким образом, предлагаемое изобретеihie имеет более высокую надежность по сравнению с известными за счет исклк)чения из состава канала местной памяти, отказ которой в прототипе приводит к полному отказу канала и возможности размещения адресных слов канала в любом блоке оперативной памяти процессора.

Формула изобретения

соединены соответственно с первыми входом и выходом блока сопряжения с внешними устройствами, вторые вход и выход которого являются вторыми входом и выходом канала, а третий вход и первый выход -

5 подключены соответственно к первым выходу и входу регистра информации, соединенного вторыми входом и выходом соответственно с первыми выходом и входом блока сопряжения с оперативной памятью, вторые вход и выход и третий выход которого

o являются соответственно третьими входом и выходом и четвертым выходом канала, а первые выход и вход - подключены соответственно к третьим входу и выходу регистра управления, четвертым выходом соединенного со входом блока модификации адреса и счета данных, отличающееся тем, что, с целью сокращения объема оборудования, в канал введен блок формирования исполнительного адреса, причем выходы блока модификации адресов и счета данных

0 подключены соответственно к четвертому входу регистра управления и первому входу блока формирования исполнительного адреса, второй, третий и четвертый входы и выход которого соединены соответственно с пер- вым входом, пятым выходом и вторым входом регистра управления и третьим входом блока сопряжения с оперативной памятью. 2. Канал, отличающийся тем, что блок формирования исполнительного адреса содержит два элемента ИЛИ, регистр базового адреса и сумматор, подключенный первым входом через регистр базового адреса ко второму входу блока, вторым входом - через первый элемент ИЛИ к третьему и четвертому входам блока, а выходом - к первому входу второго элемента ИЛИ, второй вход и выход которого являются соответственно первым входом и выходом блока.

Источники информации, принятые во внимание при экспертизе

№ 525079, кл. G 06 F 3/04, 1973 (прото.тип).

И

/ / I

/3

rz

HI

/ч / vT

f(

N/

ГТ

Фиг.1

7 15

Авторы

Даты

1981-04-23—Публикация

1979-06-04—Подача