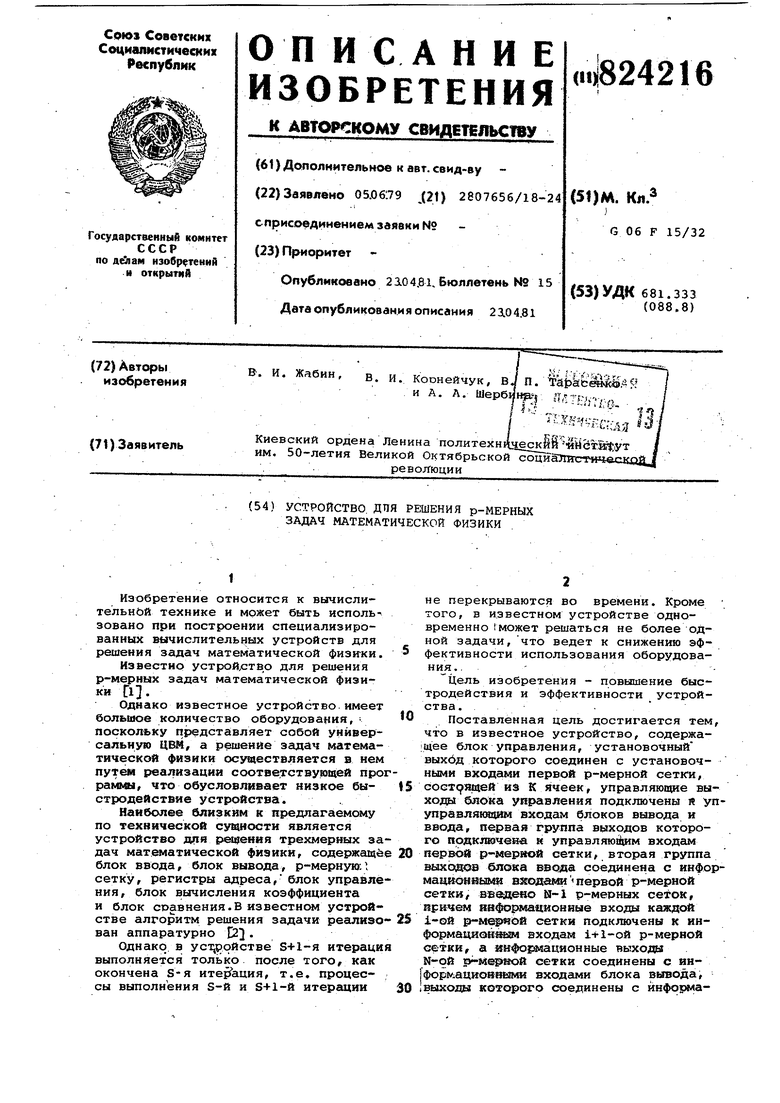

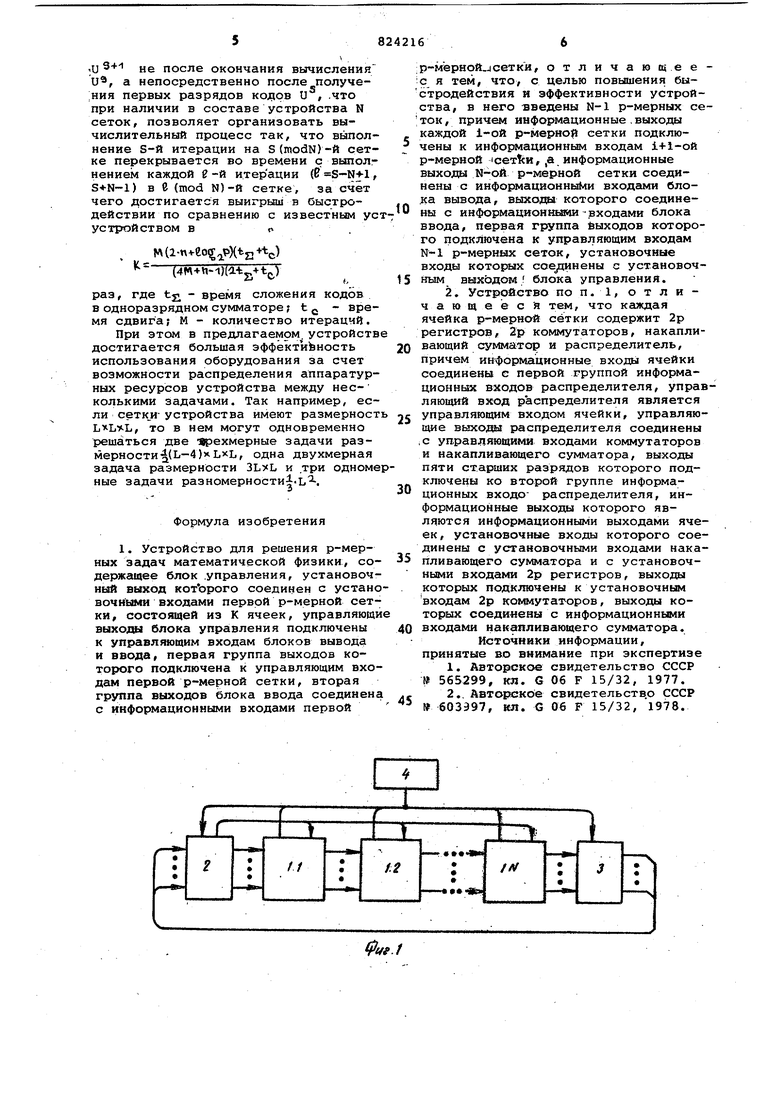

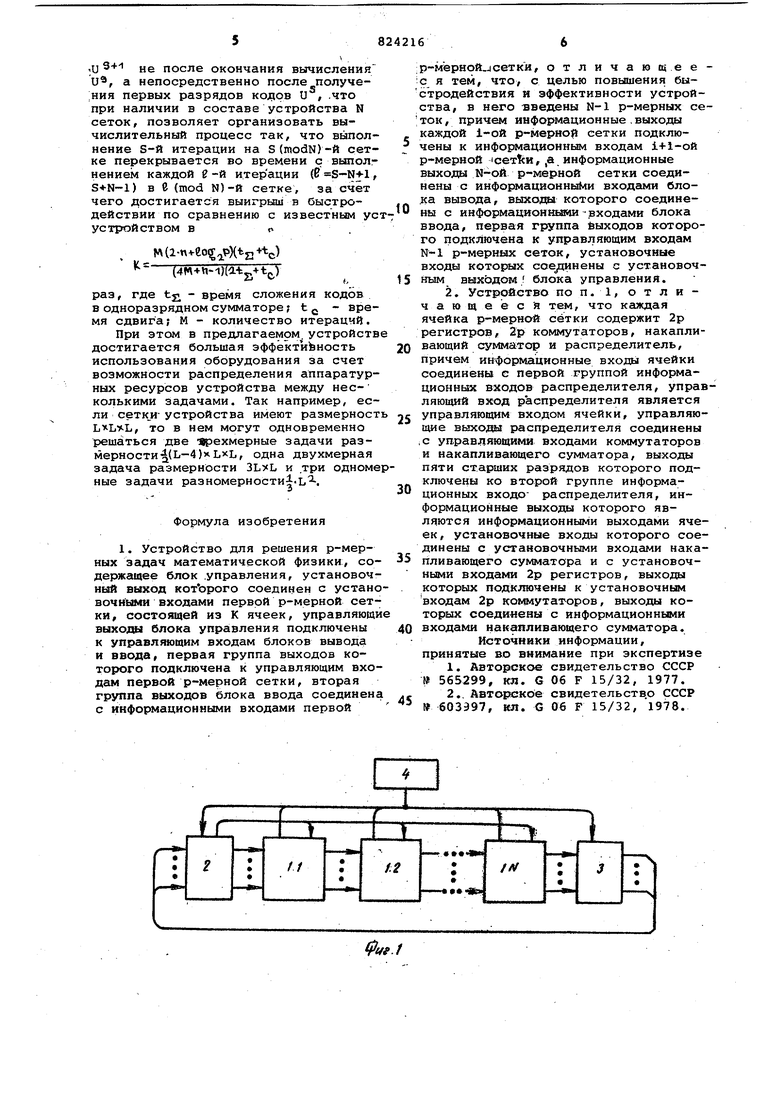

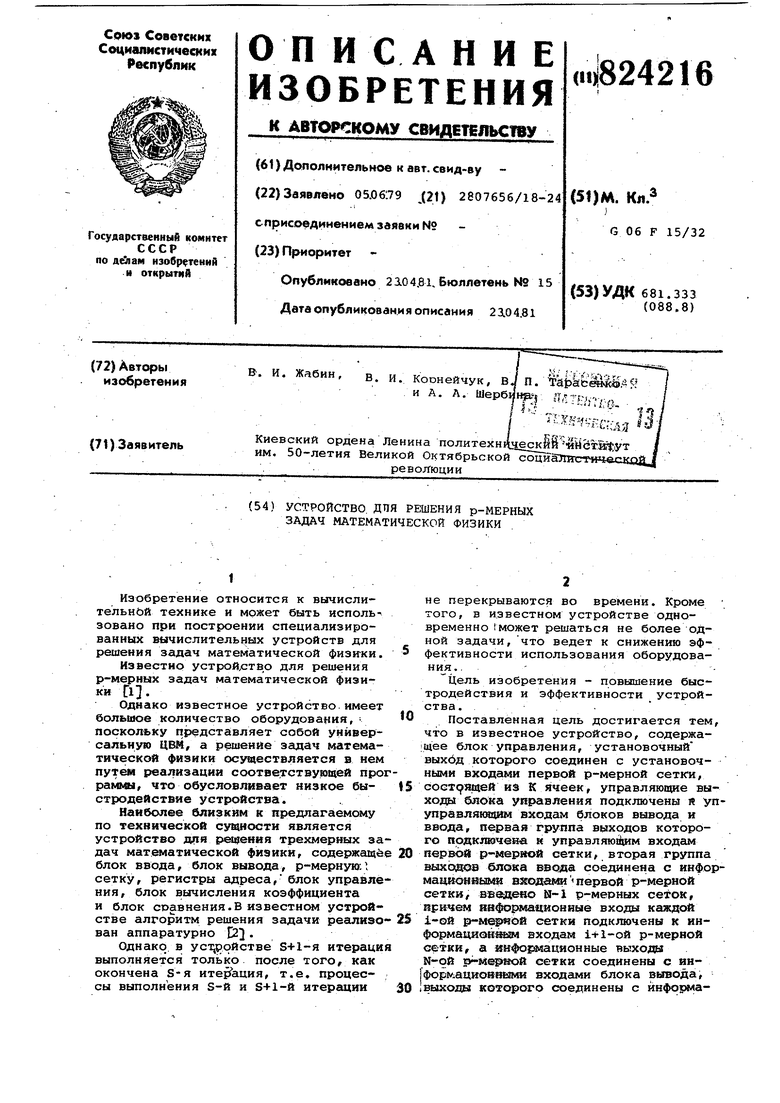

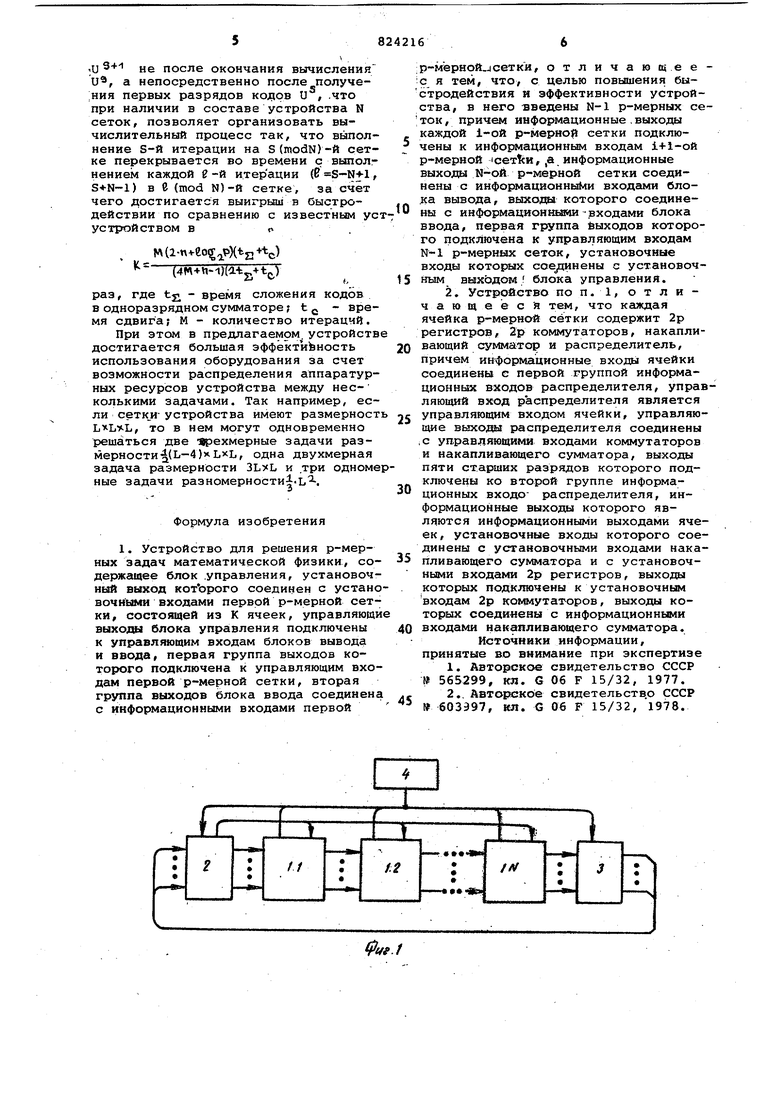

1 . Изобретение относится к вычислительнЬй технике и может быть исполь зовано при построении специализированных вычислительных устройств для решения задач математической . Известно устроаствр для решения р-мерных задач математической физики TI. Однако известное устройство имеет болыоое количество оборудования, поскольку представляет собой универсальную ЦВМ, а решение задач математической физики осуадествляется в нем путем реализаций соответствующей про рамыа, что обусловливает низкое быстродействие устройства. . Наиболее близким к предлагаемому по технической с аности является устройство для трехмерных за дач математической физики, содержаще блок ввода, блок вывода, р-мернуик. сетку, регистры адреса, блок управле ния, блок вычисления коэффициента и блок сравнения.В известном устройстве алгоритм решения задачи реалиэо ван аппаратурно D}. Однако в устройстве S-H-я итераци выполняется только после того, как окончена S-я итерация, т.е. процессы выполнения S-й и S+1-й итерации не перекрываются во времени. Кроме того, в известном устройстве одновременно 1может решаться не более одной задачи, что ведет к снижению эффективности использования оборудования. цель изобретения - повышение быстродействия и эффективности устройства. Поставленная цель достигается тем, что в известное устройство, содержащее блок управления, установочный выхбд которого соединен с установочными входами первой р-мерной сетки, сост9Я1ввй из К ячеек, управляющие выхода блока управления подключены я упуправлянн2дам входам блоков вывода и ввода, первая группа выходов которого прдктдачейа н управляющем входам первой р-«ер ой сетки, вторая группа выходов блока ввода соединена с информащйгивыми первой р-мерной сетки, BBSsaeHO N-1 р-мерных сеток, причем В8фор««а«иониые входы каждой 1-ой сетки подключены к ииформацивншет входам i+1-ой р-мерной сетки, а информационные выхода М-ой сетки соединены с ии.формациоввыми входами блока вывода, 1выхо1 которого соединены с инфо1 лациркными входами блока ввода, п«фв.я группа выходов которого подключена Г к управляющим входам N-1 р-мерных сефок, установочные 4 входы которых соединены с установочным выход Я4 бло ка управления Кроме того, каждая ячейка р-мерно сетки содержит 2р регистров, 2р коммутаторов , накапливающий сумматор и распределитель, причем информационны |вхолы ячейки соединены с первой груп пой информационныхвходов распредели теля, управлякнций вход распределителя является v;пpaвля&(им входом ячейки втравляющие вьвсоды распределителя сое динены с управлякхцит входами коммута торов и накапливающего сумматора, шл ходы пяти старших разрядов которого подключены ко второй группе информационных входов распределите ля, информационныз выходы которого являются информационными выходами ячеек, уста новоч1ше входы которого соединены с установочными входами накапливающе го сумматора и с установочными входами 2р регистров, выходы которых подключены к устаноаочнЕШ входам 2р коммутаторов, выходы кото|Я2х соедине ны с информационн1ди1и входами накапли вающего .i На фиг. i показана структурная схема устройства; на фиг. 2 - то же, ячейки; на фиг. 3 - то же, блока управления. Устройство содержит р-мерные сетки 1.1-1.N,; блок 2 ввода, блок 3 вывода и блок 4 управления. Каждая ячейка р-мерной сетки содержит регис ры 5.1-5.2р, коммутаторы б.1-6.2р, накапливакяций сумматор 7, распределитель 8. Установочные входы 9, управляющие входы 10, информационные входы 11, инфop 4aциoнныe выходам 12. Влок 4 управления содержит последовательно соединенные счетчик 13 тактов, счетчик 14 циклов, счетчик 15 сеток и счетчик 16 итераций, выходу которых подключены соответствен но ко входам дешифраторов 17-20, выходы которых являются управляющими выходами блока управления. &1ход де1Ш1фратора 20 соединен с первым вход генерахсфа 21 тактовых импульсов, выход котсчого подключен к первому входу счетчика 13 тактов. Шина 22 ус тановки исходного состояния соединена со в торгами входами генератора 21 тактовых импульсов, счетчика 13 (тактов, счетчика 14 циклов, счетчи ка 15 сеток, счетчика 16 итераций и является установочным выходом блока .4 управления. Устройство работает следующим Об-j разом. До начала вычислений в регист 5.1-5.2р записываются значения коэф фицие1 трв а, а в суммато с 7 заносятся значения правых 4acTeAT(jypaB- нения ..S gi«.u в каждом J-M цикле вычисления (,n) на информационные входы 11 кгикдой ячейки сетки 1.1 с блока 2 ввода поступают цифры операндов и , принимающие значения из множества l, О, и имеющие вес 2, где с - количество двоичных разрядов, после которых фиксируется запятая. Цифра операнда Ц , поступающая на управляющий вход коммутатора 6.1, управляет выдачей содержимого регистра 5.1 на сумматор 7 таким образом, что на сумматор 7 поступает прямой код регистра 5.1, ёсЛи цифра и равна плюс единице, дополнительный код, если цифра равна минус единице, и код регистра 5.1 не выдается, если принимаемая цифра равна нулю. Начиная с четвертого цикла,,. распределитель 8, анализируя содержимое А пятистарших разрядов сумматора 7, формирует и выдает на информационные выходы 12,5цифру числа . и , вес 2, Эта цифра равна плюс единице, если ,,нулю - если , или минус единице, если . При этом на сумматор 7 со сдвигом на три разряда влево выдается прямой код всех регистров 5, если формируемая цифра Цр равна минус единице, либо их дополнительный код, если цифра Uj равна плюс единице. В трех первых циклах цифры и равны Нулю независимо от содержимого сумматора 7. В крице каждого цикла осуществляется сдвиг содержимого сумматора 7 на один разряд влево. Цифры операндов U, формируемые в J-M цикле вычисления ячейками сетки 1.1, в j+l-M цикле поступают на вхойа 11 соответству1аадих ячеек сетки 1.2, которое формируют на выходах 12 значения стерандов О,поступающие на входа 11 ячеек сетки 1.3 и т.д. Таким образом, в каждом J-M цикле вычисления, на выхсщах сетки l.s формируются ойерандов uf имеющие вес , Если , где п - разрядность О, то значения ctapших разрядов («ерандов и формируются на выходах сетки в. тот момент, когда в сетке 1.1 вычисления уже закончены. В этом случае цифры операндов и через блок 3 вывода и блок 2 ввода непосредственно поступают на входы 11 сетки 1.1. Если .же , то в блоке 2 ввода дополнительно осуествляется задержка кодов и на n-4{N-1) одклов.до окончания вы-исления IT на сетке 1.1. в дальейшем вьтолвение каждой s-й итерации существляется на сетке l.S(modN). Таким образом, изобретение даёт , озможность приступать к вычислению;U не после окончания вычисления и, а непосредственно после получе;ния первых разрядов кодов U , .что при наличии в составе устройства N сеток, позволяет организовать вычислительный процесс так, что выполнение S-й итерации на S (modN)-и сетке перекрывается во времени с выполнением каждой е -и итерации (Р , ) в С (mod Ы)-й сетке, за счет чего достигается выигрыш в быстродействии по сравнению с известным ус устройством в ( )() (4M-«-n-lH1-tj.+ t5j) раз, где tj - время сложения кодов в одноразрядном сумматоре; t - время сдвига; М - количество итераций. При этом в предлагаемом устройств достигается большая эффективность использования оборудования за счет возможности распределения аппаратурных ресурсов устройства между несколькими задачами. Так например, если устройства имеют размерност Lf-Lf-L, то в нем могут одновременно решаться две з ехмерные задачи размерности-(L- jxLxL, одна двухмерная задача размерности и три одноме ные задачи разномерности -Ь. Формула изобретения 1. Устройство для решения р-мерных задач математической физики, со держащее блок .управления, установоч ный выход которого соединен с устан вочншви входами первой р-мерной сет ки, состоящей из К ячеек, управляющ выходы блока управления подключены к управляющим входам блоков вывода и ввода, первая группа выходов которого подключена к управляющим вхо дам первой р-мерной сетки, вторая группа выходов блока ввода соединен с информационными входами первой р-м1ерной сетки, отличающеес я тем, что, с целью повышения быстродействия и эффективности устройства, в него введены N-1 р-мерных сеток, причем информационные.выходы каждой 1-ой р-мерно й сетки подключены к информационным входам i+1-ой р-мерной , ,а информационные выходы N-оЙ р-мерной сетки соединены с информационными входами блока вывода, выходы которого соединены с информационшдаш входами блока ввода, первая группа выходов которого подключена к управляющим входам N-1 р-мерннх сеток, установочные входы которых сое/данены с установочным выходом. блока управления. 2. Устройство ПОП.1, отличаю щ е (В с я тем, что каждая ячейка р-мерной сетки содержит 2р регистров, 2р коммутаторов, накапливающий сумматор и распределитель, причем информационные входы ячейки соединены с первой группой информационных входов распределителя, управляющий вход распределителя является управляющим входом ячейки, управляющие выхода распределителя соединены ,с управляющими входами коммутаторов и накапливающего сумматора, выходы пяти старших разрядов которого подключены ко второй группе информационных входо распределителя, информационные выходы которого являются информационными выходами ячеек, установочные входы которого соединены с установочными входами накапливающего сумматора и с установочными входами 2р регистров, выходы которых подключены к установочным входам 2р коммутаторов, выходы которых соединены с информационными входами накапливающего сумматора. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 565299, кл. G Об F 15/32, 1977. 2.. Авторское свидетельству СССР №603997, кл. G Об F 15/32, 1978.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1337904A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1166103A1 |

| Устройство для вычисления преобразования Фурье-Галуа | 1989 |

|

SU1665385A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Вычислительный узел для однородной вычислительной системы | 1979 |

|

SU982008A1 |

| Устройство для вычисления преобразования Уолша (его варианты) | 1982 |

|

SU1075269A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

9

IviID

/

tf

12

fO

фаг 2

Авторы

Даты

1981-04-23—Публикация

1979-06-05—Подача