и вторым информационйым входом первого коммутатора, первый управляющий вход четвертого коммутатора соединен с пятым выходом блока управления, седьмой выход которого соединен.с вторыми управляющими входами второго и четвертого коммутаторов, установочные, входы с первого по четвертый регистров соединены соответственно с первого по четвертый входами задания начальных условий устройства, вход запуска блока управления соединен с входом запуска устройства.

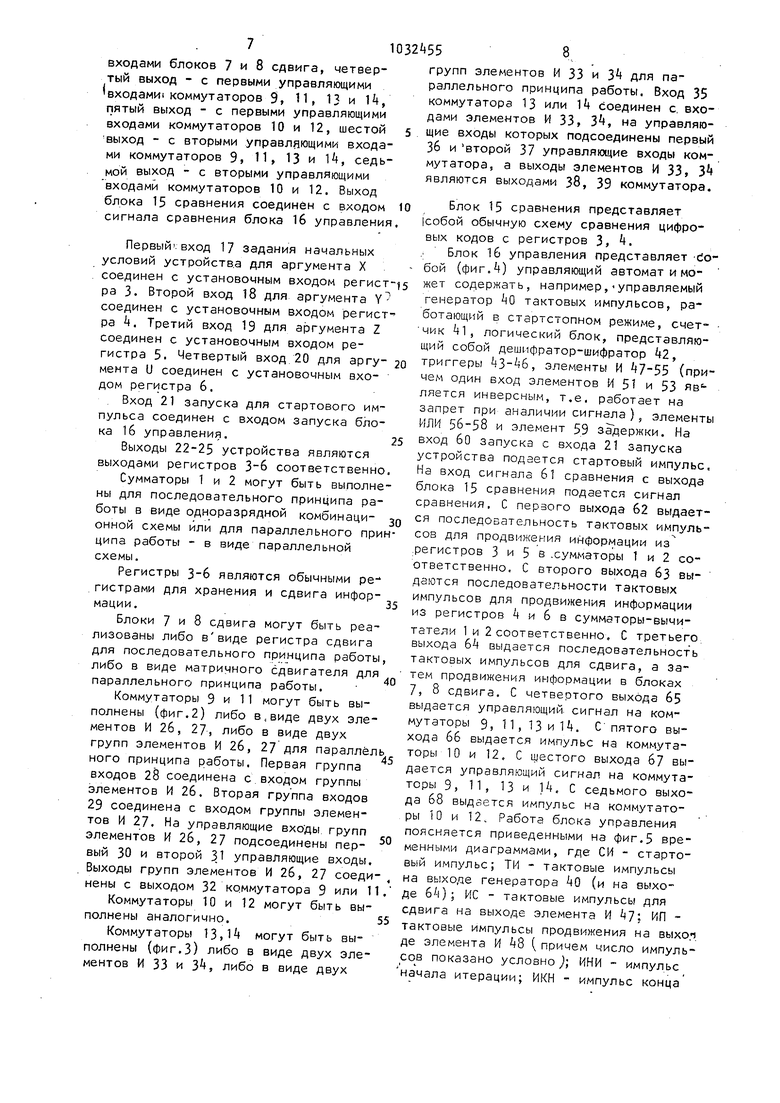

2. Устройство по п,1, о т л и чающееся тем, что блок управления содержит генерзтор импульсов, счетчик, дешифратор-шифратор, четыре триггера, девять элементов И, три , элемента ИЛИ и элемент задержки, вход которого соединен с входом запуска блока управления и первыми входами первого и второго элементов ИЛИ, выход элемента задержки соединен с входом запуска генератора импульсов, вход останова которого соединен с пер вым выходом дешифратора-шифратора и входом сброса счетчика, информационный вход которого соединен с выходом генератора импульсов и первыми агоэдами первого и второго элементов И, выход счетчика .соединен с входом дешифратора-шифратора, второй выход которого соединен с вторым входом второго

элемента ИЛИ, выход которого соединен с первыми входами с первого по третий триггеров и с третьего по пятый элементов И, третий выход дешифраторашифратора соединен с первыми входами /шестого и седьмого элементов И и вто. рыми входами первых элементов ИЛИ и триггера, выходы которых соединены соответственно с первым входом четвертого триггера и вторыми входами первого и второго элементов И, выход второго элемента И соединен с первыми входами третьего элемента ИЛИ, восьмого и девятого элементов И. вход сигнала сравнения блока управления соединен с вторым входом третьего элемента И, выход которого соединен с вторым входом четвертого триггера, выход которого подключен к вторым входам с четвер- , того по седьмой элементов И, выходы шестого и седьмого элементов И соединены с вторыми входами соответственно второго и третьего триггеров, выходы которых соединены с вторыми входами соответственно восьмого и девятого элементов И, выход первого элемента И соединен с вторым входом третьего элемента ИЛИ, выходы восьмого, девятого элементов И, третьегр элемента ИЛИ, второго триггера, четвертого элемента И, третьего триггера и пятого элемента И соединены соответст венно с первого по седьмой выходами блока .управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для вычисления степенных функций | 1985 |

|

SU1282120A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| Вычислительное устройство | 1986 |

|

SU1361546A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для вычисления квадратного корня | 1985 |

|

SU1254477A1 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Устройство для преобразования координат | 1987 |

|

SU1460720A2 |

1

Изобретение относится к цифровой вычислительной технике и может быть применено для аппаратной реализации операций аычисления функции.

Известно устройство для Во числе ния квадратного корня из частного и произведения г содержащее накопительные сдвигающие регистры и регистр падати, управляю1цие входы KOTOpbfx соединены с соответствующими выходами блока управления, одноразрядные комбинационные сумматоры, упра1зляюи ие входы которых соединены с выходами элемента анализа знака, вход которого соединен с выходом знакового рвзряда накопительного сдвигающего регистра псевдоделитепяр элемент анализа сходимости, накопительные сдвигающие регистры и одноразрядный комбинационный сумматор, причем управляющий вход последнего соединен с выходом накопительного сдвигающего регистра второго аргумента, а основной вход этого сумматора, - с выходом последнего разряда накопительного сдвигающего регистра второго псездоумножителя, выход которого соединен с управляющим входом одноразрядного комбинационного сумматора псевдоделителя, третий вход этого сумматора соединен с выходом накопительного сдвитающего регистра второго аргумента, выходы всех разрядов накопительного сдвигающего регистра псевдоделителя соединены с входами элемента анализа сходимости, выход которого соединен с входом сброса блока управления 1. Недостатком данного устройства является ограниченный класс решаемых задач, так как оно предназначено для вычисления только двух функций. Наиболее близким к предлагаемому по технической сущности является устройство для извлечения квадратного корня, содержащее два сумматора, четыре регистра, два блока сдвига, блок сравнения, блок управления и два коммутатора, причем выход первого регистра соединен с первым информационным входом .первого коммутатора, выход которого, соединен с первым входом сумматора, второй вход которого соединен с выходом первого блока сдви га, информационный вход которого соединен с выходом второго коммутатора, первый информационный вход которого соединен с выходом второго регистра, первый вход второго сумматора, соединен с выходом второго блока сдвига, управляющие входы первого и третьего регистров соединены с первым выходом блока управления, второй выход которого соединен с управляющими .входами второго и четвертого регистров, выход блока сравнения соединен с входом сиг нала сравнения блока управления, третий выход которого соединен с управляющими входами блоков сдвига, четвертый выход блока управления соединен с первым управляющим входом первого коммутатора, пятый выход блока управления соединен с первым управляющим входом второго коммутатора 2 Недостатком этого устройства является то, что оно предназначено тол ко для извлечения квадратного корня из одного аргумента, т.е. ограниченный, класс решаемых задач (вычисляемых функций). Цель изобретения - расширение кла са решаемых задач за счет возможност дополнительного вычисления функций .VxTv, fTTx, ifT и u/.fY. Поставленная цель достигается тем что в устройство, содержащее два сум- 55 ка

матора, четыре регистра, два блока сдвига, блок сравнения, блок управления и два коммутатора, причем выход 1

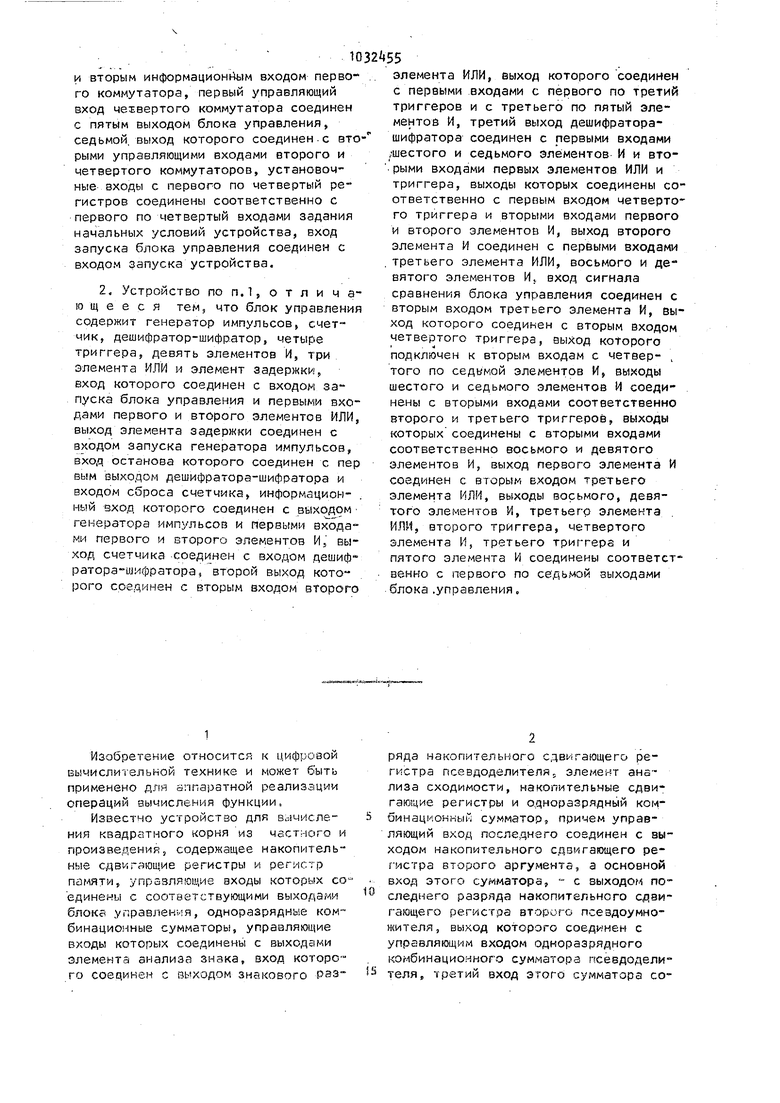

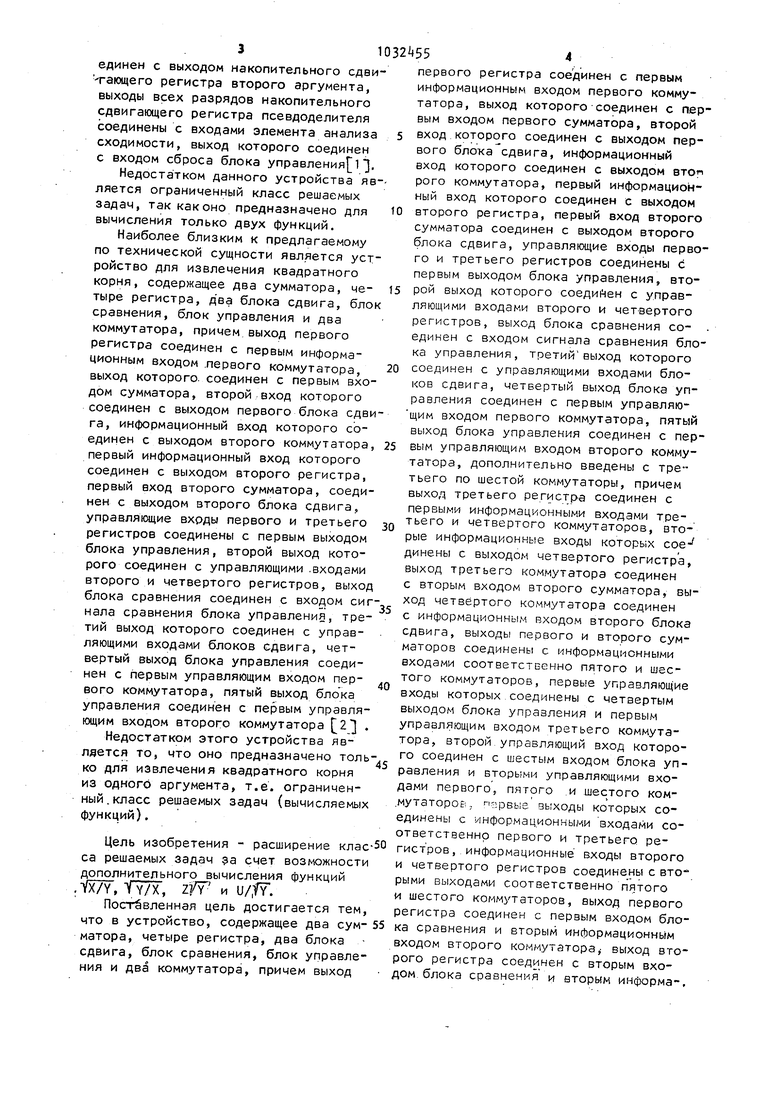

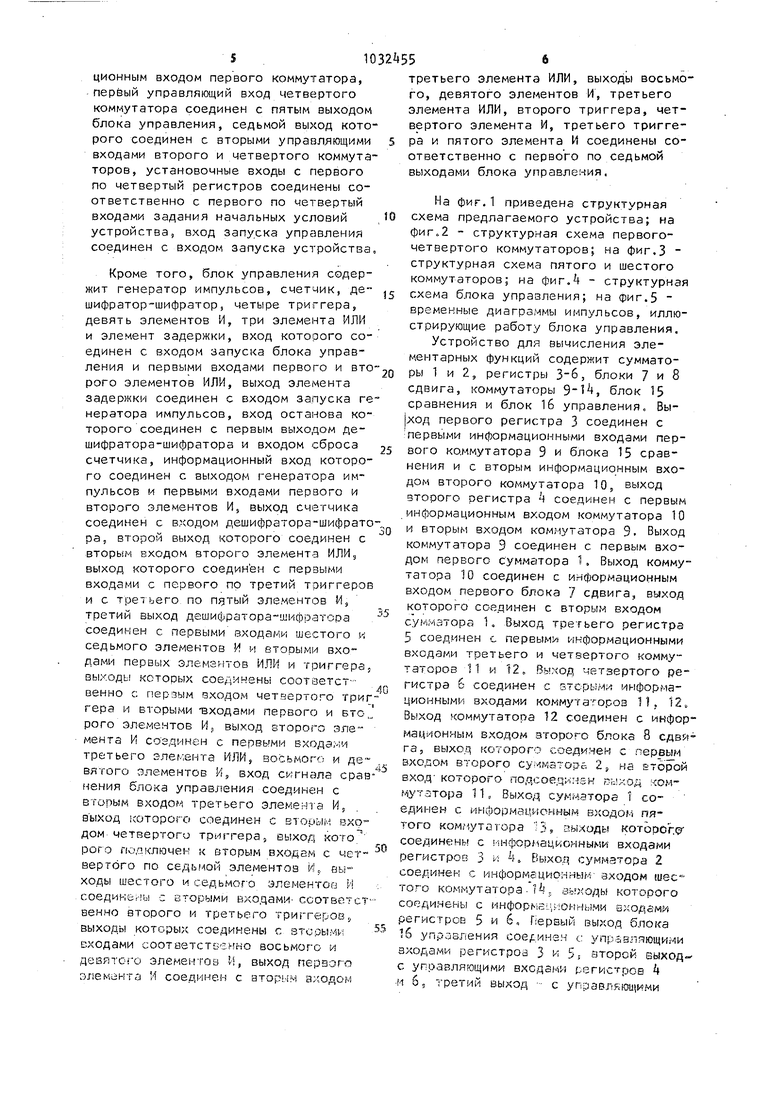

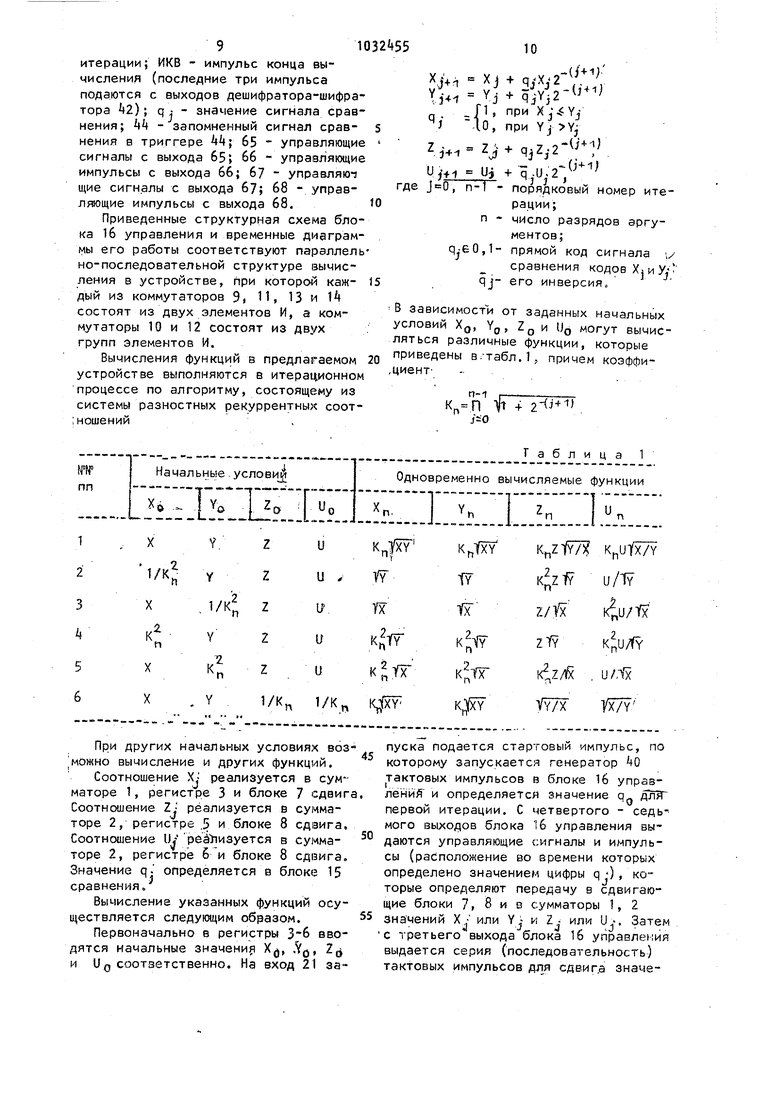

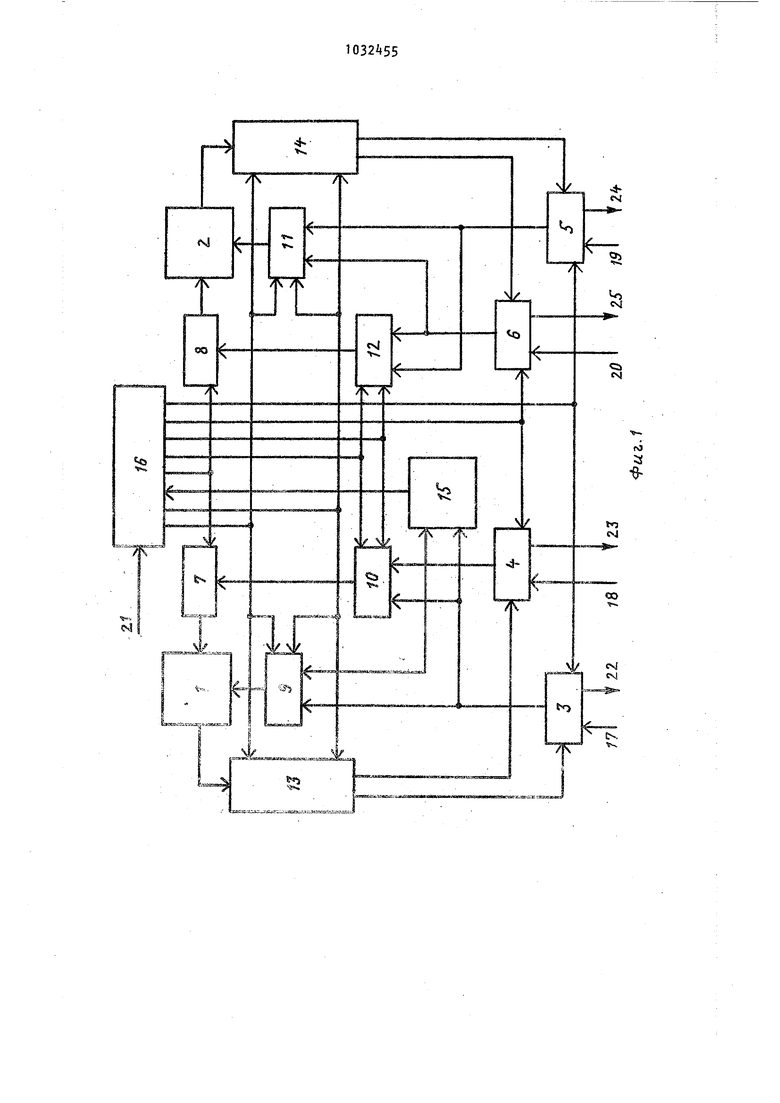

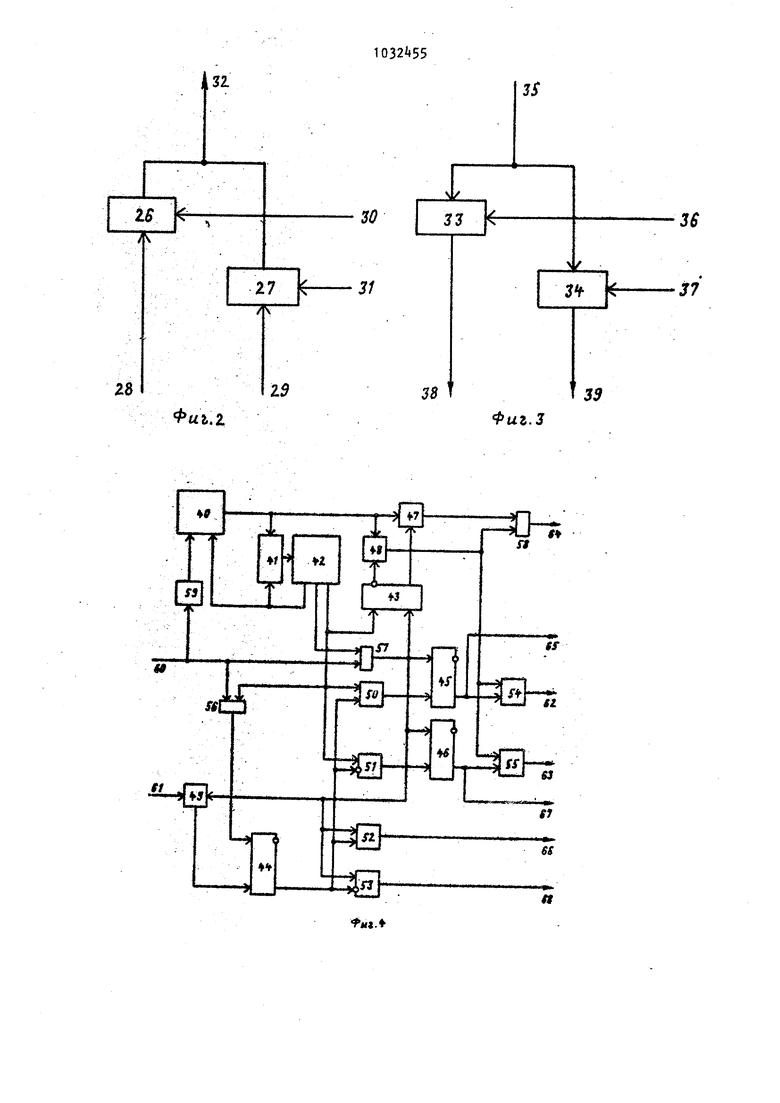

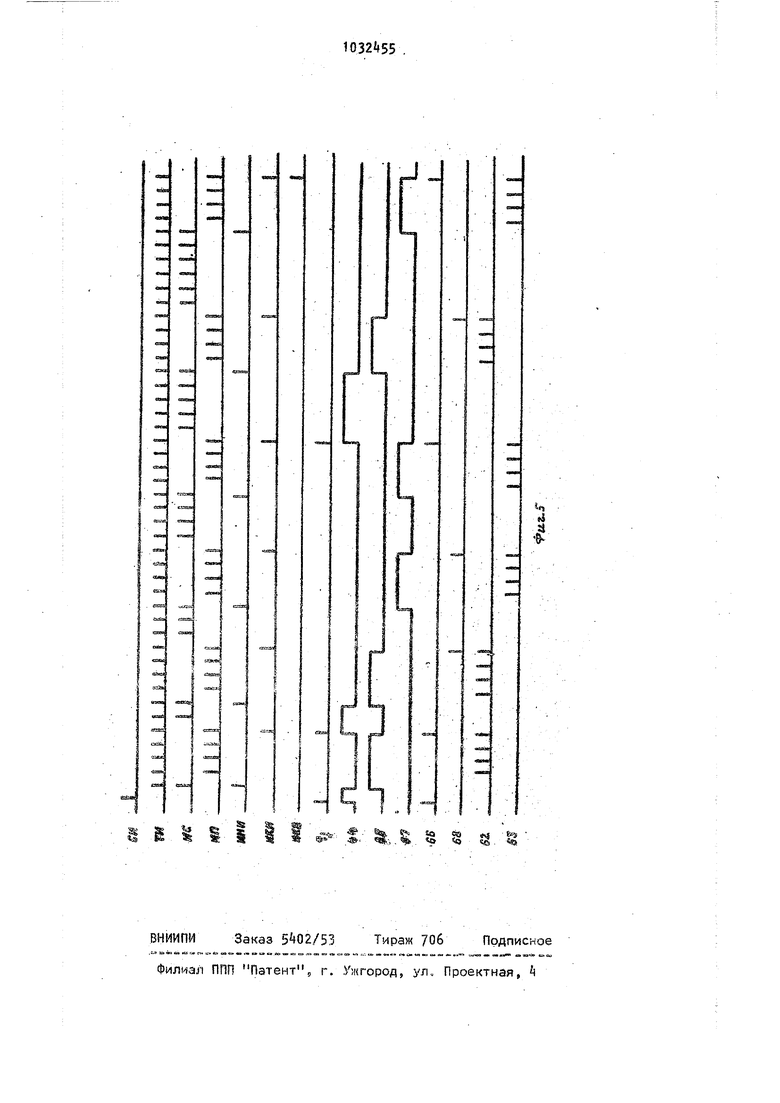

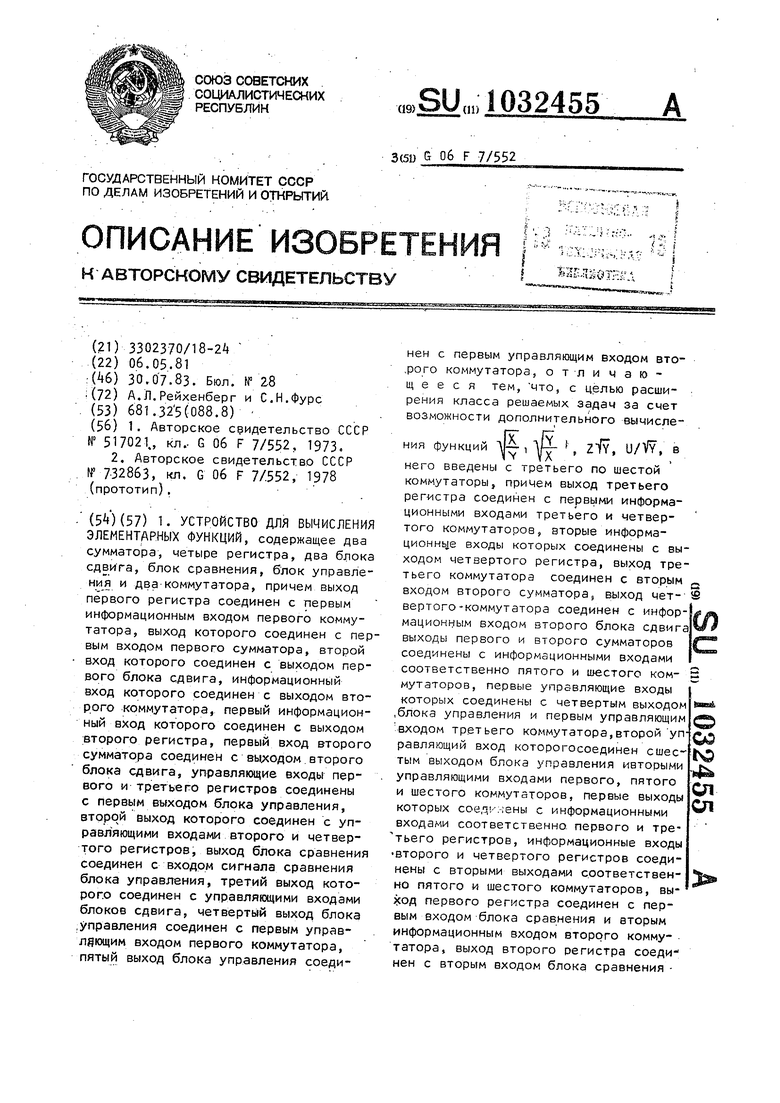

входом второго коммутатора,- выход второго регистра соединен с вторым входом, блока сравнения и вторым информа-. 554 первого регистра соединен с первым информационным входом первого коммутатора, выход которого соединен с первым входом первого сумматора, второй вход которого соединен с выходом первого блока сдвига, информационный вход которого соединен с выходом втол рого коммутатора, первый информационный вход которого соединен с выходом второго регистра, первый вход второго сумматора соединен с выходом второго блока сдвига, управляющие входы первого и третьего регистров соединены d первым выходом блока управления, второй выход которого соедийен с управляющими входами второго и четвертого регистров, выход блока сравнения со- единен с входом сигнала сравнения блока управления, третийвыход которого соединен с управляющими входами блоков сдвига, четвертый выход блока управления соединен с первым управляющим входом первого коммутатора, пятый выход блока управления соединен с первым управляющим входом второго коммутатора, дополнительно введены с третьего по шестой коммутаторы, причем выход третьего регистра соединен с первыми информационными входами третьего и четвертого коммутаторов, вторые информационные входы которых соединены с выходом четвертого регистра, выход третьего коммутатора соединен с вторым входом второго сумматора, выход четвёртого коммутатора соединен с информационным входо.м второго блока сдвига, выходы первого и второго сумматоров соединены с информационными входами соответственно пятого и шестого коммутаторов, первые управляющие входы которых.соединены с четвертым выходом блока управления и первым управляющим входом третьего коммутатора, второй,управляющий вход которого соединен с и1естым входом блока управления и вторыми управляющими входами первого, пятого .и шестого ком.мутатороь, п,7;рвые выходы которых соединены с информационными входами соответственно первого и третьего регистров, информационные входы второго и четвертого регистров соединены с вторыми выходами соответственно пятого и шестого коммутаторов, выход первого регистра соединен с первым входом блосравнения и вторым информационным ционным входом первого коммутатора, первый управляющий вход четвертого коммутатора соединен с пятым выходом блока управления, седьмой выход которого соединен с вторыми управляющими входами второго и четвертого коммута торов, установочные входы с первого по четвертый регистров соединены соответственно с первого по четвертый входами задания начальных условий устройства, вход запуска управления соединен с входом запуска устройства Кроме того, блок управления содержит генератор импульсов, счетчик, дешифратор-шифратор, четыре триггера, девять элементов И, три элемента ИЛИ и элемент задержки, вход которого соединен с входом запуска блока управления и первыми входами первого и вто рого элементов ИЛИ, выход элемента задержки соединен с входом запуска ге нератора импульсов, вход останова которого соединен с первым выходом дешифратора-шифратора и входом сброса счетчика, информационный вход которого соединен с выходом генератора импульсов и первыми входами первого и второго элементов И, выход счетчика соединен с входом дешифратора-шифрато ра. второй выход которого соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первыми входами с первого по третий триггеров и с третьего по пдтый элементов И, третий выход дешифратора-шифратора соединен с первыми входами шестого к седьмого элементов И и вторыми входами первых элемэ-нтов ИЛИ и триггера выходы которых соединены соот|3етст венно с перзым входом четвертого триг гера и вторыми -входами первого и БТО рого элементов И. выход второго элемента И создинен с первыми входами третьего элег/.ента ИЛИ, восьмого и девятого элементов И, вход сигнала срав нения блоха управления соединен с вторым входом третьего элемента 4, выход гсоторого соединен с вторым входом четвертого триггера, выход рого подключен к вторым входам с четвертого по седьмой элементов И, выходы шестого и седьмог-о элементоа И соединены с вторыми входами ссответст венно второго и третьего триггеров, выходы которых соединены с ЗТСрЫМ5-; сходами соответстеенно восьмого и выход пераого девятого элеме1- тоз и, элемента И соединен с вторым аходом 10 56 третьего элемента ИЛИ, выходы восьмого, девятого элементов И, третьего элемента ИЛИ, второго триггера, четвертого элемента И, третьего триггера и пятого элемента И соединены соответственно с первого по седьмой выходами блока управления. На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - структурная схема первогочетвертого коммутаторовj на фиг.З структурная схема пятого и шестого коммутаторов; на фиг, - структурная схема блока управления; на фиг.5 временные диаграммы импульсов, иллюстрирующие работу блока управления. Устройство для вычисления элементарных функций содержит сумматоры 1 и 2, регистры З-б, блоки 7 и 8 сдвига, коммутаторы 9-1, блок 15 сравнения и блок 16 управления. Вы1ход первого регистра 3 соединен с первыми информационными входами первого коммутатора 9 и блока 15 сравнения и с вторым информационным входом второго коммутатора 10, выход второго регистра соединен с первым информационным входом коммутатора 10 и вторым входом коммутатора 9. Выход коммутатора 9 соединен с первым входом первого сумматора 1. Выход коммутатора 10 соединен с информационным входом первого блока 7 сдвига, выход к оторого соединен с вторым входом сумматора 1. Выход третьего регистра 5 соединен с первым информационными входами третьего и четвертого коммутаторов 11 и 12, Выход четвертого регистра б соединен с вторыми информационными входами коммутатороа 11. 12. Выход коммутатора 12 соединен с информационным входом второго блока 8 сдвй га, выход которого соединен с первым входом второго cyiviK3Topa 2, на еторой вход- которого подсоединен РЫХОД нсоммутзтора 11, Выход сумматора 1 соединен с информационным входом пятого коммутатора 13s выходы которог. соединень с информаир;оинымк входами регистров 3 и k. Выход сумматора 2 соединен с информационным входом шес того коммутатора. выходы которого соединены с информвционными входами регистров 5 и 6, Первый выход блока 1б управления соединен с упр вляющи и входами регистроа 3 У 5,- агорой выход с управляющими входами регистров 4 м 6, третий выход - с упрзвпяюу ими входами блоков 7 и 8 сдвига, четвертый выход - с первыми управляющими входами коммутаторов 9, 11, 13 и 1, пятый выход - с первыми управляющими входами коммутаторов 10 и 12, шестой выход - с вторыми управляющими входами коммутаторов Э, 11 13 и Н, седьмой выход - с вторыми управляющими входами коммутаторов 10 и 12. Выход блока 15 сравнения соединен с входом сигнала сравнения блока 16 управления Первый, вход 17 задания начальных условий устройств.а для аргумента X соединен с установочным входом регист ра 3. Второй вход 18 для аргумента Y соединен с установочным входом регист ра А. Третий вход 19 для аргумента Z соединен с установочным входом регистра 5. Четвертый вход 20 для аргумента и соединен с установочным входом регистра 6. Вход 21 запуска для стартового импульса соединен с входом запуска блока 1б управления. Выходы 22-25 устройства являются выходами регистров соответственно Сумматоры 1 и 2 могут быть выполне ны для последовательного принципа работы в виде одноразрядной комбинационной схемы или для параллельного при ципа работы - в виде параллельной схемы. Регистры 3-6 являются обычными ре гистрами для хранения и сдвига информации. Блоки 7 и 8 сдвига могут быть реализованы либо ввиде регистра сдвига для последовательного принципа работы либо в виде матричного сдвигателя для параллельного принципа работы. Коммутаторы 9 и 11 могут быть выполнены (фиг.2) либо в,виде двух элементов И 2б, 27, либо в виде двух групп элементов И 2б, 27 для параллел ного принципа работы. Первая группа входов 28 соединена с входом группы элементов И 26. Вторая группа входов 29 соединена с входом группы элементов И 27. На управляющие входы групп элементов И 26, 27 подсоединены первый 30 и второй 31 управляющие входы. Выходы групп элементов И 26, 27 соеди нены с выходом 32 коммутатора 9 или 1 Коммутаторы 10 и 12 могут быть выполнены аналогично. Коммутаторы 13,14 могут быть вы полнены (фиг.З) либо в виде двух элементов И 33 и 34, либо в виде двух групп элементов М 33 и 3 для параллельного принципа работы. Вход 35 коммутатора 13 или It соединен с, входами элементов И 33, З, на управляющие входы которых подсоединены первый Зб ивторой 37 управляющие входы ком-. мутатора, а выходы элементов И 33, З являются выходами 38, 39 коммутатора. Блок 15 сравнения представляет |собой обычную схему сравнения цифровых кодов с регистров 3, t. Блок 16 управления представляет doбой (фиг.) управляющий автомат и может содержать, например,-управляемый генератор 0 тактовых импульсов, работающий в стартстопном режиме, счет- чик 41, логический блок, представляющий собой дешифратор-шифратор k2, триггеры , элементы И (причем один вход элементов И 51 и 53 является инверсным, т.е. работает на запрет при аналичии сигнала ), элементы ИЛИ 56-58 и элемент 59 задержки. На вход 60 запуска с входа 21 запуска устройства подается стартовый импульс, На вход сигнала 61 сравнения с выхода блока 15 сравнения подается сигнал сравнения. С первого выхода 62 выдается последовательность тактовых импуль сов для продвижения информации из .регистров 3 и 5 в .сумматоры 1 и 2 соответственно, С второго выхода 63 выдаются последовательности тактовых импульсов для продвижения информации из регистров 4 и 6 в сумматоры-вычитатели 1и 2 соответственно, С третьего выхода 64 выдается последовательность тактовых импульсов для сдвига, а затем продвижения информации в блоках 7, 8 сдвига. С четвертого выхода б5 выдается управляющий сигнал на коммутаторы 9, 11, 13 и 14. С пятого выхода 66 выдается импульс на коммутаторы 10 и 12, С щестого выхода 67 выдается управляющий сигнал на коммутаторы 9, 11, 13 и 14. С седьмого выхода 68 выдается импульс на коммутаторы 10 и 12. Работа блока управления поясняется приведенными на фиг.5 временными диаграммами, где СИ - стартовый импульс; ТИ - тактовые импульсы на выходе генератора 40 (и на выходе 64); ИС - тактовые импульсы для сдвига на выходе элемента И 47: ИП тактовые импульсы продвижения на выхо.ч. де элемента И 48 (. причем число импульсов показано условно ; ИМИ импульс начала итерации; ИКН - импульс конца 91032i 55 итерации; ИКВ - импульс конца вычисления (последние три импульса подаются с выходов дешифратора-шифратора 2); q ; - значение сигнала сравнения; 4 - запомненный сигнал срав- s нения е триггере 4; б5 - управляющие сигналы с выхода 65; 66 - управляющие импульсы с выхода 66; 67 - управляют щие сигналы с выхода 67; 68 - управляющие импульсы с выхода 68. О Приведенные структурная схема блока 16 управления и временные диаграммы его работы соответствуют параллель но-последовательной структуре вычисления в устройстве, при которЫ каж- 15 дый из коммутаторов 9) 11, 13 и 1 состоят из двух элементов И, а коммутаторы 10 и 12 состоят из двух групп элементов И. Вычисления функций в предлагаемом 20 Ри устройстве выполняются в итераиионном .Цие При других начальных условиях воз можно вычисление и других функций. Соотношение XJ реализуется в сумматоре 1, регистре 3 и блоке 7 сдвиг Соотношение Zj реализуется в сумматоре 2, регистре.5 и блоке 8 сдвига. Соотношение Uj рбй изуется в сумматоре 2, регистре 6 и блоке 8 сдвига. Значение q определяется и блоке 15 сравнения. Вычисление указанных функций осуществляется следующим образом. Первоначально в регистры вводятся начальные значения Х, .Y, Z и и о соотзетственно. На вход 21 загдеВ з усл лят 2-(/+) Xj + q/X. ,. , „J . -l-,J,-(j4ij j-H q-jY32 при при Yj Y.| z.,-,2-/ 1 - порядковый номер итерации ; число разрядов аргументов; ,1прямой код сигнала ;у сравнения кодов Х и У.qj- его инверсия. ти от заданных начальных Z о и УО могут вычисоичные функции, которые /табл., причем коэффипуска подается стартовый импульс, по которому запускается генератор «О тактовых импульсов в блоке 1б управлений и определяется значение q дл первой итерации. С четвертого - седь-мого выходов блока 16 управления выдаются управляющие сигналы и импульсы (расположение во времени которых определено значением цифры q ), которые определяют передачу а сдвигающие блоки 7 8 и в сумматоры 1, 2 значений X или Yj и Zj или Uv. Затем с третьего выхода блока 16 управления выдается серия (последовательность) TaKtoEibix импульсов для сдвиг.а значе111032 5512

ния X или YJ (в зависимости от значе-одном из регистров 3, или k и S, или

ния Ц;) и Z.-или Uj в блокзх 7 и 86 записано новое значение, а. в другом

сдвига доотвЁтственно. После окон- находится предыдущее значение. По почания сдвига с первого или второгоследнему тактовому импульсу продвивыходое (при с первого, а при 5жения производится сравнение значеq ; 0 с второго) и третьего выходовний Xj и Y. Затем производится вы1блока управления выдаются серии (по-полнение следующей итерации и т.д.

следовательности) тактовых импульсовПосле выполнения п итераций генерадля продвиженияг.содержаний регистровтор тактовых импульсов в блоке 1б уп3 или k и блока 7 сдвига и регистров 0равления выключается, а в регистрах

5 или 6 и блока 8 сдвига в сумматоры3 6 содержатся значения функций

1 и 2 соответственно. Результаты сум-Х. Ур, U, соответственно. мирования с выходов сумматоров 1 и 2 ,

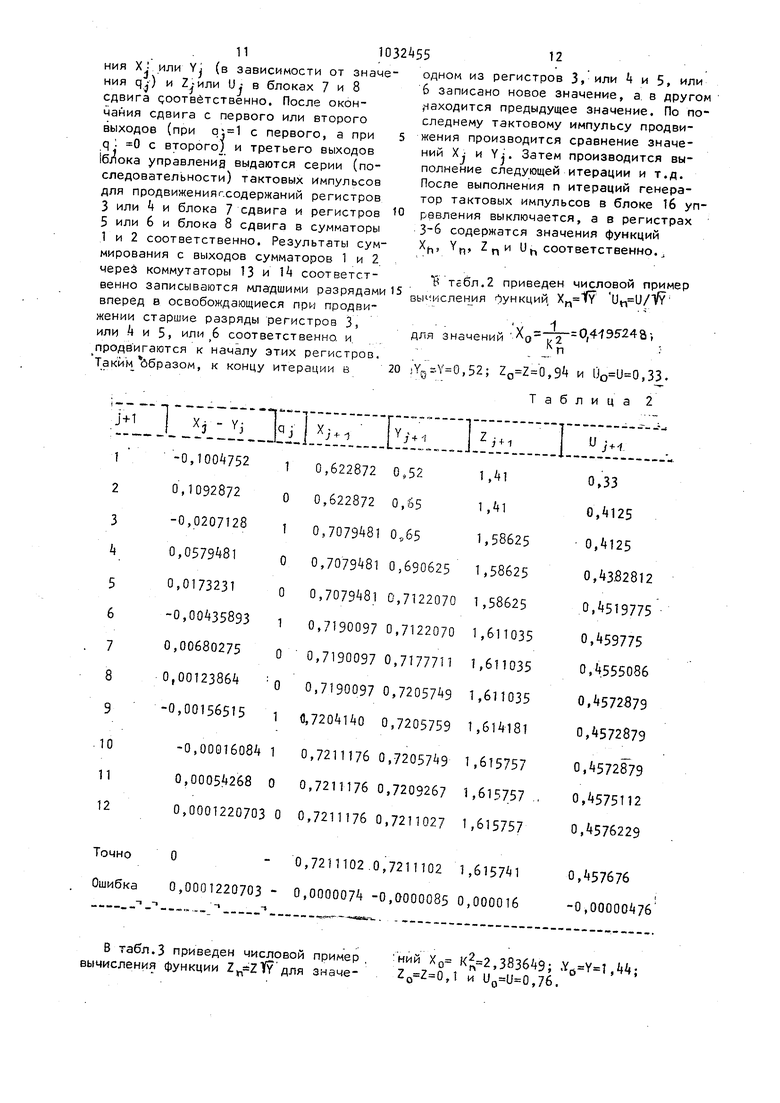

через коммутаторы 13 и 14 соответст- 8 тб6л,2 приведен числовой пример

венно записываются младшими разрядами 15вы1;исления функций, Uo U/VY вперед в освобождающиеся при продвижении старшие разряды регистров 3, или / и 5, или 6 соответственно, и. продвигаются к началу этих регистров. , . .

ТаКИМ йбразом, к концу итерации в 20 ,52; ,9t и ,33.

1 JA:ZilliJItLl i L.Z:L.

-0,

10,622872 0,521,4l

о , 1092872

00,622872 0,65l,4l

-0,0207128

10, 0,651,58625

0, 00, 0,6906251,58625

0,0173231

00, 0,71220701,58625

-0,00 35893

10,7190097 0,71220701,611035

0,00680275 0 0,7190097 0,71777111,611035

0,00123864 00,7190097 0,72057 91,611035

-0,00156515 ,7204140 0,72057591,6l4l8l

-0,0001608/4 10,7211176 0,72057491,615757

0,00054268 00,7211176 0,72092671,615757

0,0001220703 00,7211176 0,72110271,615757

0 - 0,7211102.0,7211102 1,615741 Ошибка 0,0001220703 - 0,0000074 -0,0000085 0,000016

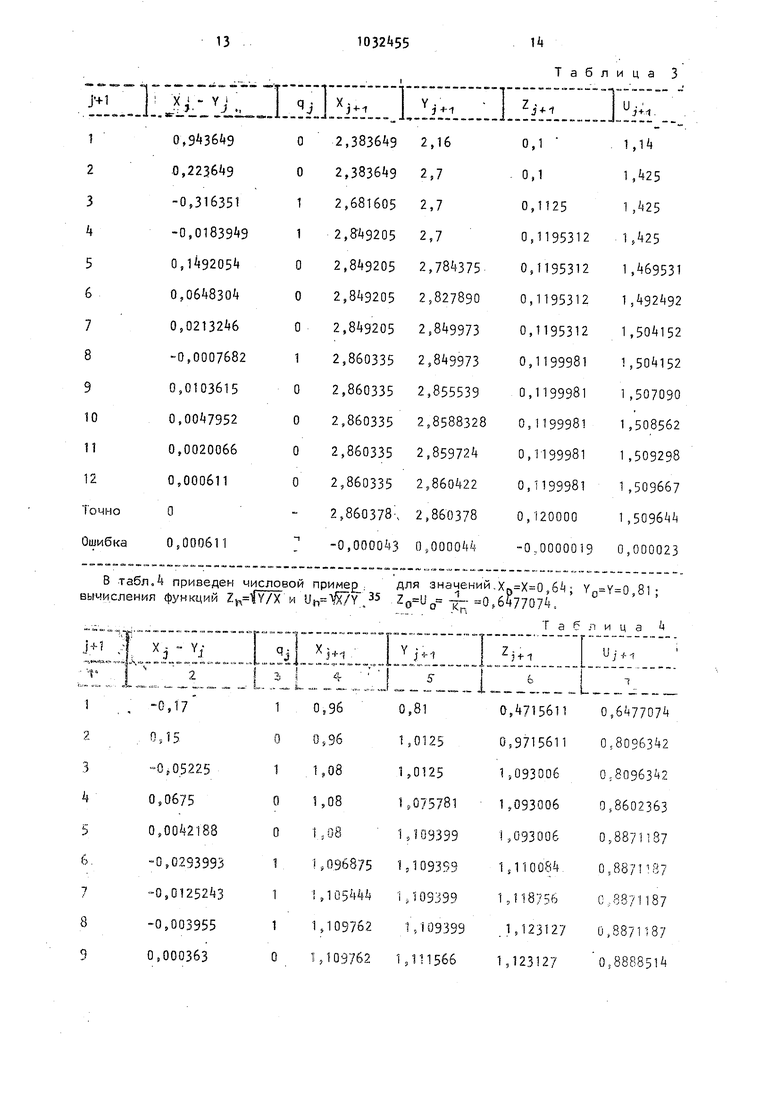

В табл.3 приведен числовой пример , вычисления функции 2,2 У для значедля значений .

Таблица 2

0,4125

0,4125

0,43.82812

0,519775

0,459775

0,4555086

0,4572379 0,4572879

0.4572879 0,4575112

0,4576229

0,457676 -0,00000476

-ний Хо ,383649; .Y.,44; ,1 и ,76. В табл.4 приведен числовой npMMeg ; вь(числения функций Z fY/X и U,f, W/Y , 5

Таблица 3

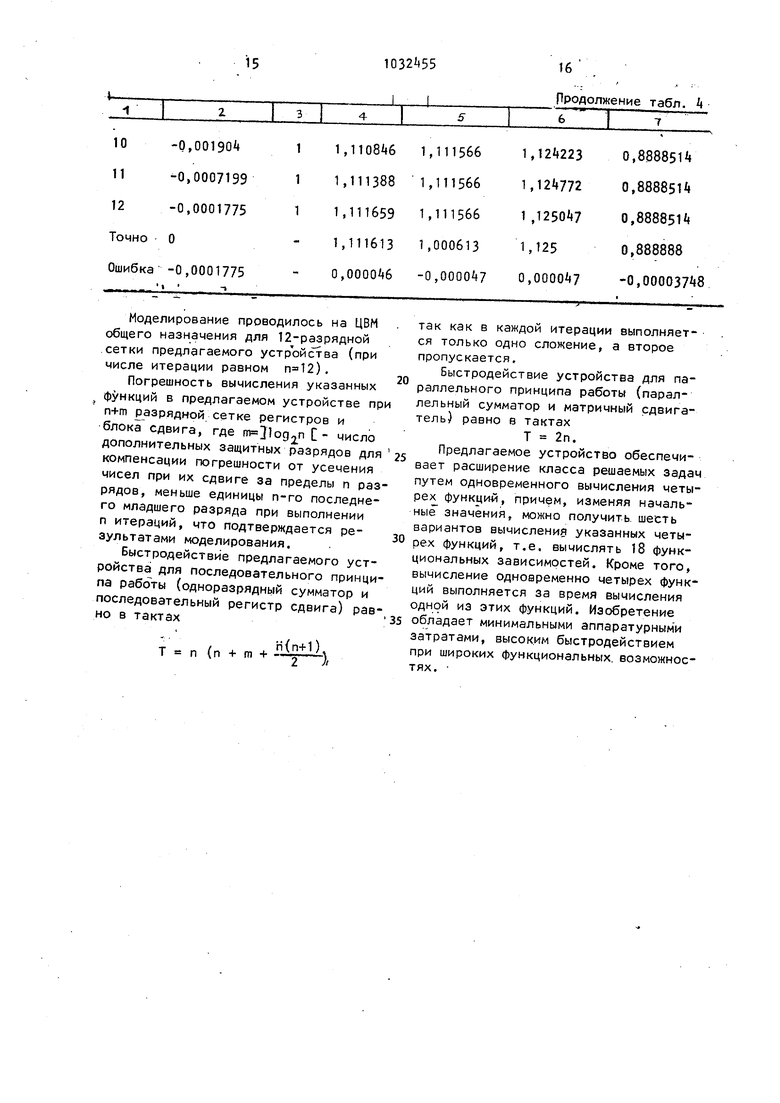

Т а б л и ц а для значений,х.,,6 ; ,81; . ..647707 Моделирование проводилось на ЦВМ общего назначения для 12-разрядной .сетки предлагаемого устройства (при числе итерации равном ). Погрешность вычисления указанных функций в предлагаемом устройстве пр n+m разрядной сетке регистров и блока сдвига, где )og, число дополнительных защитных разрядов для компенсации погрешности от усечения чисел при их сдвиге за пределы п раз рядов, меньше единицы п-го последнего младшего разряда при выполнении п итераций, что подтверждается результатами моделирования. Быстродействие предлагаемого устройства для последовательного принци па рабсугы (одноразрядный сумматор и последовательный регистр сдвига) рав но в тактах . ™ . «l-iiii

Продолжение табл. А так как в каждой итерации выполняется только одно сложение, а второе пропускается. Быстродействие устройства для параллельного принципа работы (параллельный сумматор и матричный сдаигатель) равно в тактах Т 2п. Предлагаемое устройство обеспечивает расширение класса решаемых задач путем одновременного вычисления четырех функций, причем, изменяя начальные значения, можно получить, шесть вариантов вычисления указанных четырех функций, т.е. вычислять 18 функциональных зависимостей. Кроме того, вычисление одноаременно четырех функций выполняется за время вычисления одной из этих функций. Изобретение обладает минимальными аппаратурными затратами, высоким быстродействием при широких функциональных, возможностях.

(О

5{

3S

s/

36

r

Л

27

25

28

Pui.i

37

3139

38

Фиг.З

ц 4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления квадратного корня из частного и произведения двух аргументов | 1973 |

|

SU517021A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1983-07-30—Публикация

1981-05-06—Подача