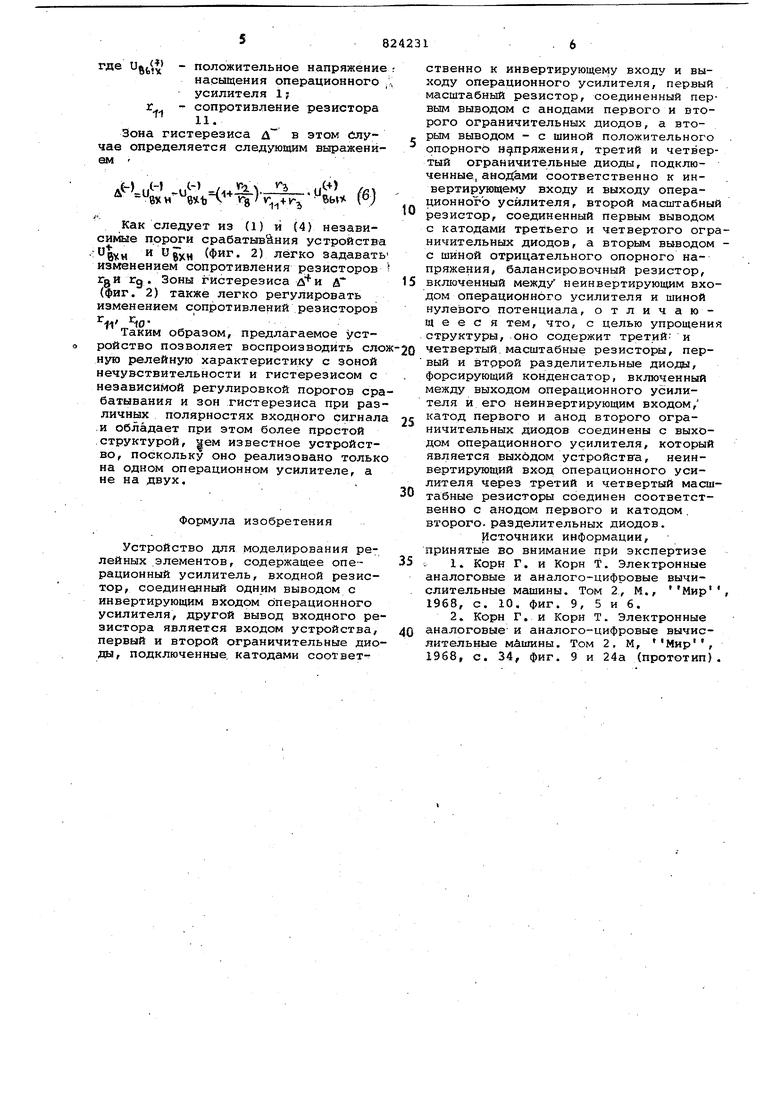

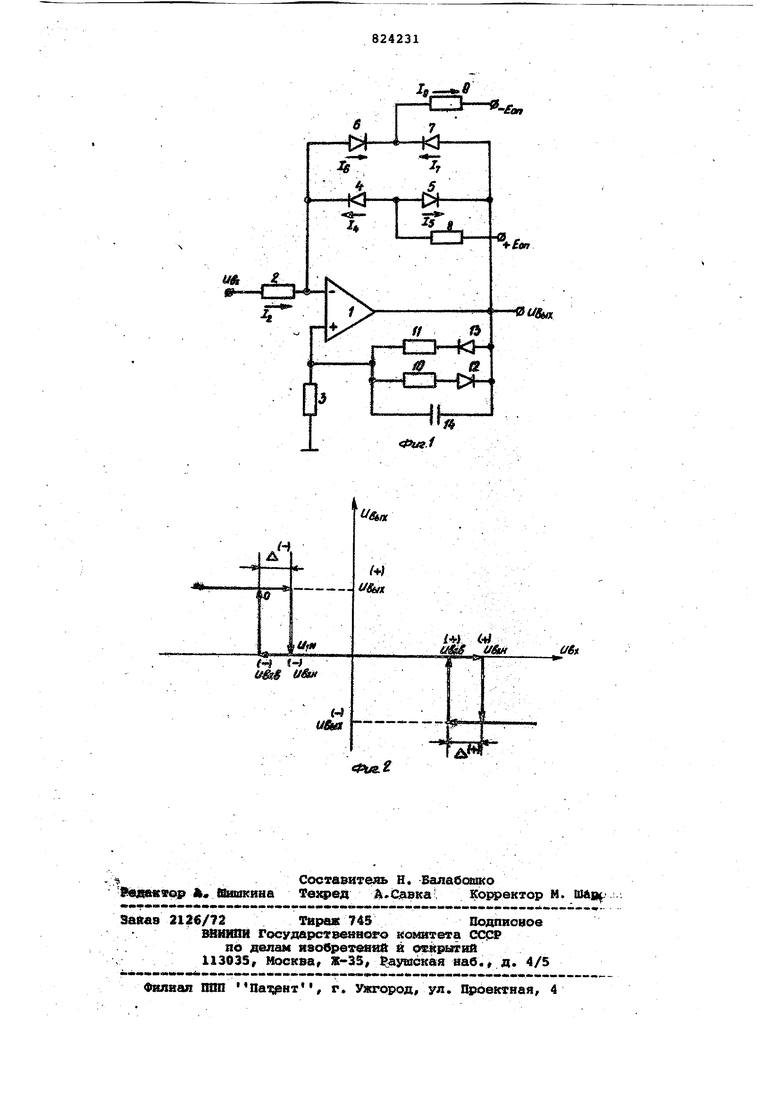

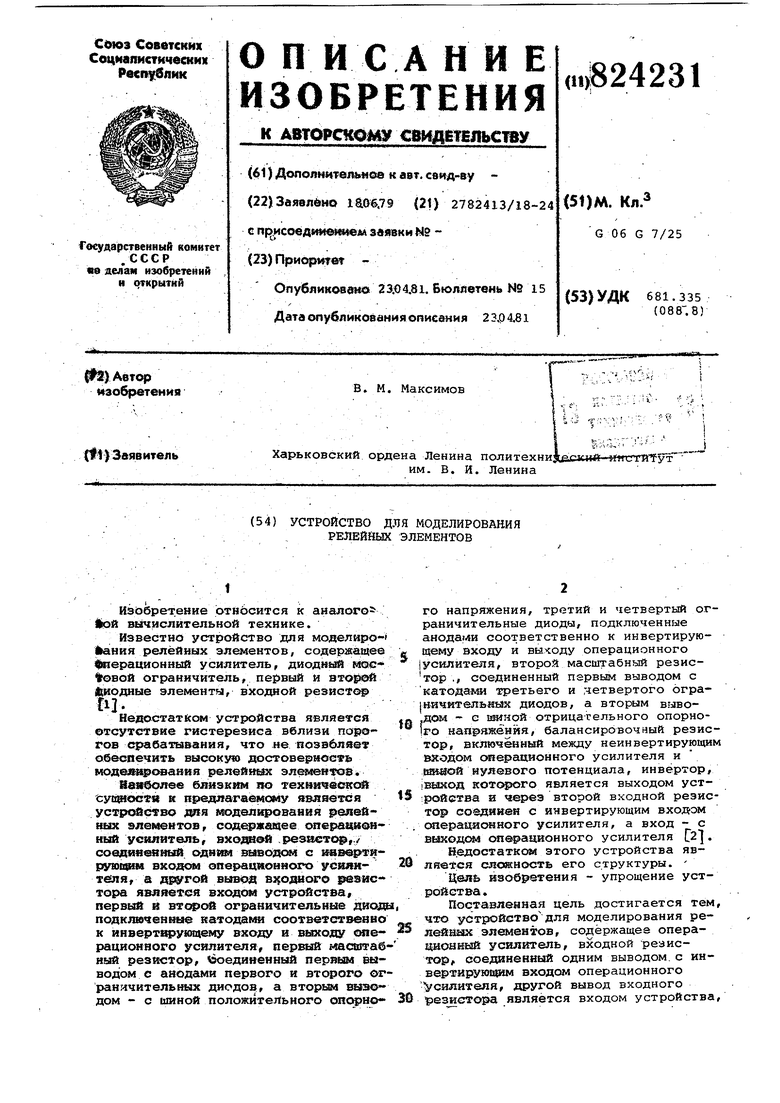

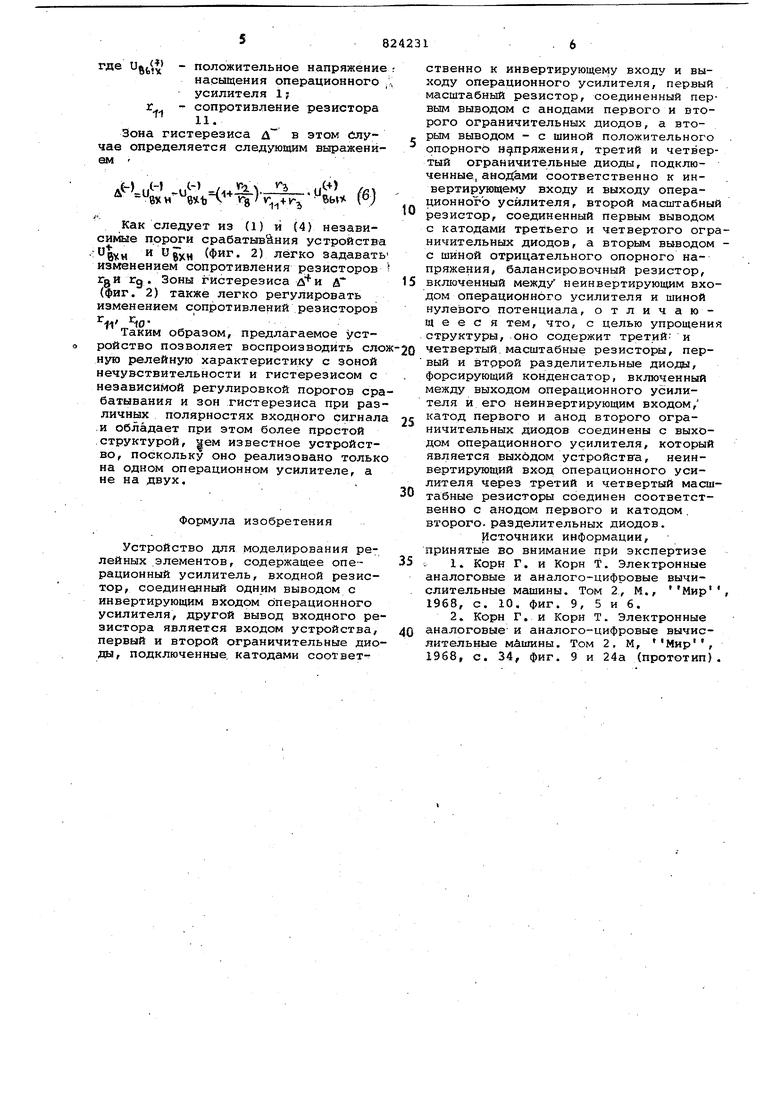

, . . . ,1 И&обретение бтнЬсится к аналого ой вычислительной текинке. Известно усггройство для моделироания релейных элементов, содержащее ерационный усилитель, диодн мое %овой ограничитель, первый и второй Киодные элементы, входа5ой резистор Недостатком устройства является отсутствие гистерезиса вблизи порогов срабатавани я, что не йозвбляечг обеспечить высокую достовериоефь модевнроаа ия релейт х элементов. 8ast6ojiee близким по техничёсжс сувдноств к йредлагаёмсму авляется моделирования релейных элементов, сод жатее опера шонный усилитель, входаей .,/ соединенный выводом с иаверт РУЮ1Ф1М входом операционного усияктеэтя, а вывод вз оянс« о резистора явяяетея входом устройства, первц и второе ограничительные диода подключенные катодами соответственно к инвертед ующему входу и выходу ояерационяого усилителя, первый масштаб ный резистор, Уединенный первым выводом с анодами первого и второго ог раничительных диодов а вторьгм ет«эо дом - с шиной положительного опсфнв го напряжения, третий и четвертый ограничительные диоды, подключенные анодами соответственно к инвертирующему входу и выходу операционного усШ1ителя, второй масштабный резистор ., соединенный первым выводом с катоданет третьего и г-1етвертого огра н-йчительвъйс диодов, а вторым выводом - с йшиой отрицательного опорно|го напряжёнйя, балансировочный резистор, включенный между неинвертирующим входом сяерационного усилителя и шшкхй нулевого потенциала, инвертор, шаход которого является выходом уст;ройства и через второй входной резистор соединен с инвертирующим входом с«1ерацисданого усилителя, а вход - с вшсодс операционного усилителя 2. Недостатком этого устройства является слоясность его структуры. Цель изобретения - упрощение устройства. Поставлейная цель достигается тем, что устройстводля моделирования реяеййих элементов, содержащее операциоанЕзй усилитель, входной реаистор, соедзненный одним выводом.с инвертирующим входом операционного -Усилителя, другой вывод входного зезистс а является входом устройства. яофоый и второй ограничительные йоды/ подключенные катодами соответственно к инвертирующему входу и выходу операционного усилителя, первый масштабный резистор, соединенный пер вым выводе с анодами первого и второго ограничительных диодов, а вторым выводом - с шиной положительного спорного напряжения, и четвертый ограничительные диоды, подключенные анодами соответственно и .иняерти1 ующему входу и выходу операционного усилителя, второй масштабный резистор, соединенный первым выводом с катодами третьего и чдтвертогс ограничительных диодов, а вторым выводом - с. шиной отрицательного опорного напряжения, .балансировечный резиотор, включ энный между неинвертирующим входом операционного усилителя и шиной нулевого потен- . циала, дополнительно содержит третий и четвертый масштабные резисторы, пе вый и второй разделительные диода|, форсирующий конденсатор, включенный между выходом операционного усилителя и его неинвертирующим входом,, катод первого и анод второго ограничительных диодов соединены с выходом операционного усилителя, который является выходом устройства, неинвертирующий вход операционйого усилителя через третий и четвертый масштабные резисторы соединен соответственно с анодом первого и катодсШ второго разделительных диодов. На фиг„ 1 приведена схема усгройства, на фиг его выходйай характеристика. Устройство содержит операционный усилитель 1, входной рези-стор 2, балансировочвый резистор 3, первый четвертый огракичительиые диода 4-7, кйрвый четвертый масштабные резисторы B-ll, иервый и второй разделительные диоды 12 и 13, форсирующий конденсатор 14, . Устройство работает следующим образом, Если напряжение входного сигнала g равно нулю, то т выходное напряжение операционного усилителя 1 также равао нулю, поскольку ограничител вы-е диоды 4-7 смещвйег в прямом наяравленаи и соггЕютищиенив отрицатель ной обратной связи оя1врацнон ого уси лйтеяя i равно нулю при УСЛОВИЙ,, что Диоды 4-7 идеальйвге. Ври иоложитель MitaM вкодном напряжении О g« диоды4 и 7 зак{ш1ваются, а § и € еще / Зояьше обещаются в пряшюм направле НИИ, Когда диоды 4. и 7 закрокпся, ; отрицательная обратная связь ояерацйонного усилителя I разрывается и ой переходит в состояние отрицательного насыщения. Форсирующий конденсатор 14 обеспечивает ускорение процесса перехода операционного усилителя 1 в состояние насыщения; В момент закрытия диодов 4 и 7.выполняется равенство токов Л и J, откуда следует, с учетом рав,енства нулю йаПряжения в .суммирующей точке операционного усилителя 1, что входное напрйжение , соответствующее насыщению операционного усилителя 1, равно у( gH Vrtu, f. ir« ЛГ1 где г сопротивление резистора а 2; Гд - сопротивление резистора 9; Оп напряжение на шине отрица.тельного опорного напряжения. При снижении положительного входного напряжения возврат операцион-г ного усилителя 1 в начальное состояние с нулевым выходным н,апряжением происходит при меньшем входном напряжении и gjj, поскольку в этом случае на неинвертируюадий вход операционного усилителя 1 подается отрицательное напряжение с его выхода через делитель, образованный резисторами 10 и 3 ,.( а /1 ъ .Л, Ччъ | опЧ - - бых (2) где Ugj,,- отрицательное напряжение насыщения операционного усилителя 1; сопротивление резистора . 10; Гл - сопротивление резистора Зона гистерезиса при положительном входном напряжении определяется разностью Ugxji и Ugyg /+)..(+ .,( --.I/Д %ЛУЪ Если входное напряжение отрицательное, то закрываются диода 5 и б. В этом случае входное напряжение , при которсил сшерационный усилитель 1 переходит в состояние положительного насыщения, определяется следующим образом U - -i3Lc 6x«r1 fcen где Efjf) - напряжение на шине положительного опорного напряжения;Ге - сопротивление резистора 8Г Входное напряжение возврата U о аналогии с (2) определяется следуюкувч о&разом . С-|С-(«%)-.-и;;„ р| где и-- -положительное напряжение нарыщения операционного усилителя 1; -сопротивление резистора 11, Зона гистерезиса д в этом с5лучае определяется следующим выражением .Л-) /,Уа г иС+) Как следует из (1) и (4) независимые пороги срабатыв&ния устройства ЙУМ ixH (фиг. 2) легко задавать изменением сопротивления резисторов rgH Гд. Зоны гистерезиса д (фиг. 2) также легко регулировать изменением сопротивлений резисторов 11 fO Таким образом, предлагаемое устройство позволяет воспроизводить сло ную релейную характеристику с зоной нечувствительности и гистерезисом с независимой регулировкой порогов сра батывания и зон гистерезиса при раз личных полярностях входного сигнал ,и обладает при этом более простой структурой, |ем известное устройство, поскольку оно реализовано тольк на одном операционном усилителе, а не на двух. Формула изобретения Устройство для моделирования релейных .элементов, содержащее операционный усилитель, входной резистор, соединенный одним выводом с инвертирующим входом операционного усилителя, другой вывод входного ре зистора является входом устройства, первый и второй ограничительные дио ды, подключенные, катодами соответственно к инвертирующему входу и выходу операционного усилителя, первый масштабный резистор, соединенный первым выводом с анодами первого и второго ограничительных диодов, а вторым выводом - с шиной положительного опорного напряжения, третий и четвертый ограничительные диоды, подключенные, анодами соответственно к инвертирующему входу и выходу операционного усилителя, второй масштабный резистор, соединенный первым выводом с катодами третьего и четвертого ограничительных диодов, а вторым выводом с шиной отрицательного опорного напряжения, балансировочный резистор, включенный между неинвертирующим входом операционного усилителя и шиной нулевого потенциала, отличающееся тем, что, с целью упрощения структуры, оно содержит третий и четвертый, масштабные резисторы, первый и второй разделительные диоды, форсирующий конденсатор, включенный между выходом операционного усилителя и его неинвертирующим входом, катод первого и анод второго ограничительных диодов соединены с выходом операционного усилителя, который является выхбдом устройства, неинвертирующий вход операционного усилителя через третий и четвертый масштабные резисторы соединен соответственно с анодом первого и катодом. второго, разделительных диодов. Источники информации, принятые во внимание при экспертизе ; 1. Корн г. и Корн т. Электронные аналоговые и аналого-цифровые вычислительные машины. Том 2, М., Мир, 1968, с. 10. фиг. 9, 5 и 6. 2, Корн Г. и Корн Т. Электронные аналоговые и аналого-цифровые вычислительные МИШИНЫ. Том 2, М, Мир, 1968, с. 34, фиг. 9 и 24а (прототип).

-Л

Vfi

Амг./

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА АВТОМАТИЧЕСКОЙ РЕГУЛИРОВКИ УСИЛЕНИЯ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 2018 |

|

RU2684510C1 |

| Компаратор абсолютных величин | 1978 |

|

SU752217A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Устройство для выделения максимального сигнала | 1980 |

|

SU959098A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Перемножающее устройство | 1987 |

|

SU1465896A1 |

| Функциональный преобразователь | 1985 |

|

SU1405078A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Оптоэлектронный умножитель | 1981 |

|

SU1012287A1 |

| Импульсное устройство сравнения | 1987 |

|

SU1443157A1 |

Н

А

е

4i4

М 1 е/&и

W Мбит

М М

U6t

ит и&и

ж

Авторы

Даты

1981-04-23—Публикация

1979-06-18—Подача