Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения - повышение точности.

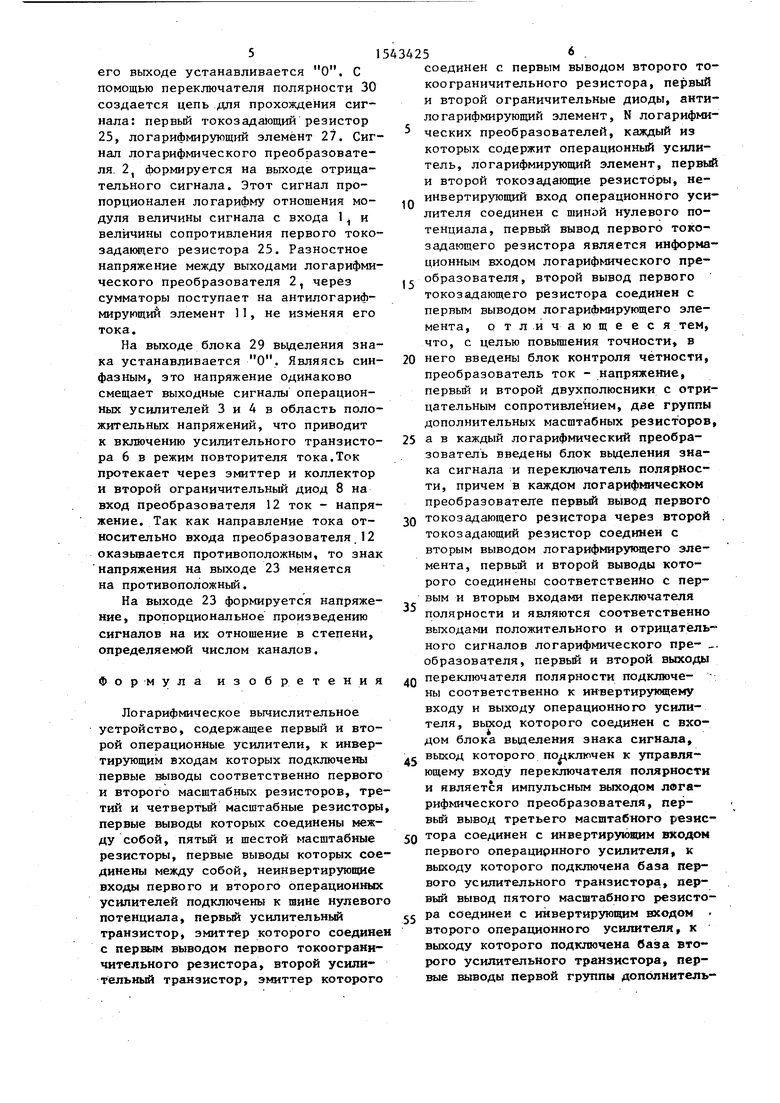

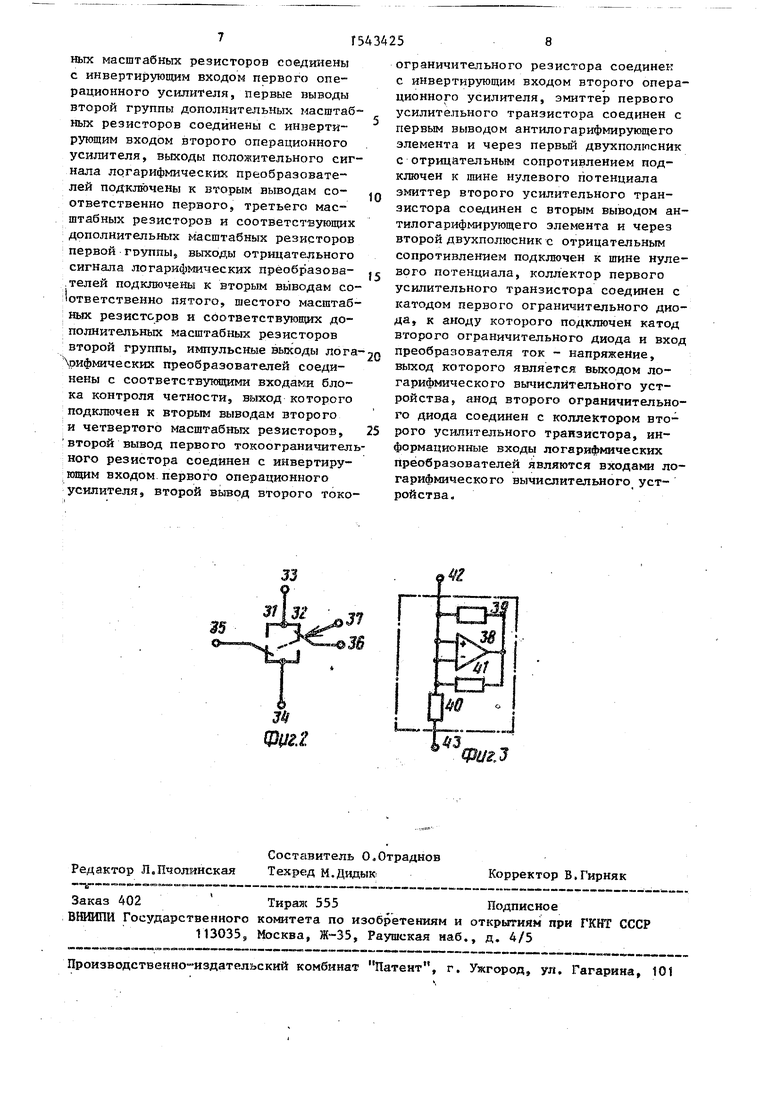

На фиг. 1 изображена функциональная схема логарифмического вычислительного устройства; на фиг. 2 и 3 - функциональные схемы переключателя полярности и двухполюсника с отрицательным сопротивлением.

Устройство содержит входы Ц ,..., IN, логарифмические преобразователи 2,...,2N, первый 3 и второй 4 операционные усилители, первый 5 и второй

6усилительные транзисторы, первый

7и второй 8 ограничительные диоды, первый 9 и второй 10 двухполюсники с отрицательным сопротивлением, анти- логарифмирующий элемент 11, преобразователь 12 ток - напряжение, блок

13 контроля четности, с первого по шестой масштабные резисторы 14-19, первый 20 и второй 21 токоограничи- тельные резисторы, шииу 22 нулевого потенциала, выход 23, первую группу дополнительных масштабных резисторов 24,,... ,24(W.jj, вторую группу дополни- тельных масштабных резисторов 24(м.3ц,, ...247(М,Э), первый 25 и второй 26 токоэадаюшие резисторы, логарифмирующий элемент 27, операционный усилитель 28, блок ,29 выделения знака сигнала, переключатель 30 полярности, первый 31 и второй 32 переключатели, первый 33 и второй 34 входы , , первый 35 и второй 36 выходы, управляющий вход 37, операционный усили- тель 38, первый 39, второй 40 и третий 41 масштабные резисторы и первый 42 и второй 43 выводы.

Логарифмическое вычислительное устройство работает следующим образом

Предположим, что работает один сквозной канал, состоящий из логарифмического преобразователя 2,, сумматора, образованного первым операционным усилителем 3 с соответствующими масштабными резисторами, блока 13 контроля четности, в качестве которого можно использовать, например, постоянное запоминающее устройство, выходного антилогарифмического узла, состоящего из усилительных транзисторов 5 и 6, ограничительных диодов 7 и 8, двухполюсников 9 и 10 с отри

jg

J5

jn

25 Зо ,, 40

.г .

50

55

цательным сопротивлением и антилога- рифмирующего элемента II. .

При наличии на в:соде 1, положительного сигнала на выходе блока 29 выделения знака формируется 1, на выходе положительного сигнала логарифмического преобразователя 2, формируется напряжение, пропорциональное логарифму отношения сигнала с входа 1, и величины сопротивления второго токозадающего резистора 26. На выходе отрицательного сигнала логарифмического преобразователя 2, напряжение практически равно нулю. Напряжение с этих выходов логарифмического преобразователя 2, инвертируется первым сумматором на первом операционном усилителе 3 и вторым сумматором на втором операционном усилителе 4 и к антилогариф- мирующему элементу 11 прикладывается разность напряжений с первого и второго выходов. Ток антилогарифмирующе- го элемента 11 является антилогарифмом от логарифма отношения, т.е. пропорционален отношению сигнала с входа 1ч к величине сопротивления второго токозадающего резистора 26.

Усилительные транзисторы 5 и 6 и ограничительные диоды 7 и 8 служат для передачи этого тока на вхс$д преобразователя 12 ток - напряжение. Так, для получения положительного напряжения на выходе 23 при инвертирующем преобразователе 12 ток - напряжение с выхода блока 13 контроля четности на операционные усилители 3 и 4 через масштабные резисторы 17 И 15 подается 1. Поступая одновременно на операционные усилители 3 и 4, это напряжение не изменяет ток антилогарифмирующего элемента 11, но вызывает отрицательное смещение на выходах этих усилителей, что приводит к включению первого усилительного транзистора 5 в режим повторителя тока. Ток протекает через эмиттер и коллектор усилительного транзистора 5, ограничительный диод 7 на вход преобразователя 12 ток - напряжение. Паразитную утечку через первый токоограннчительный резистор 20 компенсирует первый двухполюсник с отрицательным сопротивлением 9.

При изменении полярности сигнала на входе Ц на отрицательную на выходе операционного усилителя 28 также изменяется знак, что регистрируется блоком 29 выделения знака и на

его выходе устанавливается О. С помощью переключателя полярности 30 создается цепь для прохождения сигнала: первый токозадающий резистор 25, логарифмирующий элемент 27. Сигнал логарифмического преобразователя 2t Лорнируется на выходе отрицательного сигнала. Этот сигнал пропорционален логарифму отношения модуля величины сигнала с входа 11 и величины сопротивления первого токо- задающего резистора 25. Разностное напряжение между выходами логарифмического преобразователя 2, через сумматоры поступает на антилогариф- мирующий элемент 11, не изменяя его тока.

На выходе блока 29 выделения знака устанавливается О. Являясь синфазным, это напряжение одинаково смещает выходные сигналы операционных усилителей 3 и 4 в область положительных напряжений, что приводит к включению усилительного транзистора 6 в режим повторителя тока.Ток протекает через эмиттер и коллектор и второй ограничительный диод 8 на вход преобразователя 12 ток - напряжение. Так как направление тока относительно входа преобразователя 12 оказывается противоположным, то знак напряжения на выходе 23 меняется на противоположный.

На выходе 23 формируется напряжение, пропорциональное произведению сигналов на их отношение в степени, определяемой числом каналов.

Формула изобретения

Логарифмическое вычислительное устройство, содержащее первый и второй операционные усилители, к инвертирующим входам которых подключены первые выводы соответственно первого и второго масштабных резисторов, третий и четвертый масштабные резисторы первые выводы которых соединены между собой, пятьй и шестой масштабные резисторы, первые выводы которых соединены между собой, неинвертирующие входы первого и второго операционных усилителей подключены к шине нулевого потенциала, первый усилительный транзистор, эмиттер которого соединен с первым выводом первого токоогранн- чительного резистора, второй усилительный транзистор, эмиттер которого

0

соединен с первым выводом второго то- коограничительного резистора, первый и второй ограничительные диоды, антилога рифмирующий элемент, N логарифмических преобразователей, каждый из которых содержит операционный усилитель, логарифмирующий элемент, первый и второй токозадающие резисторы, неинвертирующий вход операционного усилителя соединен с шиной нулевого потенциала, первый вывод первого токо- задающего резистора является информационным входом логарифмического пре, образователя, второй вывод первого токозадающего резистора соединен с первым выводом логарифмирующего элемента, отличающееся тем, что, с целью повышения точности, в

0 него введены блок контроля четности, преобразователь ток - напряжение, первый и второй двухполюсники с отрицательным сопротивлением, две группы дополнительных масштабных резисторов,

5 а в каждый логарифмический преобразователь введены блох выделения знака сигнала и переключатель полярности, причем в каждом логарифмическом преобразователе первый вывод первого

о токозадающего резистора через второй токозадающий резистор соединен с вторым выводом логарифмирующего элемента, первый и второй выводы которого соединены соответственно с первым и вторым входами переключателя полярности и являются соответственно выходами положительного и отрицательного сигналов логарифмического пре- . образователя, первый и второй выходы

Q переключателя полярности подключены соответственно к инвертирующему входу и выходу операционного усилителя, выход которого соединен с входом блока выделения знака сигнала,

с выход которого подключен к управляющему входу переключателя полярности и является импульсным выходом логарифмического преобразователя, первый вывод третьего масштабного резисQ тора соединен с инвертирующим входом первого операцирнного усилителя, к выходу которого подключена база первого усилительного транзистора, первый вывод пятого масштабного резистос ра соединен с инвертирующим входом второго операционного усилителя, к выходу которого подключена база второго усилительного транзистора, первые выводы первой группы дополнитель5

ных масштабных резисторов соединены с инвертирующим входом первого операционного усилителя, первые выводы второй группы дополнительных масштабных резисторов соединены с инвертирующим входом второго операционного усилителя, выходы положительного сигнала логарифмических преобразователей подключены к вторым выводам соответственно первого, третьего масштабных резисторов и соответствующих дополнительных масштабных резисторов первой группы, выходы отрицательного сигнала логарифмических преобразователей подключены к вторым выводам со- ответственно пятого, шестого масштабных резисторов и соответствующих дополнительных масштабных резисторов второй группы, импульсные выходы логаХоифмических преобразователей соединены с соответствующими входами блока контроля четности, выход которого подключен к вторым выводам второго и четвертого масштабных резисторов, второй вывод первого токоограничитель нрго резистора соединен с инвертирующим входом первого операционного усилителя, второй вывод второго токо

0

п

5

5

ограничительного резистора соединен с инвертирующим входом второго операционного усилителя, эмиттер первого усилитепьного транзистора соединен с первым выводом антилогарифмирующего элемента и через первый двухполюсник с отрицательным сопротивлением подключен к шине нулевого потенциала эмиттер второго усилительного транзистора соединен с вторым выводом антилогарифмирующего элемента и через второй двухполюсник с отрицательным сопротивлением подключен к шине нулевого потенциала, коллектор первого усилительного транзистора соединен с катодом первого ограничительного диода, к аноду которого подключен катод второго ограничительного диода и вход преобразователя ток - напряжение, выход которого является выходом логарифмического вычислительного устройства, анод второго ограничительного диода соединен с коллектором второго усилительного транзистора, информационные входы логарифмических преобразователей являются входами логарифмического вычислительного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Вычислительное устройство | 1987 |

|

SU1462364A1 |

| Множительно-делительное устройство | 1987 |

|

SU1543426A1 |

| Среднеквадратический преобразователь | 1985 |

|

SU1275302A1 |

| Аналоговое логарифмическое вычислительное устройство | 1982 |

|

SU1095198A1 |

| Вычислительное устройство | 1987 |

|

SU1539798A1 |

| Четырехквадратное множительно-делительное устройство | 1987 |

|

SU1474686A1 |

| Аналоговое логарифмическое вычислительное устройство | 1983 |

|

SU1137486A2 |

| Логарифмический усилитель | 1980 |

|

SU896636A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности. Логарифмическое вычислительное устройство содержит логарифмические преобразователи 2, первый и второй операционные усилители 3 и 4, первый и второй усилительные транзисторы 5 и 6, первый и второй ограничительные диоды 7 и 8, первый и второй двухполюсники с отрицательным сопротивлением 9 и 10, антилогарифмирующий элемент 11, преобразователь ток-напряжение 12, блок контроля четности 13, шесть масштабных резисторов 14-19, два токоограничительных резистора 20 и 21, шину нулевого потенциала 22, две группы дополнительных масштабных резисторов 24, два токозадающих резистора 25 и 26, логарифмирующий элемент 27, операционный усилитель 28, блок выделения знака сигнала 29, переключатель полярности 30. Работа устройства основана на реализации логарифмического алгоритма вычисления произведения и отношения сигналов в степени. 3 ил.

| Справочник по нелинейным схемам/Под ред | |||

| Д.Шейнголда. | |||

| М.: Мир, 1977, с | |||

| Дальномер | 1922 |

|

SU379A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР | |||

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-15—Публикация

1987-05-29—Подача