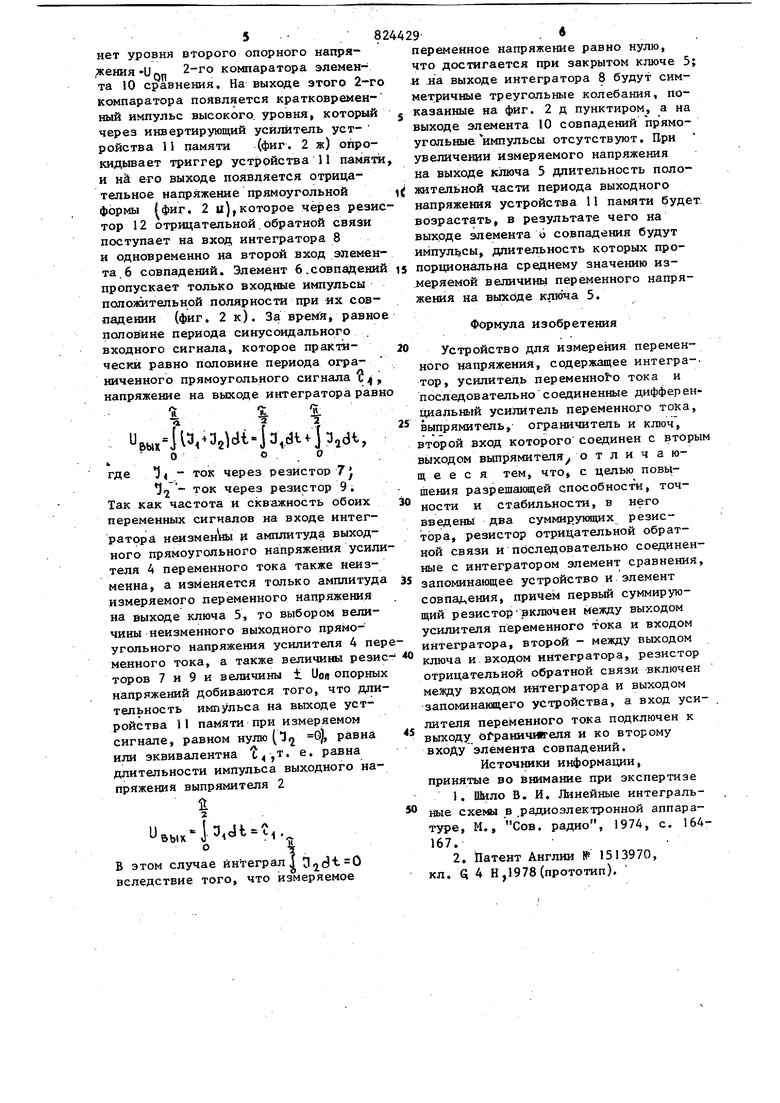

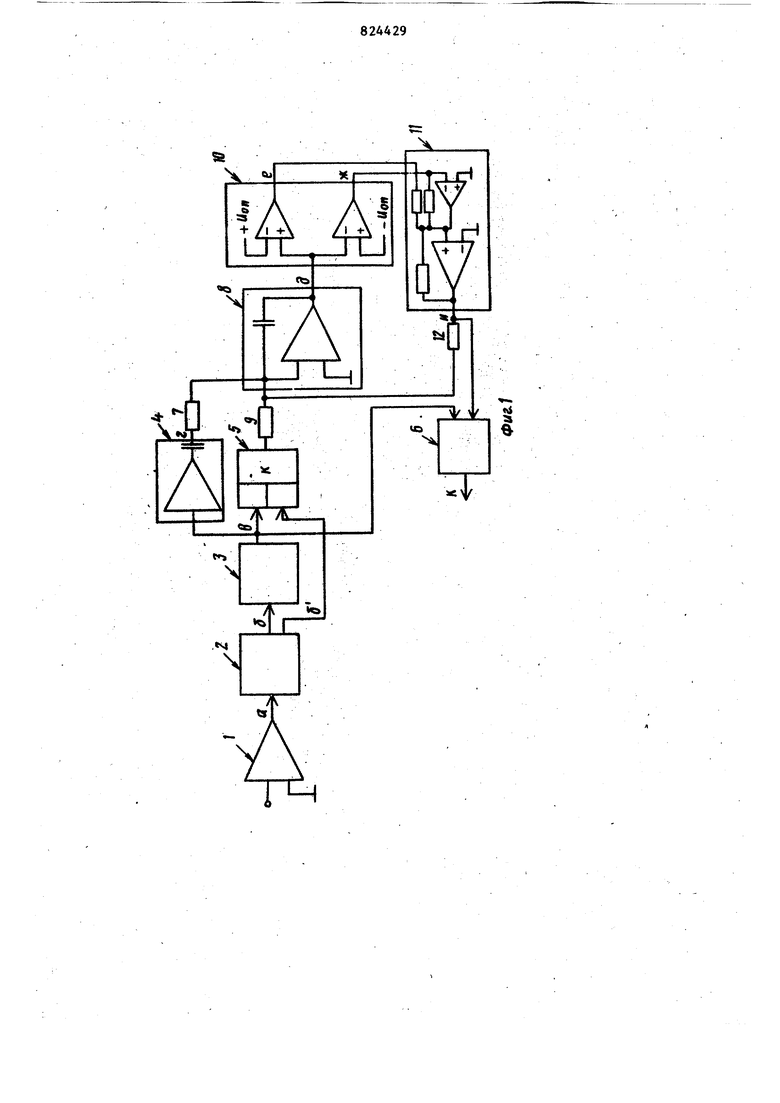

54), УСТРОЙСТВО ДЛЯ Й ЕРЕНИЯ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ 3- - . тегратором элемент сравнения, за поминающее устройство и элемент совпадения, причем первый суммирующий резистор включен между выходом усилителя переменного тока и входом интегратора, второй - между выходом ключа и входом интегратора, резистор отрицательной обратной связи включен между входом интегратора и выходом з поминающего устройства, а вход усилителя переменного тока подключен к выходу ограничителя и ко второму вхо ду элемента совпадения. На фиг. 1 изображена функциональная электрическая схема устройства; на фиг. 2 - временная диаграмма его работы. Устройство состоит из дифференциа ного усилителя выход которого подключен ко входу выпрямителя 2, выход которого соединен со входом ограничи теля 3. Выход ограничителя 3 подключен ко входу усилителя 4 переменного тока, ко входу возбуждения ключа 5, другой вход которого соединен с выходом выпрямителя и объединенным входом компараторов элемента 6 совпадений. Выход усилителя через первый суммирующий резистор 7 подалючен ко входу интегратора 8, к которому через второй суммируклций резистор 9 подключен выход.ключа 5. Выход интегратора 8 подключен к одному из входов элемента 10 сравнения,,на другие входы которого подключены два стабилизированных опорных напряжения . Выходы элемента 10 сравнения подключены ко входу устройства 11 памяти, выход которого соединен с резистором 12 отрицательной обратной связ и с рдйим из входов элемента 6 совпадения. Резистор 12 отрицательной обратной связи подключен также ко входу интегратора 8. Устройство работает следукицим образом. На вход дифференциального усилителя 1 переменного тока поступает измеряемый синусоидальный сигнал (ил другой формы неизменной частоты {фиг. 2 а) где усиливается и подается на вход выпрямителя 2, с выхода которого (фиг. 2 б)поступает на вход усилителя-ограничителя 3 и одновременно на вход ключа 5 (фиг. 2 б). Усиленный и ограниченный выходной си нал ограничителя 3 (фиг. 2 в) неизмен 94 ной амплитуды и скважности подается одновременно на взод усилителя 4 переменного тока, на вход возбуждения ключа 5 и на один из входов элемента 6 совпадений. Выходной сигнал усилителя тапа неанщ (без постоянной с х:тавляющей со скважностью Q 2 и неизменной амплитуды) поступает на вход интегратора 8 через суммируюпщй резистор 7 (фиг. 2 г). Одновременно в течение положительной части полупериода на вход интегратора 8 поступает второй измеряемый сигнал с выхода KjB04a 5 через суммирующий резистор , 2 бХв течение положи- тельного полупериода измеряемого сигнала оба сигнала, поступающие на. вход интегратора 8 (отрицательные сигналы) суммируются. В результате на выходе интегратора 8 возникает пилообразное напряжение с малым временем нарастания, соответствующее отрицательному полупериоду, и с большим. временем спада, соотвутствующим положительному полупериоду.(фиг.2 д) Так как с1мплитуда и скважность 042).. выходного сигнала усилителя неизменны, то крутизна нарастания пилообразного сигнала в течение положительного полупериода измеряемого сигнала.пропорциональна измеряемому сигналу с выхода ключа 5. Выходной сигнал интегратора 8 п.ос.тупает на объединенный вход компараторов элемента 10 сравнения, на другие входы этих компараторов подаются положительные 1) on и отрицательные -Uoti опорные и стабилизированные напряжения постоянного тока. Эти напряжения показаны на фиг. 2 д в виде двух прямых линий, параллельных оси времени. Когда выходной сигнал интегратора 8, нарастая в положительном направлении, достигает уровня опорного напряжения + UQлjвepxнйй компаратор элемента 10 сравнения открывается и на его выходе появляется сигнал высокого уровня, соответствующий уровню логической фнг.1е) который опрокидывает триггер устройства памяти, в рез:ультате к резистору 12 отрицательной обратной связи ко 2-му входу элемента 6 совпадений прикладывается положительный сигал прямоугольной формы (фиг.2 и), и игнал на выходе интегратора 8 наинает нарастать в отрицательном наравлении до тех пор, пока не достигнет уровня второго опорного напряpKeHHH«U/4f, 2-го компаратора элемента 10 сравнения. На выходе этого 2компаратора появляется кратковремен ный импульс высокого, уровня, которы через инвертирующий усилитель устройства П памяти (фиг. 2 ж) опро кидывает триггер устройства 11 памя и н1 его выходе появляется отрицательное напряжение прямоугольной формы (фиг. 2 и),которое через рез тор 12 отрицательной.обратной связи поступает на вход интегратора 8 и одновременно на второй вход элеме та. 6 совпадений. Элемент 6,совпадени пропускает только входные импульсы положительной полярности при их сов падении (фиг. 2 к). За время, равн половине периода синусоидального входного сигнала, которое практачески равно половине периода ограниченного прямоугольного сигнала напряжение на выходе интегратора рав % I Гf l3,02)cii-Ja,),dt, оо где Тt ток через резистор 7J J2 - ток через резистор 9. Так как частота и скважность обоих переменных сигналов на входе интегратора неизмен л и амплитуда выходного прямоугольного напряжения усил теля 4 переменного тока также неизменна, а изменяется только амплитуд измеряемого переменного напряжения на выходе ключа 5, то выбором величины неизменного выходного прямоугольного напряжения усилителя 4 пе менного тока, а также величины рези торов 7 и 9 и величины i: Uon опорны напряжений добиваются того, что дли тельность импульса на выходе устройства 11 памяти при измеряемом сигнале, равном нулю(12 ) или эквивалентна t,T. е. равна длительности импульса выходного напряжения выпрямителя 2 l.dt в этом случае йнтеграл J Ovj. вследствие того, что измеряемое переменное напряжение равно нулю, что достигается при закрытом ключе 5; и .на выходе интегратора 8 будут симметричные треугольные колебания, показанные на фиг. 2 д пунктиром, а на выходе элемента 10 совпадений прямоугольные импульсы отсутствуют, Ери увеличении измеряемого напряжения на выходе ключа 5 длительность положительной части периода выходного напряжения устройства 11 памяти будет возрастать, в результате чего на выходе элемента о совпадения будут импульсы, длительность которых пропорциональна среднему значению измеряемой величины переменного напряжения на выходе ключа 5. Формула изобретения Устройство для измерения переменного напряжения, содержащее интегра-тор, усилитель переменно о тока и последовательносоединенные диффер енциальный усилитель переменного тока, выпрямитель,- ограничитель и ключ , второй вход которого соединен с вторым выходом выпрямителя отличающееся тем, что, с целью повышения разрешакядей способности, точности и стабильности, в него введены два суммирукмцих резистора, резистор отрицательной обратной связи и последовательно соединенные с интегратором элемент сравнения, запоминающее устройство и элемент совпадения, причем первый суммирующий резисторвключен между выходом усилителя переменного тока и входом интегратора, второй - между выходом ключа и-ВХОДОМ интегратора, резистор отрицательной обратной связи -включен между входом интегратора и выходом запоминающего устройства, а вход уси- . лителя переменного тока подключен к выходу (эГраш1Ч1«геля и ко второму вхоДу элемента совпадений. Источники информации, принятые во внимание при экспертизе 1.Шило В. И, Линейные интегральные схемы в .радиоэлектронной аппаратуре, М., Сов. радио, 1974, с. 164167. 2.Патент Англии № 1513970, кл. Q 4 Н,1978 (прототип).

а А

А А

| название | год | авторы | номер документа |

|---|---|---|---|

| Компаратор | 1979 |

|

SU813757A1 |

| Преобразователь сигнала | 1979 |

|

SU813762A1 |

| ШИРОКОДИАПАЗОННЫЙ ВОЛОКОННО-ОПТИЧЕСКИЙ ИЗМЕРИТЕЛЬ УГЛОВОЙ СКОРОСТИ | 2002 |

|

RU2227272C2 |

| Устройство для направленной защиты от однофазного замыкания на землю в сети с изолированной нейтралью | 1981 |

|

SU1034115A1 |

| Измерительный преобразователь активной мощности | 1989 |

|

SU1659890A1 |

| Устройство для управления частотно-регулируемым асинхронным электроприводом | 1991 |

|

SU1793527A1 |

| Преобразователь угла поворота вала в частоту следования импульсов | 1987 |

|

SU1471311A1 |

| Устройство для преобразования напряжения переменного тока в код | 1990 |

|

SU1795543A1 |

| Устройство для контроля пламени | 1983 |

|

SU1129467A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ НАПРЯЖЕНИЯ ПЕРЕМЕННОГО ТОКА В КОД | 2001 |

|

RU2195767C1 |

Фиг. 2

Авторы

Даты

1981-04-23—Публикация

1979-07-06—Подача