(54) РЕВЕРСИВНЫЙ СЧЕТЧИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный счетчик | 1982 |

|

SU1066039A2 |

| Счетчик в коде либау-крейга | 1977 |

|

SU660264A1 |

| Счетчик в коде Грея | 1984 |

|

SU1202050A1 |

| Регистр сдвига | 1977 |

|

SU705522A1 |

| Счетное устройство | 1980 |

|

SU953741A1 |

| Регистр | 1979 |

|

SU822367A1 |

| Распределитель | 1981 |

|

SU966902A1 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Двухтактный реверсивный счетчик | 1985 |

|

SU1297223A1 |

1

изобретение относится к построению устройств цифровой вычислитель ной техники и дискретной автоматики.

Реверсивные счетчики с последовательным переносом широко применяются в различных цифровых устройствах. Они обеспечивают как сумми1 ук1ций, так и вычитающий счет числа импульсов и отличаются небольшими аппаратурными затратами по сравнению с реверсивными счетчиками с параллельным переносом.

Известен реверсивный счетчик с последовательным переносом, содержащий счетный вход, два управляющих входа, счетные разрядь и межразрядные коммутаторы, построенные на трех логических элементаз И-НЕ ll.

Извесген также реверсивный счетчик, содержащий вход, первь1й и второй управляющие входы и разряды, каждый из которых содержит первый , второй и .третий RS-триггеры на элементах И-НЕ, второй выход первбго RS-триггера каждого разряда соединен с S-входом третьего RS-триггера того же разряда, второй выход второго RSтриггера соединен с R-входом третьего RS-триггера,- второй выход третье.го RS-триггера соединен с S-входом

второго RS-триггера, первый выход которого ооединен с S-входом первого RS-триггера, а .каждый разряд, кроме первого, содержит также первый и второй элементы И-НЕ, выход первого элемента И-НЕ соединен с S-входами первого и третьего RS-триггеров того же разряда, выход второго элемента И-НЕ соединен с R-входом третьего и

S-входом «второго RS-триггеров того же разряда, а первый выход первого RS-триггера соединен со входом первого элемента И-НЕ того же разряда, первый выход второго RS-триггера

соединен с входом второго элемента И-НЕ того же разряда, первый управляющий вход соединен с входами первых и вторых элементов И-НЕ, второй управляющий вход соединен с R-входами первого и второго RS-триггеров всех разрядов, кроме первого,, а ,счетный вход соединен с R-входами первого и второго триггеров первого | разряда, а первый выход третьего RSтриггера каждого разряда соединен со входами первого и второго элементов И-НЁ следующего разряда, второй выход третьего RS-триггера каждого разряда соединен с R-входами первого и второго RS-триггеров следующего разряда 2,

Недостатком известного счетчика являются относительно большие аппаратурные затраты.

Цель изобретения - снижение аппаратурных затрат.

Поставленн ая цель достигается тем, что в реверсивном счетчике, содержащем счетный вход, первый, второй управляющие входы и разряды, каждый из которых содеряйит первый, второй и третий RS-триггеры на элементах. И-НЕ второй выход первого RS-триггера каждого разряда соединен с S-входом третьего RS-триггера того же разряда, второй выход второго RS-триггера соединен с R-входом третьего RS-триггера, второй выход третьего RS-триггера соединен с S-входом второго RSтриггера, первый выход которого соединен с S-входом первого RS-триггера а каждый четный разряд содержит также первый и второй элементы И-НЕ, выход первого элемента И-НЕ соединен с $-вх6дами первого и третьего RSтриггеров того же разряда, выход второго элемента И-НЕ соединен с R-входом третьего и S-входом второго RSтриггеров того же разряда, а первый выход первого RS-триггера соединен со входом первого элемента И-НЕ того же разряда, первый выход второго RSтриггера соединен с входом второго элемента И-НЕ того же разряда, первый управляющий вход соединен с входами первых и вторых элементов И-НЕ, второй управляющий вход соединен с R-входами первого и второго RS-триггеров четных разрядов, а счетный вход соединен с R-входами первого и второго RS-триггеров первого разряда второй выход первого RS-триггера каждого нечетного разряда соединен с R-входами первого и второго RS-триггеров следунвдего разряда, второй выход второго RS-триггера каткдого не четного разряда соединен со входами первого и второго элементов И-НЕ следующего разряда, выход первого элемента И-НЕ кажцого четного разряда соединен с R-входами первого и второго RS-триггеров следующего разряда, а второй выход второго RS-триггера каяадого четного разряда соединен с R-входами первого и второго RS-триггеров следукядего разряда.

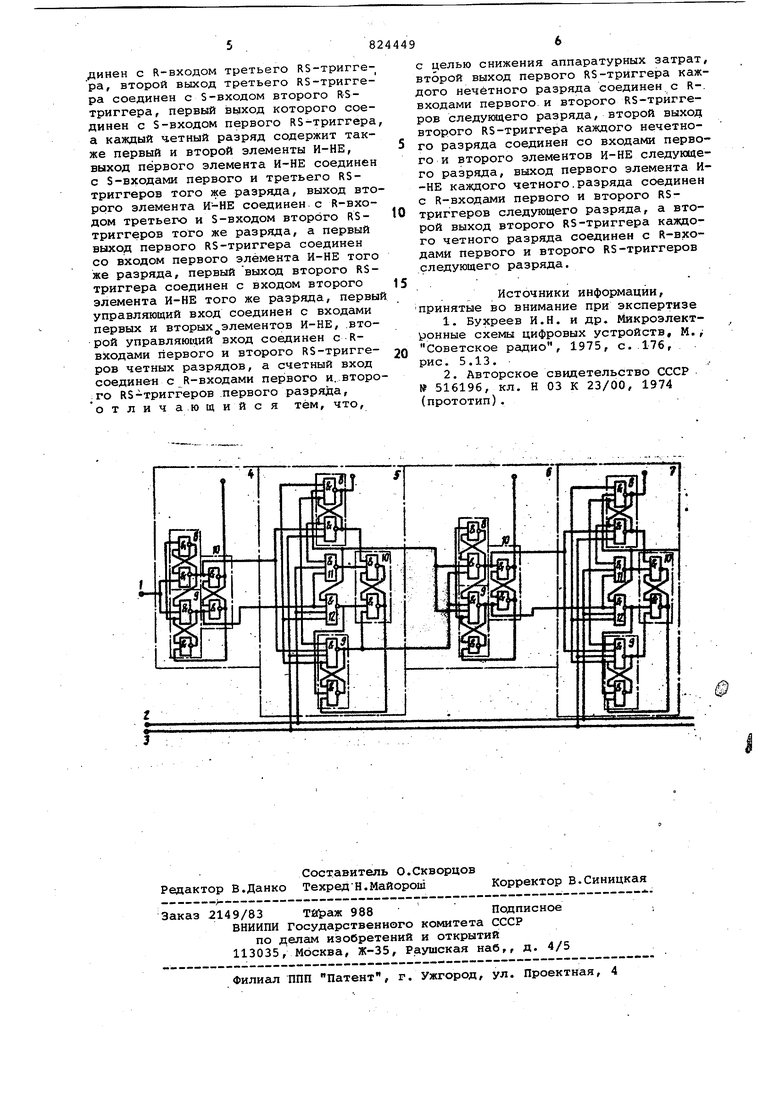

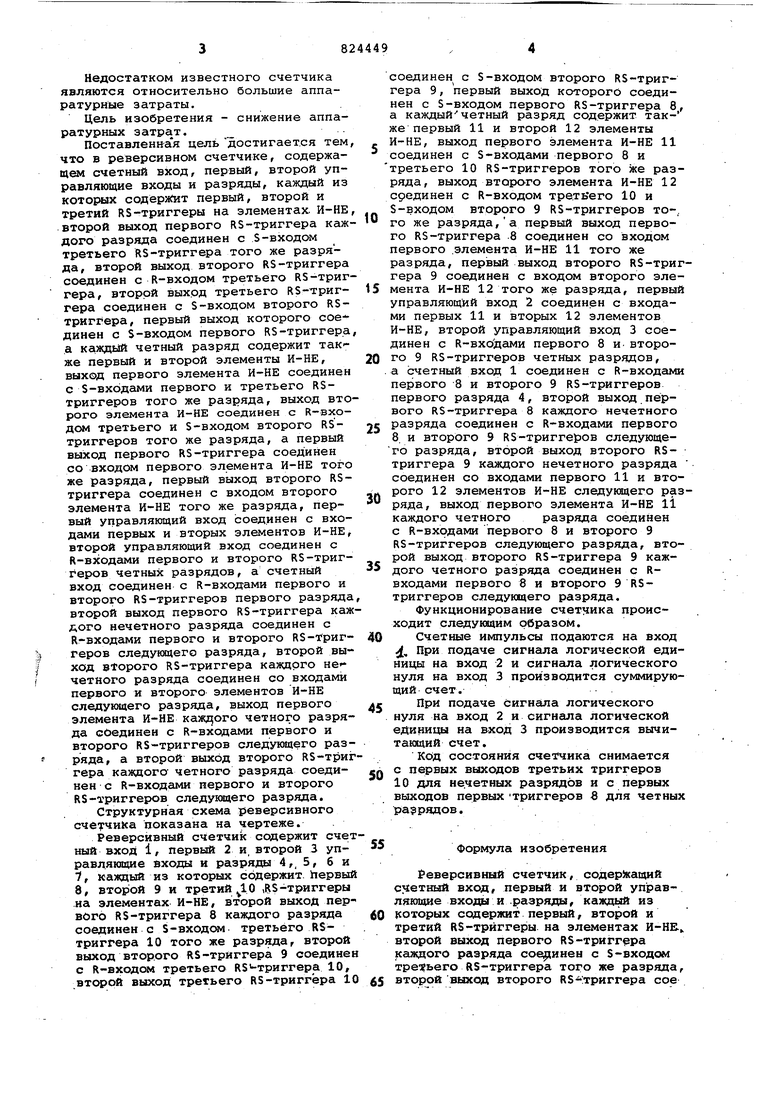

Структурная схема реверсивного счетчика показана на чертеже.

Реверсивный счетчик содержит счетный вход 1, первый 2 и, второй 3 управляющие входы и разряды 4,, 5, б и , каждый из которых содержит 11ервый 8, второй 9 и третий 10 ,RS-триггеры на элементах И-НЕ, второй выход первого RS-триггера 8 каждого разряда соединен с $-вход 1 третьего RSтриггера 10 того же разряда, второй выход второго RS-триггера 9 соединен с R-входом третьего RS-триггера 10, второй выход третьего RS-триггера 10

соединен с S-входом второго RS-триггера 9, первый выход которого соединен с S-входом первого RS-триггера 8 а каждыйчетный разряд содержит также первый 11 и второй 12 элементы И-НЕ, выход первого элемента И-НЕ 11 соединен с S-входами первого В и третьего 10 RS-триггеров того же разряда, выход второго элемента И-НЕ 12 срединен с R-входом третьего 10 и S-входом второго 9 RS-триггеров то-, го же разряда,а первый выход первого RS-триггера 8 соединен со входом первого .элемента И-НЕ 11 того же разряда, первый выход второго RS-триггера 9 соединен с входом второго элемента И-НЕ 12 того же разряда, первый управляющий вход 2 соединен с входами первых 11 и вторых 12 элементов И-НЕ, второй управляющий вход 3 соединен с R-вxoi aми первого 8 и. второго 9 RS-триггеров четных разрядов, а счетный вход 1 соединен с R-входами первого 8 и второго 9 RS-триггеров первого разряда 4, второй выход первого RS-триггера 8 каждого нечетного разряда соединен с R-входами первого 8. и второго 9 RS-триггеров следующего разряда, второй выход второго RSтриггера 9 каждого нечетного разряда соединен со входами первого 11 и второго 12 элементов И-НЕ следукзщего разряда, выход первого элемента И-НЕ 11 каждого четного разряда соединен с R-входами первого 8 и второго 9 RS-триггеров следующего разряда, второй выход второго RS-триггера 9 каждого четного разряда соединен с Rвходами первого 8 и второго 9 RSтриггеров следующего разряда.

Функционирование счетника происходит следующим образом.

Счетные импульсы подаются на вход (, При подаче сигнала логической единицы на вход 2 и сигнала логического нуля на вход 3 производится суммирующий счет. . .

При подаче сигнала логического нуля на вход 2 и сигнала логической единицы на вход 3 производится вычитающий счет.

состояния счетчика снимается с первых выходов третьих триггеров 10 для нечетных разр;эдЬв и с первых выходов первых триггеров 8 для четных разрядов.

Формула изобретения

еверсивный счетчик, содер кащий счетный вход, первый и второй управляюише входы и .разряды, каждь1й из которых содержит первый, второй и третий RS-триггеры на элементах И-НЕ второй выход первого RS-триггера кааздого разряда соединен с S-входом третьего RS-триггера того же разряда, второй выход второго RS :тpиггepa сое

динен с R-входом третьего RS-триггера, второй выход третьего RS-триггера соединен с S-входом второго RSтриггера, первый звьаход которого соединен с S-входом первого RS-триггера а каждый четный разряд содержит также первый и второй элементы И-НЕ, выход первого элемента И-НЕ соединен с S-входами первого и третьего RSтриггеров того же разряда, выход второго элемента И-НЕ соединен с R-входом третьего и S-входом второго RSтриггеров того же разряда, а первый выход первого RS-триггера соединен со входом первого элемента И-НЕ того же разряда, первый выход второго RSтриггера соединен с входом второго элемента И-НЕ того же разряда, первы управляющий вход соединен с входами первых и вторых элементов И-НЕ, .второй управляющий вход соединен с Rвходами первого и второго RS-триггеров четных разр5здов, а счетный вход соединен с R-входами первого и.второго RS-триггеров первого разряда, отличающийся тем, что.

с целью снижения аппаратурных затрат, второй выход первого RS-триггера каждого нечётного разряда соединен с R-. входами первого.и второго RS-триггеров следукнцего разряда, второй выход второго RS-триггера каждого нечетного разряда соединен со входами первого и второго элементов И-НЕ следующего разряда, выход первого элемента И-НЕ каждого четного.разряда соединен с R-входами первого и второго RSтриггеров следующего разряда, а второй выход второго RS-триггера казедого четного разряда соединен с R-входами первого и второго RS-триггеров следующего разряда.

5

Источники информации, принятые во внимание при экспертизе

0 рис. 5.13.

Авторы

Даты

1981-04-23—Публикация

1979-07-13—Подача