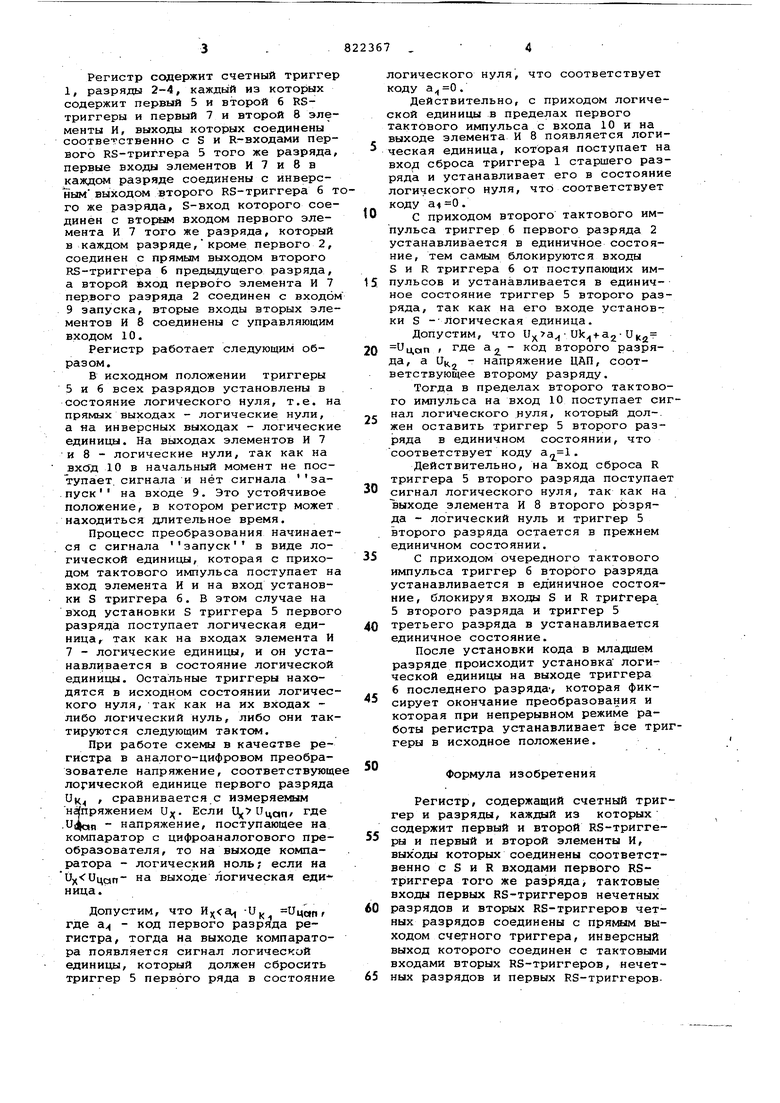

Изобретение относится к цифровой вычислительной технике и предназначено для использования в аналогоцифровых преобразователях. : Известен регистр последовательно приЗлижения, выполненный в интегральном исполнении, входящий в состав аналого-цифрового преобразовате ля ,и содержащий в каждом разряде пять логических узлов {l , Недостатком этого регистра является относительно высокая сложнос Известен также регистр, содержащий счетный триггер и разряды, каждый из которых содержит первый и второй RS-триггеры. и первый и второ элементы И, выходы которых соединен соответственно с S и R-входами первого RS-триггера того же разряда, тактовые входы первых RS-триггеров соединены с прямым выходом счет ного триггера, инверсный выход которого соединен с тактовыми входами вторых RS-триггеров 2. Недостатком этого регистра являе ся относительно низкое быстродействие . Цель изобретения - повышение быстродействия . Поставленная цель достигается тем, что в регистре, содержащем триггер и разряды, каждый из которых содержит .первый и второй RS-триггеры и первый и второй элементы И, выходы которых соединены сбо.тветственно с S и R входами первого RS-триггера того же разряда, тактовые входы первых RS-тритгеррв нечетных разрядой и вторых RS-триггеров четных разрядов соединены с прямым выходом счетного триггера , инверсный выход которого соединен с тактовыми входами вторых RS-триггеров нечетных разрядов и первых RS-триггеров четных разрядов, а первые входы элементов Ив каждом разряде соединены с инверсным выходом второго RS-триггера того же разряда, S-вход которого соединен с вторым входом первого элемента И того же разряда, который в каждом разряде, кроме первого, соединен с прямым выходом второго RS-i;pHrrepa предыдущего разряда, а второй вход первого элемента И первого разряда соединен с входом запуска, вторые входы вторых элементов .И соединены с управляющим входом. На чертеже показана структурная схема предлагаемого регистра.

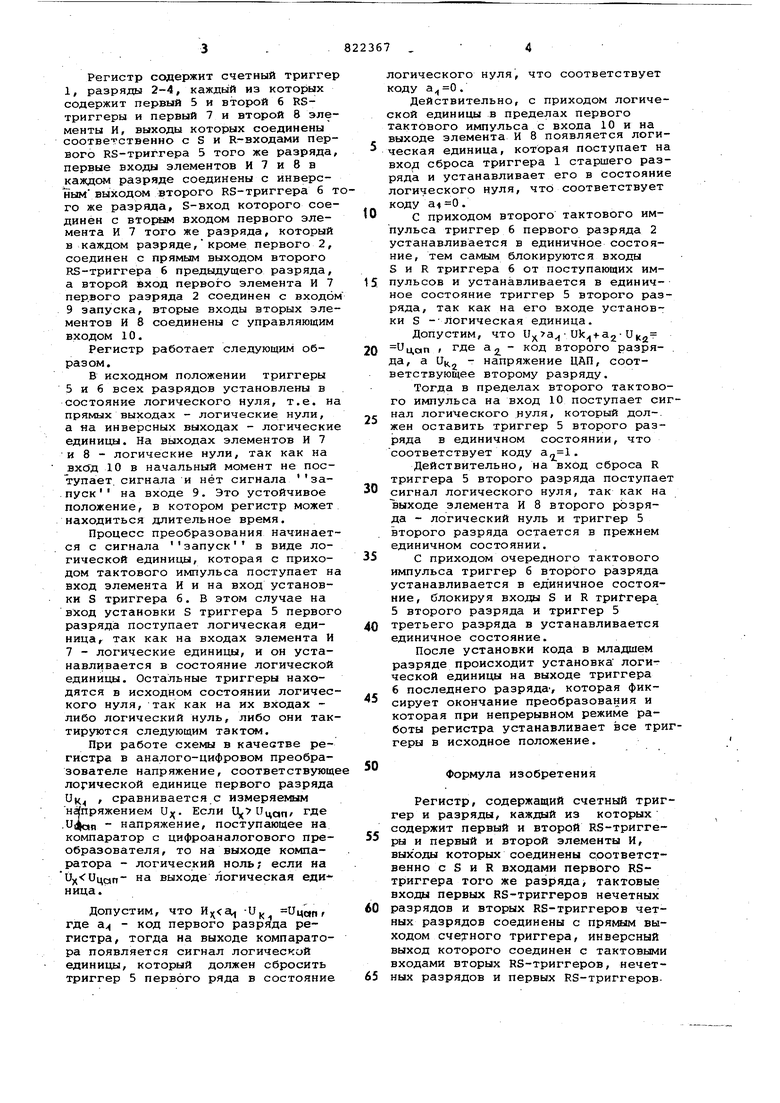

Регистр содержит счетный триггер 1, разряды 2-4, каждый из которых содержит первый 5 и второй 6 RSтриггеры и первый 7 и второй 8 элементы И, выходы которых соединены соответственно с S и R-входами первого RS-триггера 5 того же разряда, первые входы элементов И 7 и 8 в каждом разряде соединены с инверс 5ЫМвыходом второго RS-триггера б тго же разряда, S-вход которого соединен с входом первого элемента И 7 того же разряда, который в каждом разряде,кроме первого 2, соединен с прямым выходом второго RS-триггера б предыдущего разряда, а второй вход первого элемента И 7 первого разряда 2 соединен с входом 9 запуска, вторые входы вторых элементов И 8 соединены с управляющим входом 10.

Регистр работает следующим образом.

В исходном положении триггеры 5 и 6 всех разрядов установлены в состояние логического нуля, т.е. на прямых выходах - логические нули, а на инверсных выходах - логические единицы. На выходах элементов И 7 и 8 - логические нули, так как на вхсЗд 10 в начальный момент не поступает, сигнала и нет сигнала за.пуск на входе 9. Это устойчивое положение, в котором регистр может находиться длительное время.

Процесс преобразования начинается с сигнала запуск в виде логической единицы, которая с приходом тактового импульса поступает на вход элемента И и на вход установки S триггера б. В этом случае на вход установки S триггера 5 первого разряда поступает логическая единица, так как на входах элемента И 7 - логические единицы, и он устанавливается в состояние логической единицы. Остальные триггеры находятся в исходном состоянии логического нуля, так как на их входах либо логический нуль, либо они тактируются следующим так-гом,

При работе схемы в качестве регистра в аналого-цифровом преобразователе напряжение, соответствующе логической единице первого разряда UK г сравнивается с измеряемым напряжением U;. Если Ц( Пцап Яе .Uiloii, - напряжение, поступающее на компаратор с цифроаналогового преобразователя, то на выходе компаратора - логический ноль; если на на выходе логическая единица.

Допустим, что -и, ицапг где а - код первого разряда регистра, тогда на выходе компаратора появляется сигнал логической единицы, который должен сбросить триггер 5 первого ряда в состояние

логического нуля, что соответствует коду .

Действительно, с приходом логической единицы в пределах первого тактового импульса с входа 10 и на выходе элемента И 8 появляется логическая единица, которая поступает н вход сброса триггера 1 старшего разряда и устанавливает его в состояни логического нуля, что соответствует коду .

С приходом второго тактового импульса триггер б первого разряда 2 устанавливается в единичное состояние, тем самым блокируются входы В и R триггера б от поступающих импульсов и устанавливается в единичное состояние триггер 5 второго разряда, так как на его входе установки S -Логическая единица.

Допустим, что Уцап I где 3.2. второго разряда, а UK, - напряжение ЦАП, соответствующее второму разряду.

Тогда в пределах второго тактового импульса на вход 10 поступает синал логического нуля, который дол-. жен оставить триггер 5 второго разряда в единичном состоянии, что соответствует коду .

Действительно, на вход сброса R триггера 5 второго разряда поступае сигнал логического нуля, так как на выходе элемента И 8 второго розряда - логический нуль и триггер 5 второго разряда остается в прежнем единичном состоянии.

С приходом очередного тактового импульса триггер б второго разряда устанавливается в единичное состояние, блокируя входы S и R триггера

5второго разряда и триггер 5 третьего разряда в устанавливается единичное состояние.

После установки кода в младшем разряде происходит установка логической единицы на выходе триггера

6последнего разряда , которая фиксирует окончание преобразования и которая при непрерывном режиме работы регистра устанавливает все тригеры в исходное положение.

Формула изобретения

Регистр, содержащий счетный триггер и разряды, каждый из которых содержит первый и второй RS-триггеры и первый и второй элементы И, выходы которых соединены соответственно с S и R входами первого RSтриггера того же разряда, тактовые входы первых RS-триггеров нечетных разрядов и вторых RS-триггеров четных разрядов соединены с прямым выходом счетного триггера, инверсный выход которого соединен с тактовыми входами вторых RS-триггеров, нечетных разрядов и первых RS-триггеровчетных разрядов, о т л и ч а ю .щ и йс я тем, что, с целью повышения быстродействия, первые входы элементов И в каждом разряде соединены с инверсным выходом второго RS-триггера того же разряда, S-вход которого соединен с вторым входом первого элемента И того же .разряда, который в каждом разряде, кроме первогр, соединен с выходом второго RS-триггера предыдущего разряда, а

второй вход первого элемента И первого разряда соединен с входом запуска, вторые входы вторых элементов И соединены с управляющим входом .

Источники информации, принятые во внимание при экспертизе

1.Патент США 4083043, кл. 340-347, 1978.

2.Data Book Advanced Micro Devices, 1975, рис. 28 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Регистр последовательного приближения | 1981 |

|

SU1149791A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Регистр | 1979 |

|

SU860137A1 |

| Регистр | 1981 |

|

SU1024989A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

| Модульное устройство программного управления и контроля | 1990 |

|

SU1803905A1 |

| Устройство для контроля параллельного кода на четность | 1987 |

|

SU1413632A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 1996 |

|

RU2097774C1 |

Авторы

Даты

1981-04-15—Публикация

1979-06-27—Подача