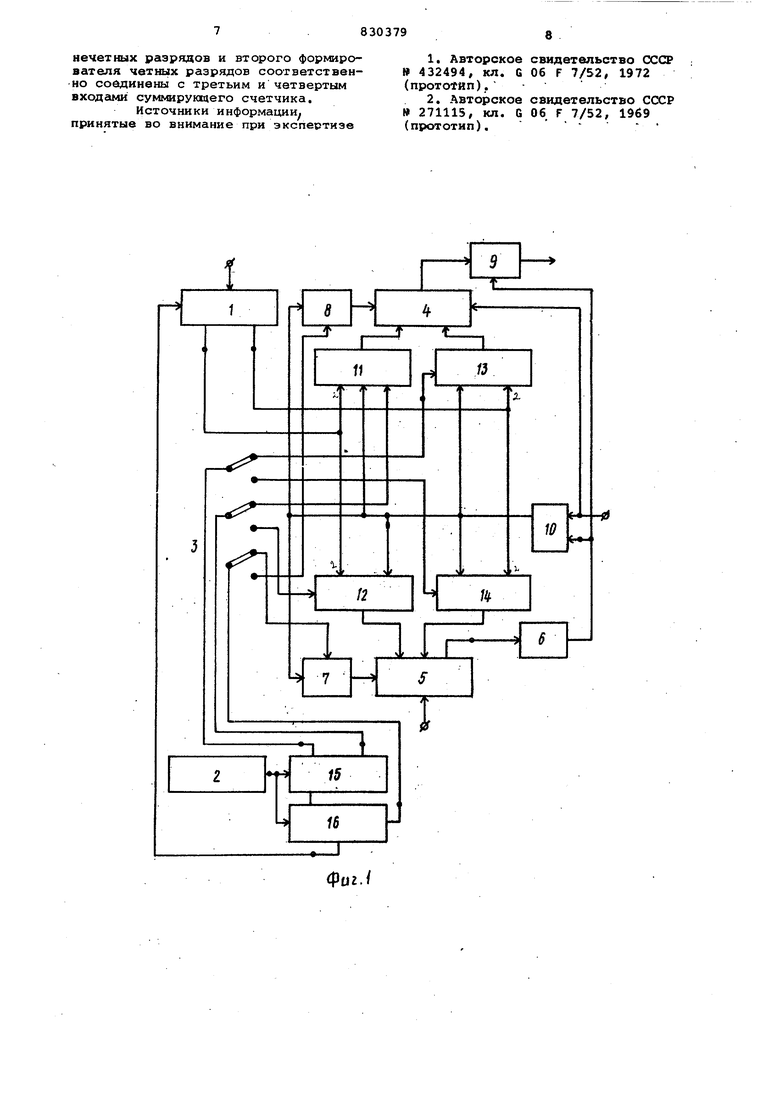

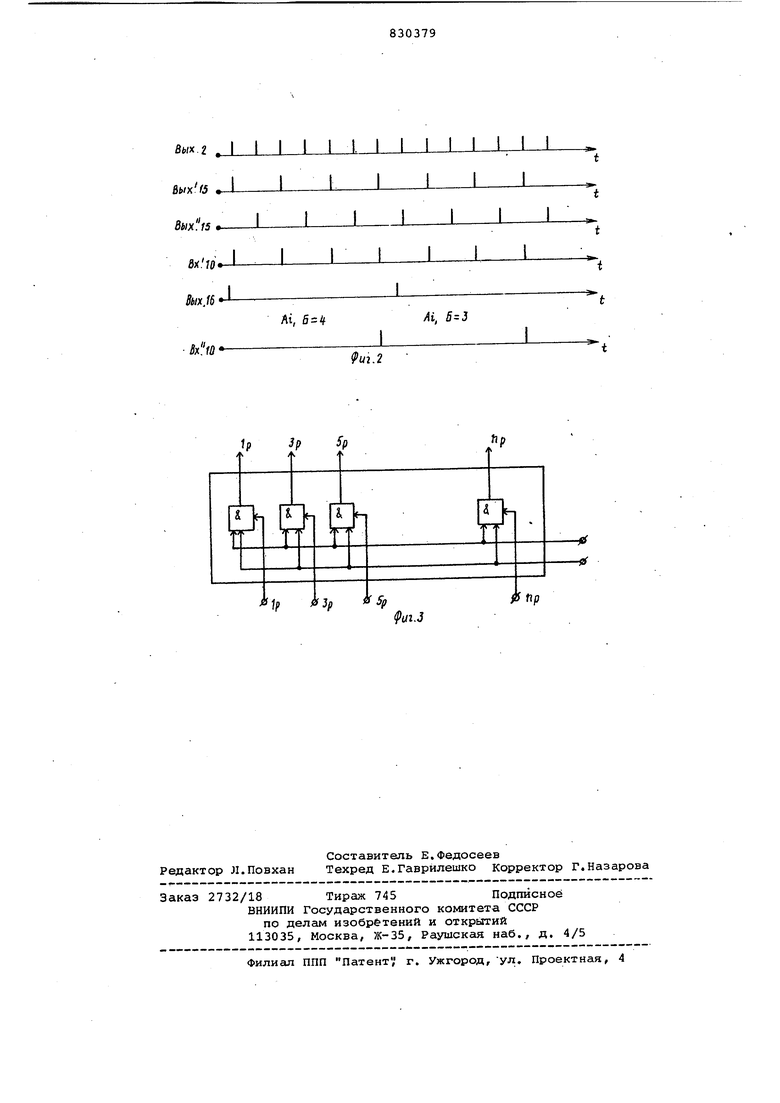

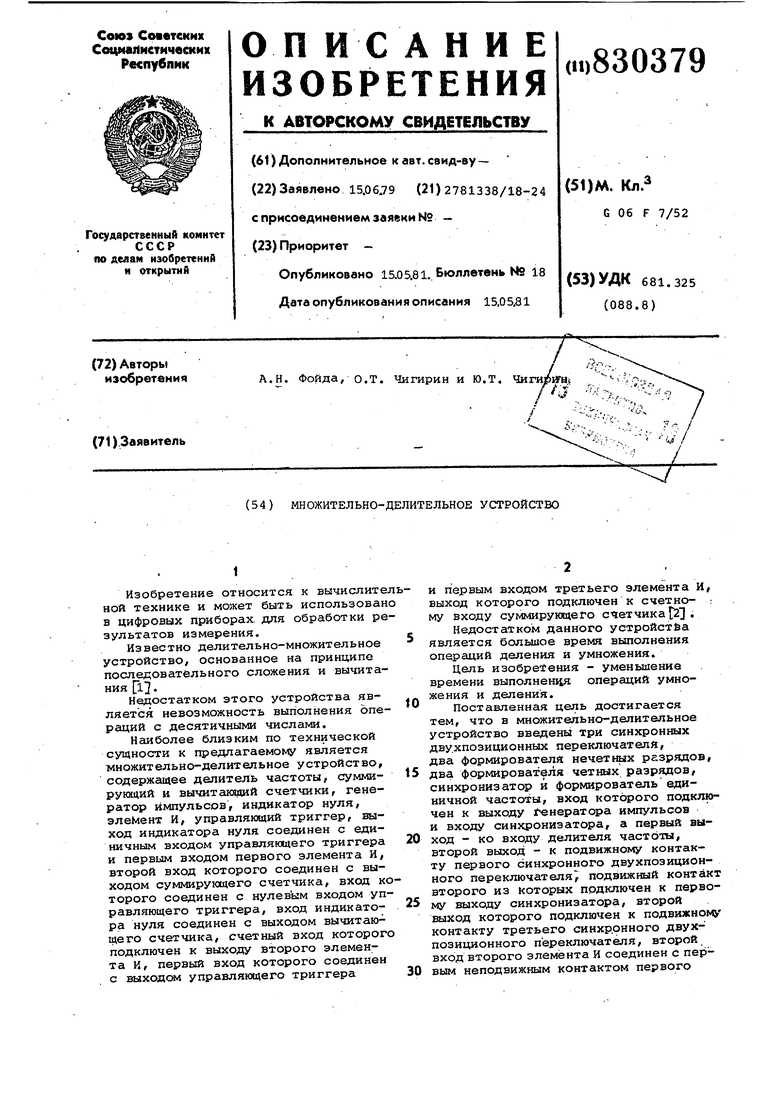

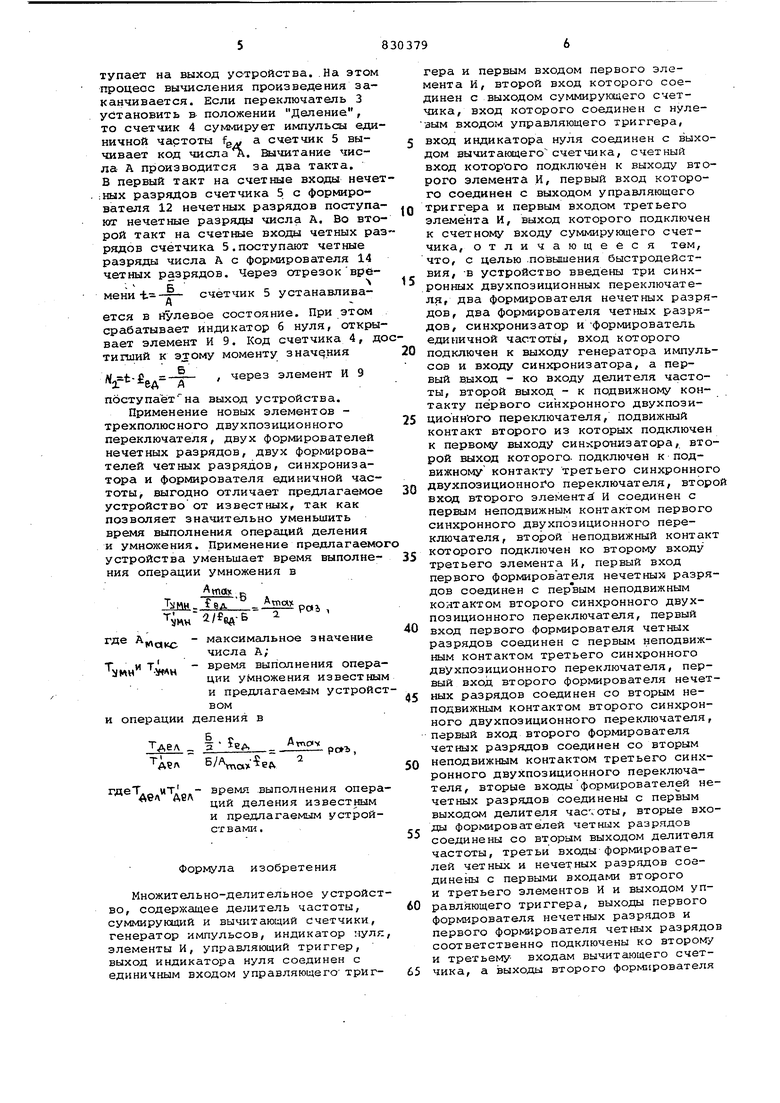

Изобретение относится к вычислите ной технике и может быть использован в цифровых приборах, для обработки ре зультатов измерения. Известно делительно-множительное устройство, основанное на принципе последовательного сложения и вычитания р.}. Недостатком этого устройства является невозможность выполнения операций с десятичными числами. Наиболее близким по технической сущности к предлагаемому является множительно-делительное устройство, содержащее делитель частоты, суммирунвдий и вычитаклдий счетчики, генератор импульсов, индикатор нуля, элемент И, управляющий триггер, выход индикатора нуля соединен с единичным входом управляющего триггера и первым входом первого элемента И/ второй вход которого соединен с выходом суммирующего счетчика, вход ко торого соединен с нулевым входом управляющего триггера, вход индикатора нуля соединен с выходом вычитающего счетчика, счетный вход которог подключен к выходу второго элемента И, первый вход которого соединен с выходом управляющего триггера и первым входом третьего элемента И, выход которого подключен к счетно- : му входу суммирующего с етчикар2 . Недостатком данного устройства является большое время выполнения операций деления и умножения. Цель изобретения - уменьшение времени выполненная операций умножения и деления. Поставленная цель достигается тем, что в множительно-делительное устройство введень три синхронных двухпозиционных переключателя, два формирователя нечетных разрядов, два формирователя четных разрядов, синхронизатор и формирователь единичной частоты, вход которого подключен к выходу генератора импульсов и входу синхронизатора, а первый выход - ко входу делителя частоты, второй выход - к подвижному контакту первого синхронного двухпоэиционного переключателя подвижный контакт второго из которых подключен к первому выходу синхронизатора, второй выход которого подключен к подвижному контакту третьего синхр.онного двухпозиционного переключателя, второй вход второго элемента И соединен с первым неподвижным контактом первого синхронного дву-х-познционного переключателя, второй неподвижный контакт которого подключён ко второму входу третьего элемента И, первый вход первого формирователя нечетных разрядов соединен с первым неподвиж ным контактом второго синхронного двухпозиционного переключателя, пер вый вход первого формирователя четных разрядов соединен с первым неподвижным контактом третьего синхро ного двухпозиционного переключателя, первый вход второго формирователя нечетных разрядов соединен со вторым неподвижным контактом вто рого синхронного двухпозиционного переключателя, первый входвторого формирователя четных разрядов соеди нен со вторым неподвижным контактом третьего синхронного двухпозиционного переключателя, вторые входы фо мирователей нечетных, разрядов соеди нены с первым выходом делителя част ты, вторые входы формирователей чет ных разрядов соединены со вторым вы ходом делителя частоты, третьи входы формирователей четных и нечетных разрядов соединены с первыми входам второго и третьего элементов И и вы ходом управляющего триггера-; выходы первого формирователя нечетных разр дов и первого формирователя четных, разрядов соответственно подключены ко второму и третьему входам вычитающего счетчика, а .выходы второго формирователя нечетных разрядов и в рого формироватешя четных разрядов соответствецно соединены с третьим и четвертым входами суммирующего сч чика. На фиг. 1 представлена блок-схем предлагаемого множительно-делительного устройства на фиг. 2 - времен ные диаграммы работы устройства на фиг. 3 - схема формирователя нечетных (четных) разрядов. Предлагаемое устройство состоит из делителя 1 частоты, генератора 2 импульсов, синхронных двухпозиционных переключателей 3,- суммируквдего счетчика 4, вычитакйцаго счетчика 5, игщикатора 6 нуля, элeмeнтoвV И 7-9 управляющего триггера 10, формирователей 11 и 12 нечетных разрядов, формирователей 13 и 14 четных разрядов, синхронизатора 15 и формирователя 16 единичной частоты-. Формирователь 11(12) нечет ных разрядов предоставляет группу трехвходовых схем И, первые входы которых соединены между собой, вторые входы также соединены между собой.. При поступлении управляющего сигнала на первые входы элементов И формирователя 11(12) из синхронизатора 15 через переключатель 3 и на вторые входы элементов И из управляющего, .триггера 10 на счетные входы нечетных разрядов счетчика 5(4) поступают сигналы из тех нечетных i разрядов делителя .1 частоты, которые находятся в единичном состоянии. Формирователь четных разрядов 13(14) представляет группу трехвходовых элементов И , первые входы которых соединены между собой, вторые входы также соединены между собой. При поступлении управляющего сигнала на первые входы элементов И формирователя 13(14) из син5фонизатора 15 через переключатель 3 и на вторые входы элементов И из управляющего триггера 10 на счетные входы четных разрядов счетчика 5(4) поступают сигналы из тех четных разрядов делителя 1 частоты, которые находятся в единичном состоянии. Устройство работает следующим образом. На вход делителя 1 частоты поступает число А. На вход вычитающего счетчика 5 поступает код числа Б. В исходном состоянии триггер 10 запирает элементы И 7 и 8, на входах счетчиков 4 и 5. Перед началом вычисления командой Пуск устанавливают суммиругадий счетчик 4 в нулевое положение и, переключая триггер 1( открывают элементы И 7 и 8. Если переключатель 3 установлен в положении Умножение, счетчик 4 начинает суммировать нечетные разряды числа А, поступающие с выхода делителя 1 частоты через формирователь 11 нечетных разрядов на счетные входы нечетных разрядов счетчика 4. Управляющий сигнал, разрешаюций счет в 4, поступает на формирователь 11 нечетных разрядов с синхронизатора 15 через входы переключателя 3. Затем по сигналу, поступагацему с синхронизатора 15, через входы переключателя 3 на формирователь 13 четных разрядов V в последнем формируются четные разряды числа А. ЧетЕШе разряды числа А поступают с выхода делителя 1 частоты на формирователь 13 четных разрядов, Четные разряды числа А поступают с формирователя 13 четных разрядов на счетные входы четных разрядов счетчика 4, где суммируются с кодом нечетных разрядов числа А. Счетчик 5 начинает вычитать из кода Б импульсы единичной частоты fgA, поступающей через элемент И 7 с формирователя 16 единичной частоты. Через отрезок времени--Ь. -:г--- б счетчик 5 еА устанавливается в нулевое состояние, что вызывает срабатывание индикатора 6. При этом перебрасывается триггер 10, заш1раются элементы ,7 и 8 и открывается элемент И 9. Код счетчика 4, равный N., т.е. произведению вход-шх кодов А и Б, через открытый элемент И 9 поступает на выход устройства..На это процесс вычисления произведения за канчивается. Если переключатель 3 установить в- положении Деление, то счетчик 4 суммирует импульсы ед ничной частоты fg а счетчик 5 вычивает код числа TV. Вычитание числа А производится за два такта. В первый такт на счетные входы неч ;Ных разрядов счетчика 5 с формирователя 12 нечетных разрядов поступ ют нечетные разряды числа А. Во вт рой такт на счетные входы четных р рядов счетчика 5.поступают четные разряды числа А с формирователя 14 четных разрядов. Через отрезоквре Б счетчик 5 устанавливамени -t.- ется в йулевое состояние. При этом срабатывает индикатор 6 нуля, откр вает элемент И 9. Код счетчика 4, тигший к этому моменту значения В через элемент И 9 поступает на выход устройства. Применение новых элементов трехполюсного двухпозиционного переключателя, двух формирователей нечетных разрядов, двух формирователей четных разрядов, синхронизатора и формирователя единичной час тоты, выгодно отличает предлагаемо устройство от известных, так как позволяет значительно уменьшить время выполнения операций деления и умножения. Применение предлагаем устройства уменьшает время выполне ния операции умножения в А man JkiaJl-ieA. максимсиаьное значение числа А; г и т время выполнения опера ilMH -VWH ции умножения известны и предлагаемым устройс вом и операции деления в -« VA- AeAвремя выполнения опера ций деления известным и предлагаемым устройствами. Формула изобретения Множительно-делительное устройст во, содержащее делитель частоты, суммиругадий и вычитающий счетчики, генератор импульсов, индикатор нуля элементы И, управляющий триггер, выход индикатора нуля соединен с единичным входом управляющего триггера и первым входом первого элемента И, второй вход которого соединен с выходом суммирующего счетчика, вход которого соединен с нулезым входом управляющего триггера, вход индикатора нуля соединен с выходом вычитающего счетчика, счетный вход которого подключен к выходу второго элемента И, первый вход которого соединен с выходом управляющего триггера и первым входом третьего элемента И, выход которого подключен к счетному входу суммирующего счетчика, отличающееся тем, что, с целью .повышения быстродействия, -в устройство введены три синхронных двухпозиционных переключателя, два формирователя нечетных разрядов, два формирователя четных разрядов, синхронизатор иформирователь единичной частоты, вход которого подключен к выходу генератора импульсов и входу синхронизатора, а первый выход - ко входу делителя частоты, второй выход - к подвижному контакту первого синхронного двухпозиционного переключателя, подвижный контакт второго из которых подключен к первому выходу синхронизатора, второй выход которого, подключен к подвижному контакту третьего синхронного двухпозиционного переклк)чателя, второй вход второго элементd И соединен с первым неподвижным контактом первого синхронного двухпозиционного переключателя, второй неподвижный контакт которого подключен ко второму входу третьего элемента И, первый вход первого формирователя нечетных разрядов соединен с первым неподвижным контактом второго синхронного двухпозиционного переключателя, первый вход первого формирователя четных разрядов соединен с первым неподвижным контактом третьего синхронного двухпозиционного переключателя, первый вход второго формирователя нечетных разрядов соединен со вторым неподвижным контактом второго синхронного двухпозиционного переключателя, первый вход второго формирователя четных разрядов соединен со вторым неподвижным контактом третьего синхронного двухпозиционного переключателя, вторые входы формирователей нечетных разрядов соединены с первым выходом делителя частоты, вторые входы формирователей четных разрядов соединены со вторым выходом делителя частоты, третьи входы формирователей четных и нечетных разрядов соединены с первыми входами второго и третьего элементов И и выходом управляющего триггера, выходы первого формирователя нечетных разрядов и первого формирователя четных разрядов соответственно подключены ко второму и третьему входам вычитающего счетчика, а выходы второго формирователя

нечетных разрядов и второго формирователя четных разрядов соответственно соединены с третьим и четвертым входаи н суммирующего счетчика.

Источники информацииу принятые во внимание при экспертизе

1.Авторское свидетельство ОССР 432494, кл. G Об F 7/52, 1972 (ПРОТОТИП).

2.Авторское свидетельство СССР W 271115, кл. G 06 F 7/52, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое множительно-делительное устройство | 1981 |

|

SU1012246A2 |

| Делительно-множительное устройство | 1978 |

|

SU798833A1 |

| Анализатор частотного спектра | 1982 |

|

SU1170374A2 |

| Устройство для возведения в степень | 1982 |

|

SU1084787A1 |

| Параллельный анализатор частотного спектра | 1981 |

|

SU998971A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1629886A1 |

| Преобразователь напряжение-код | 1977 |

|

SU945976A1 |

| Цифровой измеритель магнитной индукции | 1990 |

|

SU1755221A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Устройство для деления | 1975 |

|

SU547766A1 |

фиг./

flwx 2 . I I I I 1 I. II I I I I I I

flwxtt

Jp 3p Sp

иг.2

hp

Авторы

Даты

1981-05-15—Публикация

1979-06-15—Подача