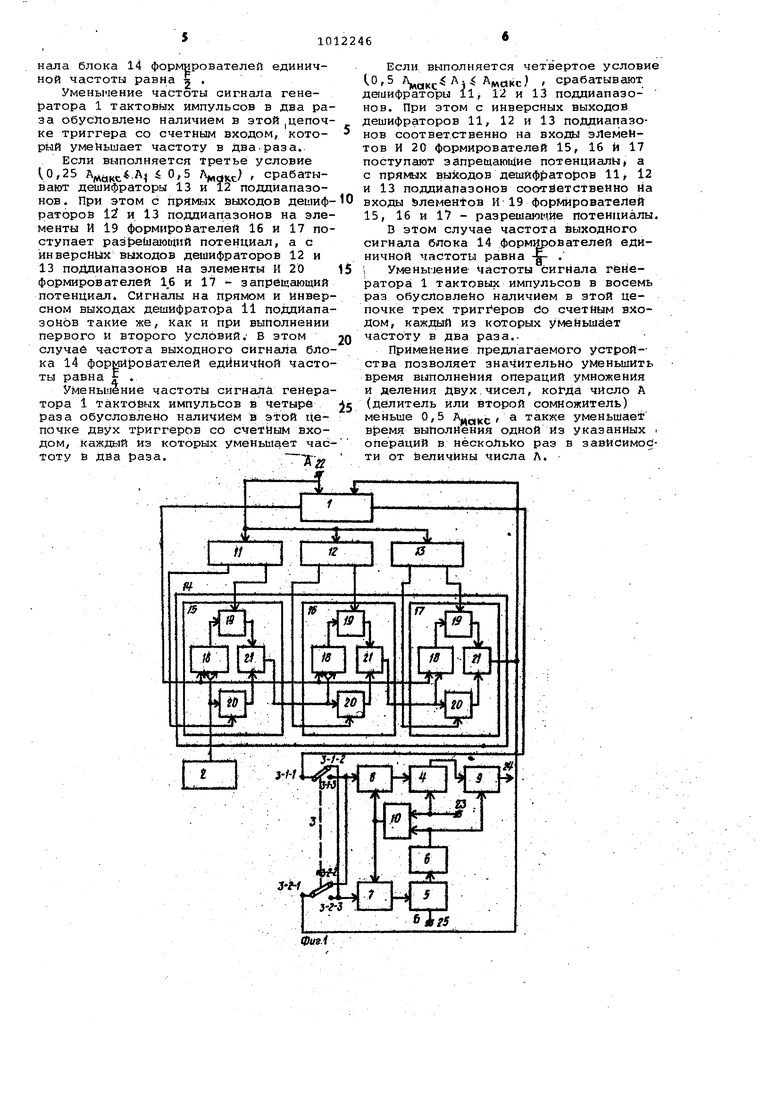

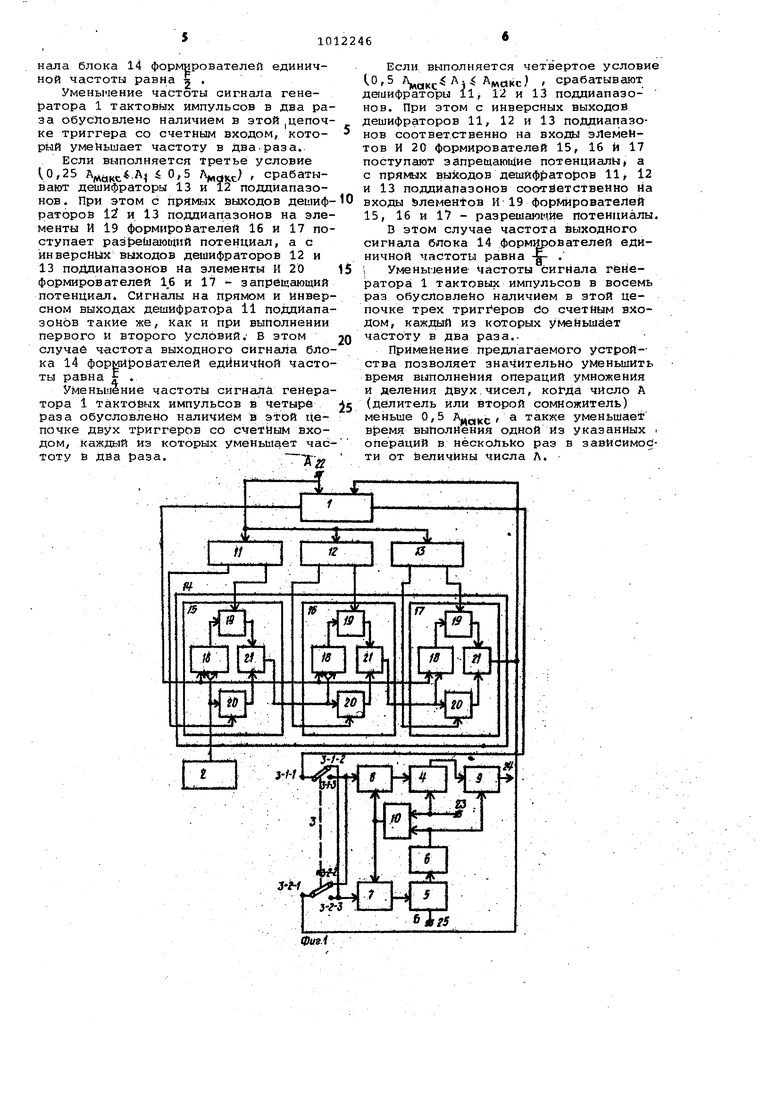

Изобретение относится к области ВЕлчислительной техники. По основному авт.св. 271115 известно цифровое множительно-делитель ное устройство, содержа1чее делитель частоты, суммирующий и вычитакичий счетчики, генератор тактовых импульсов, индикатор нуля, элементы И,триг гер и двухпозиционный переключатель причем выходы генератора тактовых им пульсов и делителя частоты, соединен ного с уп|эавляюпим входом, соединены через двухпозиционный переключатель с элементами И, соединенными по входам также с выходом триггера,,а по выходам - с последовательными входами соответственно суммирующего и вычитающего счетчиков, выход суммирующего счетчика через выходной элемент И соединен с выходом устррй ства, параллельный вход вычитающего счетчика соединен с шинами входного кода Cl. Недостатком данного устройства является большое время преобразования при операциях с числами, код которых меньше половины максимально возможного кода, обусловленное тем, что в данном устройстве преобразование кода входного числа в число-импульсный код происходит за один и тот же интервал времени, который зависит от максимально возможного кода входного числа. Цель изобретения - повышение быст родействия устройства при выполнении операций умножения и деления. Поставленная цель достигается тем, что в цифровое множительно-дели тельное устройство введены п дешифраторов поддиапазонов и п формирователей единичной частоты, причем кажлый формирователь единичной частоты содержит триггер, первый и второй элементы И и элемент ИЛИ, выход триг гера соединен с первым входом первого элемента И, выход которого соединен с первым входом элемента ИЛИ, второй вход элемента ИЛИ соединен с выходом,второго элемента И, первый вход которого соединён со счетным входом триггера, счетный вход триг|Гера первого формирователя единичной частоты соединен с выходом генератора тактовой частоты, а счетный вход ,триггера каждого последующего формирователя единичной частоты соединен с выходом элемента ИЛИ предыдущего формирователя единичной частоты, выход элемента ИЛИ п -го .формирователя соединен с входом первой платы двухпозиционного переключателя и с информационным входом делителя частоты установочные входы триггеров h формирователей частоты объединены и со динены с установочным выходом делит ля частоты, вторые входы первых эле ментов И И формирователей единичной частоты соответственно соединены с прям1-ами выходами h дешифраторов поД диапазонов, а вторые входы вторых элементов и п формирователей единичной частоты .соответственно соединены с инверсными выходами п деГиифраторов поддиапазонов, входы п дешифраторов поддиапазонов Объединены и соединены с первым информационным входом устройства. На фиг.1 представлена функциональная схема устройства; на фиг.2 - временные диаграммы работы устройства. Цифровое делительно-множительное устройство состоит из делителя 1 частоты, генератора 2 тактовых импульсов, . двухпозицИонного переключателя 3, суммирующего счетчика 4, вычитающего, счетчика 5, индикатора 6 нуля, элементов И 7-9, TpHrfepa 10, дешифраторов 11-13 поддиапазонов, блока 14 ф.ормиро в ателей единичной частоту/ включающего однотипные формирователи 15-17 единичной частоты, каждый Из которых состоит из триггера 18, элементов И 19 и 20 и элемента ИЛИ 21, причем выход делителя 1 частоты соединен с контактом 3-1-1 переключателя 3, выход генератора 2 тактовых импульсов соединен со счетным входом триггера 18 и с первым входом второго элемента И 20 первого форми- рователя 15 единичной частоты, выходы вторых элементов И 20 .формиррва телей 15, 16 и 17 единичной частоты соединены соответственно с первыми входами элементов ИЛИ 21, вторые входы которых соединены соотбетственно с выходами первых элементов И 19, первые входы первых элементов И 19 соединены соответственно с йЬосодами триггеров 18, установочные входы которых объединены и соединены с установочным выходом делителя 1 частоты, вторые вхбды первого элемента И 19 формирователей 15, 16 и 17 единичной ча.стоты соединены соответственно с прямым выходами дешифраторов 11, 12 и 13 поддиапазонов, а вторые входы второго элемента И 20 формирователей 15, 16 и 17 единичной частоты соединены соответственно с инверсными выходами дешифраторов 11, 12 и 13 поддиапазонов, выход элемента ИЛИ 21 формирователя 15 единичной частоты соединен со счетным входом триггера 18 формирователя 16, единичной частоты, выход элемента ИЛИ 21 формирователя 16 единичной частоты соединен со счетным входом триггера 18 формирователя 17 единичной частоты, а выход элемента ИЛИ 21 формирователя 17.единичной частоты соединен с информационным входом делителя 1 частоты и с контактом 3-2-1 переключателя 3, входы дешифраторов 11, 12 и 13 поддиапазонов объединены и соединены с установочным входом делителя 1 частоты и первым информационным входом, устройства 22, контакты 3-1-2 и 3-2переключателя 3 объединены И соедине ны с первым входом элемента-И 7, кон такты 3-1-3 и 3-2-2 переключателя 3 объединены и соединены с первым вхо.дом элемента Н 8, вторые входы элементов И 7 и 8 объединены и соединены с выходом триггера 10, вход установки в единицу которого соединен с установочным входом сугФгарурлпего счетчика 4 и с шиной 23 Пуск устройства, вход установки в ноль триггера 10 соединен с,Выходом индикатора 6 нуля и с первым входом элемента И 9, второй вход которого соединен с выходом суммируюцего счетчика 4, а выход элемейта И 9 являётсй выходом 24 устройства, выход элеМен. та И 8 соединен с информациейн(ам вхо дом сум} 1ирующегб счетчика 4, выход элемента И 7 соединен с информационным входом вычитающего 5, установочные входы которого съединены со вторым информационным ёходом устройства 25, а илход вычитающего счетчика 5 соедйиен с входом индикатора б нуля. Устройство работает .следующим о6раэом. На выходе делителя 1 частоты фор-мируются импульсы,( частота кoтoJм jX линейно связана с кодом Д, постуЪаищим на 1ервый инфо|}мационный iaxOA 22 устройства, причем передахочннй коэф фициент делителя 1 частоты равен бдиницё, т.е. А.. Импульсы с частотой поступаю на контакт 3-1-1 перек.точатеяя 3. Ни «онтакт 3-2-1 поступают импульсы еди ничной частоты 2 1 с блока 14 фор мйрователей единичной частоты. На вход вычитающего счетчика 5 со BTotJoro информационного входа поступ ет КОД В. В исходном состоянии триггер 10 запирает элементы И 7 и 8 на входах счетчиков 4.и 5. Перед началом вычисления командой Пуск по ши Не 23 устанавливают суммирующий счет чик 4 в нулевое положение и, переклю чай триггер 10, открывают элементы И 7 н 8. Если переключатель 3 установлен в положение Умножение, счетчик 4 начинает суьадировать входные импульсы частоты f. , поступающие с делителя 1 частоты. Счетчик 5 начинает вычитать из кода В импульсы единичной частоты fj отрезок времени - г 2 счетчик 5 устанавливается в нулевое состояние, что вызывает с|)абатывание индикатора Л При этом переключается триггер 10, запираются элементы И 7 и 8 и открывается И 9. Код счетчика 4, равный ,AB, т.е. произведению входных кодов А и Б, через открытый элемент П 9 поступает на выход 24 устройства. На этом, процесс вычисления произведения заканчивается. Если переключатель 3 установлен в положение Деление, то счетчик 4 суммирует импульсы единичной частО ы f - , а счетчик 5 вычитает импульсы частоты €-, , поступающие с делителя частоты 1. Через отрезок времени, к Б счетчик 5 устанавливается в нулевое состояние. При этом срабатывает индикатор б нуля и отКЕЯЛвает элемент И 9. Код счетчика 4, достигающий к этому моменту значения через элемент И 9 поступает на выход 24 устройства. Значение числа А находиться В одном из следующих поддиапазонов: 1.О 4Aj 0,125 А хс-J 2.ОД25 025 ; 3.0,25 , 0,5 ; 4.0,5 А,цд,({.А4 AMQKC В зависимости от величины входного кода А срабатывают определенные да11ифраторы 11, 12 и 13 поддиапазонов, которые определяют коэффициент деления блока 14 формирователей единичной частоты. Если выполняется первое условие 0,125 о дешифрато.1ры 11, 12 и 13 поддиапазонов не срабатывают. При этом с инверсных выходов дешифраторов 11, 12 и 13 поддиапазонов соответственно на вторые вхоftfj элементов и 20 формирователей 15, 16 и 17 единичной частоты поступают разрешающие .потенциалы, а с прямых выходов дешифраторов 11, 12 и 13 поддиапазонов соответственно на входы элементов И 19 формирователей 15, 16 и 17 единичной частоты поступают запрещающие потенциалы. В этом случае частота сигналов F, поступииаих на блок 14 формирователей единичной частоты с выхода генератора 1 так гoвыx импульсов, не изменяется. Если выполняется второе условие Ч 0,12 5 ,с) срабатывает дешифратор 13 поддиапазонов. При этом с прямого выхода дешифратора 13 поддиапазонов на элемент И 19 формирователя 17 единичной частоты поступает разрешающий потенциал, а с инверсного выхода дешифратора 13 поддиапазонов на элемент И 20 формирователя 17 запрещающий потенциал. Сигналы на и инверсных выходах дешифраторов 11 и 12 поддиапазонов такие же, как и при выполнении первого условия ( 0,125 (j,jL В этом случае.частота выходного спгнала блока 14 формирователей единичной частоты равна f .

Уменьшение частоты сигнала генератора 1 тактовых импульсов в два раза обусловлено наличием в этой |цепочке триггера со счетным входом, который уменьшает частоту в два-раз а.

Если выполняется третье условие

025 АМЫКС -Л 0,5 „g, срабатывают дешифраторы 13 и 12 поддиапазонов. При этом с прямых выходов дешифраторов I2f и 13 поддиапазонов на элементы И 19 формиройателей 16 и 17 поступает разрешающий потенциал, а с йнверсмах вьаходов дешифраторов 12 и 13 поддиапазонов йа элементы И 20 формирователей 1.6 и 17 - запрещающий потенциал4 Сигналы на прямом и инверсном выходах дешифратора 11 поддиапазонов такие же, как и при выполнении первого и второго УСЛОВИЙ. В этом случае частота выходного сигнгша блока 14 формйройателей едйничйой частоты райна .

Уменьшение частоты сигнала генератора 1 тактовых импульсов и четыре раза обусловлено наличием в этой цепочке двух триггеров со счетйым входом, каждый из которых уменьшает час тоту в дйа раза.

Если выполняется четвертое условие (.0,5 wdKc) срабатывают дешифраторы 11, 12 и 13 поддиапазонов. При этом с инверсных выходов дешифраторов 11, 12 и 13 поддиапазонов соответственно на входы эЛемейтов И 20 формирователей 15, 16 и 17 поступают запрещающие потенциал а с пряьфлх выходов дешифраторов 11 12 и 13 поддиапазонов соотйетственно на входы йлеменфов и 19 формирователей 15, 16 и 17 - разрешаюийе потенциалы

В stoM случае частота выходного сигнала блока 14 формирователей единичной частоты равна -|- . j Уменьшение Частоты сигнала генератора 1 тактовых импульсов в восемь раз обусловлено наличием в этой цепочке трех тригг еров do счетным входом, каждый из которых уменьшает частоту в два раза,Применение предлагаемого устройства позволяет значительно уменьшить время выполнения операций умножения и деления Двух.чисел, когда число А (делитель или второй сомножитель) меньше 0,5 , , а также уменьшает время выполнения одной Из указанных операций в HecKoftbko раз в завИСимОс:ти от величины числа А.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1979 |

|

SU830379A1 |

| Устройство для возведения в степень | 1982 |

|

SU1084787A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Делительно-множительное устройство | 1978 |

|

SU798833A1 |

| Устройство для возведения в степень | 1982 |

|

SU1076904A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1629886A1 |

| Преобразователь напряжение-код | 1977 |

|

SU945976A1 |

| Параллельный анализатор частотного спектра | 1981 |

|

SU998971A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1644054A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1133593A1 |

ЦИФРОВОЕ МНОЖИТЕЛЬЙО-ДЁЛЙ- : ТЕЛЬНОЕ УСТРОЙСТВО ПО ает.Св 271115, о т л и j а ю ш е е с я тем, что с цельй повьшейия бустролействия уст- ; :ройстба, fe него введены Н дешифраторов пбддйанаэонов и блок И формирователей единичной частоты, причем КйждыЙ формирователь единичной частоты содержит триггер, первый и элеМей ы И и элемент ИЛИ, выход триггера соединен с первым входомпервого элемента И, выход которого со(эдиней с перйым входом элемента ЙЙИ Второй вход элемента ИЛИ соединен с выходом второго элемента И, первый вход которого соединен со счетным входом триггера, счетны вход триггера первого формирователя единичной частоты соединен с выходом генератора тактовой частоты, а счетный вход триггера каждого последующего формирователя единичной частоты соединен с выходом элемента ИЛИ предыдущего формирователя единичной частоты, выход элемента ИЛИ п -го формирователя соединен с входом первой платы двухпозиционНого переключателя и с информационным уходом делителя частоты, установочные входы триггеров и формирователей частоты объединены и соединена с установочным выходом ;делителя частоты, вторые входы первых элементов И tr формирователей единич- g ной соответственно соединены, с прял4лми выходами п деитфраторов поддиапазонов, а вторые входы вторых элементов И п Формирователей единичной частоты соответственно соединены с инверсными выходами п дешифраторов поддиапазонов, входы п дешифраторов. поддиапазонов объединены и соединены с первым информационным входом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЦИФРОВОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 0 |

|

SU271115A1 |

| г, 06 F 7/52, 196 (прототип) | |||

Авторы

Даты

1983-04-15—Публикация

1981-11-02—Подача