BfcuM входом второго элемента группы И,, первый вход третьего элемента группы И соединен с третьим выходом .вторрго дешифратора, входы начальной установки в ноль триггера, реверсивного счетчика и формир,ователя одиночных импульсов соединены с |ВТОрым выходом второго дешифратора, выход генератора импульсов соединен с вторыми входами всех элементов группы И, выходы которых соединены с первой группой входов элемента ИЛИ, второй вход которого соединен с выходом формирователя одиночных импульсов, выход первого элемента ИЛИ соединен со счетным входом реверсивного счетчика, вход перевода в режим вычитания импульсов которого соединен с инверсным выходом триггера, разрядные выходы реверсивного счетчика соединены с вторыми группами разрядных входов матриц умножения двух разрядов и воведения десятичной цифры в квадрат, информационные входы регистра основания соединены с входом устройства, в блоке управления прямой выход первого триггера соединен с первым входом первого элемента И, выход которого соединен со счетным входом счетчика циклов, разрядные выходаа которого соединены с информационными входами второго дешифратора, второй выход которого срединен с входом установки в ноль второго триггера и пepвы JI входом .второго элемента ИЛИ, выход генератора тактов соединен с вторым входом первого элемента И и первым входом второго элемента И, второй вход которого соединен с инверсным выходом первого триггера, вход сброса которого соединен с третьим выходом второго дешифратора, вход установки в единицу первого триггера соединен с выходом второго элемента ИЛИ, второй вход которого соединен-с выходом третьего элеме нта И и входом рброса счетчика циклов, первый вход третьего элементами соединен с первым выходом третьего дешифратора, информационные входы которого соё,динены с разрядными выходами счетчика тактов, счетный вход которого сое динен с выходом (Второго элемента И, второй вход третьего элемента И соединен с прямым выходом второго триггера, стробирующие вхоли первого и второго дешифраторов соединены с первым выходом триггера режимов, а второй выход последнего - со стробирующим входом третьего дешифратора, . второй, третий, четвертый, , шестой и седьмой выходы третьего дешифратора соединены соответственно с управляющими входами pej-HCTpa основания, матрицы возведения десятичной цифры в квадрат десятичного счетчика, матрицы умножения двух разрядов, преобразователя десятичного числа в число-импульсный код и управлякивдгм входом первой и второй схем сравнения .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1982 |

|

SU1076904A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1141406A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1133593A1 |

| Устройство для возведения в квадрат | 1983 |

|

SU1160404A1 |

| Множительно-делительное устройство | 1979 |

|

SU830379A1 |

| Множительно-делительное устройство | 1978 |

|

SU877536A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1629886A1 |

| Способ определения индукции магнитного поля в зазоре магнитопровода | 1987 |

|

SU1688211A1 |

| Цифровой измеритель магнитной индукции | 1989 |

|

SU1675810A1 |

| Цифровой измеритель магнитной индукции | 1988 |

|

SU1644054A1 |

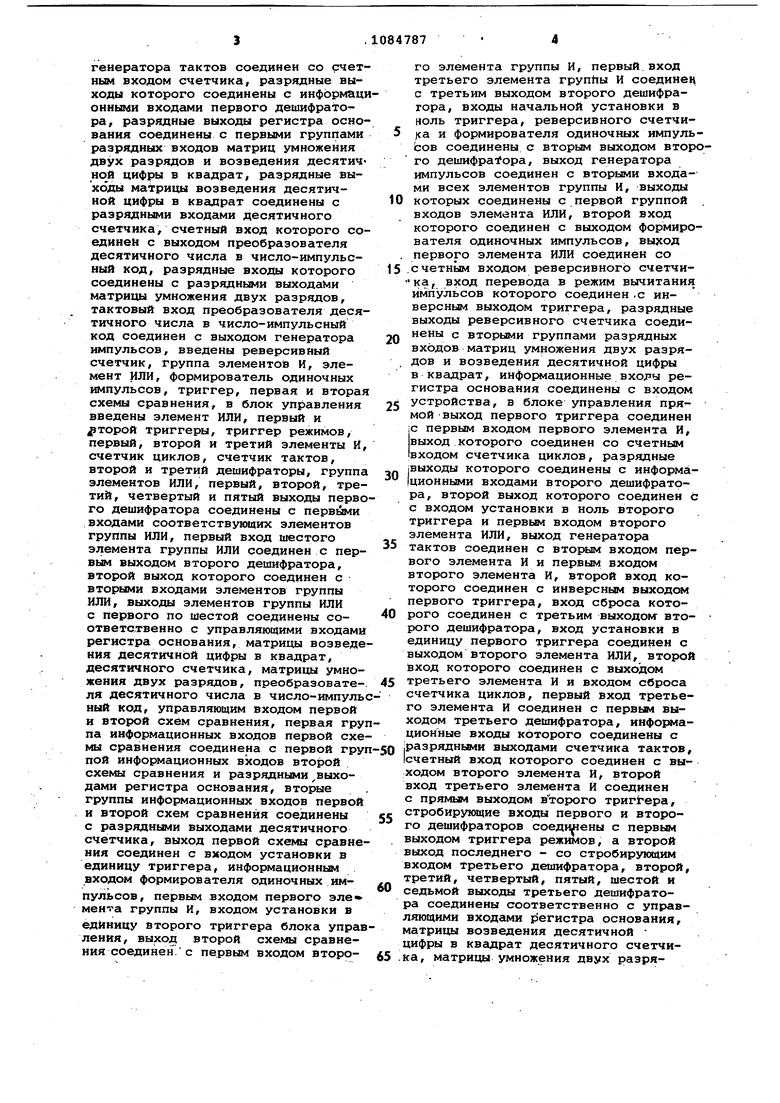

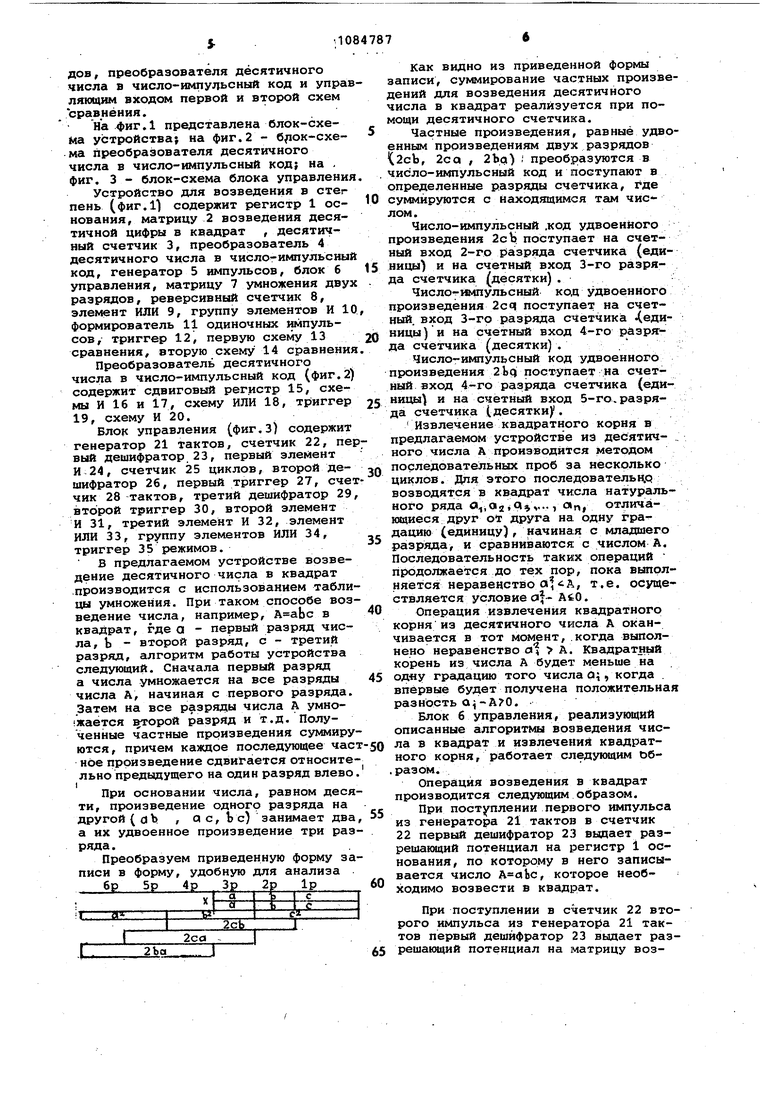

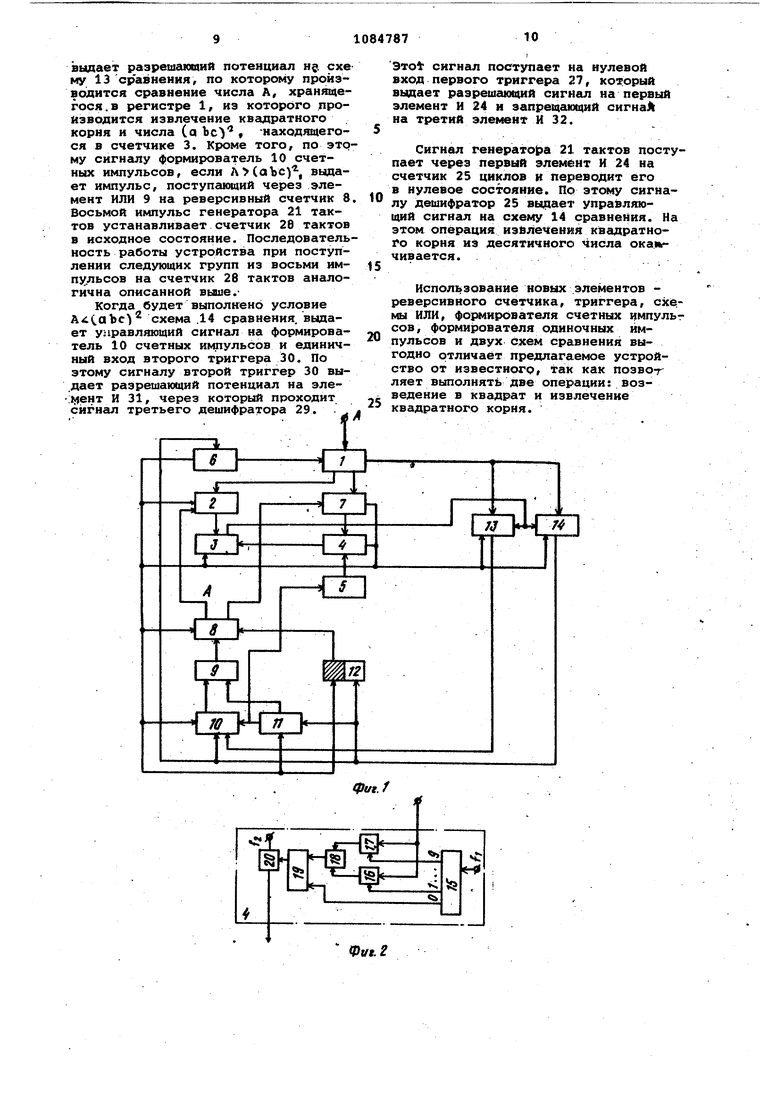

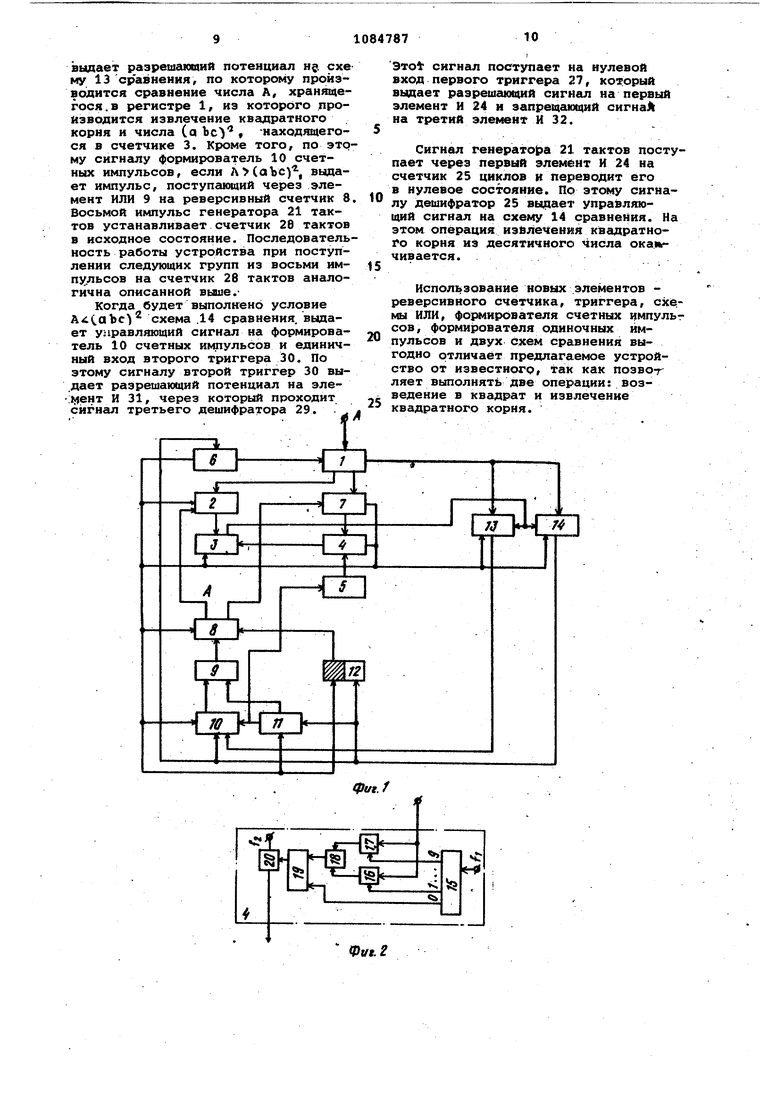

УСТРОЙСТВО ДЛЯ ВОЗВЕДЕ НИЯ В СТЕПЕНЬ, содержащее регистр основания, матрицу умножения двух разрядов, матрицу возведения десятичной цифры в квадрат, десятичный счетчик, преобразователь десятичного числа в число-импульсный код, генератор импульсов, блок управления, содержащий генератор тактов, первый дешифратор, выход генератора тактов соединен со счетным входом счетчика, разрядные выходы которого соединены с информационными входами первого дешифратора, разрядные выходы регистра основания соединены с первыми группами разрядных входов матриц умножения двух разрядов и возведения десятичной цифры в квадрат, разрядные выходы матрицы возведения десятичной цифры в квадрат соединены с разг рядными входами десятичного счетчика, счетный вход которого соединен с выходом преобразователя десятичного числа в число-импульсный код, разрядные входы которого соединены с разрядными выходами матрицы умно- жения двух разрядов, тактовый вход преобразователя десятичного числа в число-импульсный код соединен с выходом генератора импульсов, о т л ич а ю;,щ е е с я тем, что, с целью расширения области его применения путем обеспечения возможности извле чения квадратного корня из десятичного числа в него введены реверсив ный счетчик, группа элементов И, элемент ИЛИ, формирователь одиночных импульсов, триггер, первая и вторая схемы сравнения, в блок управления введены элемент ИЛИ, первый и второй триггеры, триггер режимов, первый, второй и третий элементы И, счетчик циклов, счетчик тактов, второй и третий дешифраторы, группа элементов ИЛИ, первыЛ второй, третий, четвертый и пятый выходы первого дешифратора соединены с первыми входами соответствующих элементов группы ИЛИ, первый вход шестого элемента группы ИЛИ i соединен с первым выходом второго дешифратора, второй выход которого (Л соединен с вторыми входами элементов группы ИЛИ, выходы.элементов группы ИЛИ с первого по шестой соединены соответственно с управляющими входами регистра основания, матрицы возведения десятичной цифры в ;квадрат, десятичного счетчика, матрицы умножения двух разрядов, преобразователя десятичного числа в число-импульсный код, управляющим входом первой и второй схем сравнеэо ния, первая группа информационных 4 1 входов первой схемы сравнения соеди-нена с первой группой информационных входов второй схемы сравнения 00 и разрядными выходами регистра основания, вторые группы информационных входов и второй схем срав нения соединены с разрядными выходами десятичного счетчика, выход первой схемы сравнения соединен с входом установки в единицу триггера, информаионным входом формирователя одиночных импульсов, первым входом первого элемента группы И, входом установки в единицу второго 1 триггера блока управления, выход втс рой схемы сравнения с пер

I

Изобретение относится к вычислительной технике и может быть приме jeHo в цифровых приборах для обра.ботки результатов измерения.

Известно устройство содержащее г нератор импульсов, группу элементов И, счетчик результата, счетчик числа, группу дешифраторов нуля. Данное устройство позволяет возводить десятичные числа, представлен ые двоично-десятичным кодом, в квадрат l .

Недостатком данного устройства яляется невозможность извлечения квадратного корня из заданного числа.

Наиболее близким по технической сущности к изобретению является устройство, содержащее регистр основания, матрицу разрядов, матрицу произведения двух разрядов, накопитель, лреоОразователь числа в код.

генератор импульсов и схему управления 2J .

Недостатком, известного устройства также является невозможность извле чения квадратного корня: из заданного числа.

Целью изобретения является расширение функциональных возможностей путем обеспечения возможности извлеJ. чения квадратного корня из десятичного числа.

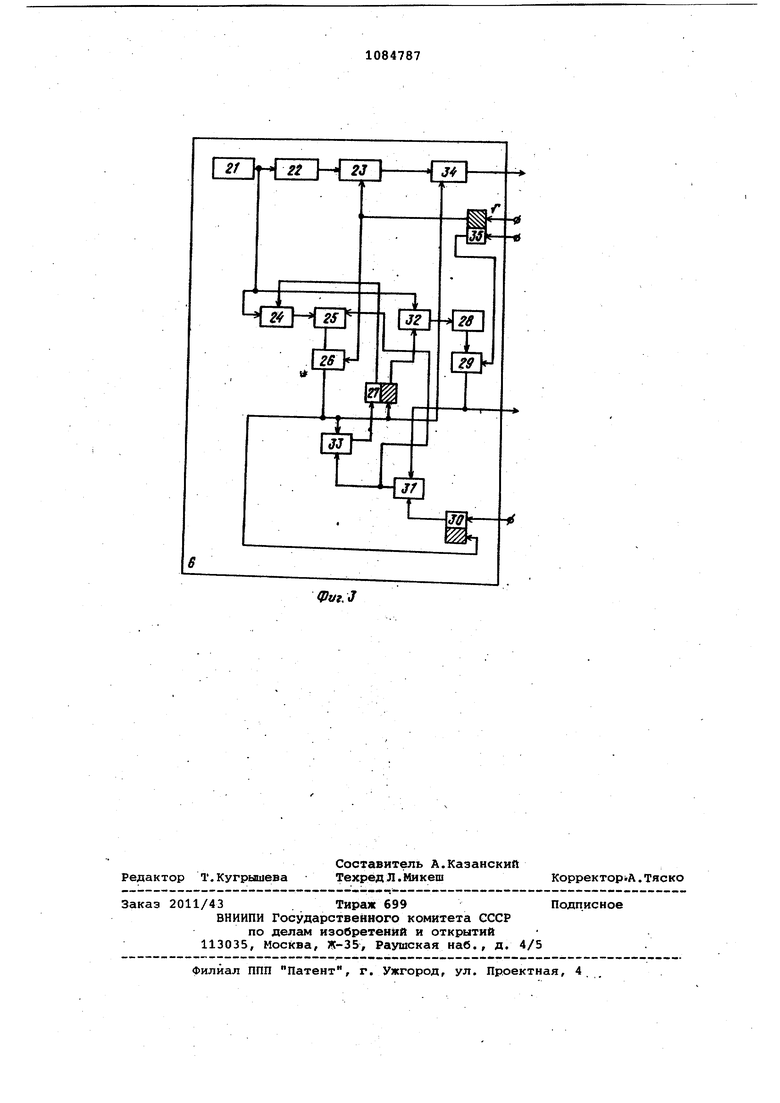

Поставленная цель достигается тем, что в устройство для возведения в степень, содержащее регистр основания, матрицу умножения двух разрядов, матрицу возведения десятичной цифры в квадрат, десятичный счетчик, преобразователь десятичного числа в число-импульсный код, генератор импульсов, бхюк управле0 ния, содержащий генератор тактов, счетчик, первый дешифратор, выход генератора тактов соединен со счет ным входом счетчика, разрядные выходы которого соединены с информац онными входами первого дешифратора, разрядные выходы регистра осно вания соединены с первыми группами разрядных входов матриц умножения двух разрядов и возведения десятич ной цифры в квадрат, разрядные выходы матрицы возведения десятичной цифры в квадрат соединены с разрядными входами десятичного счетчика, счетный вход которого со единен с выходом преобразователя десятичного числа в число-импульсный код, разрядные входы которого соединены с разрядными выходами матрицы умножения двух разрядов, тактовый вход преобразователя деся тичного числа в число-импульсный код соединен с выходом генератора импульсов, введены реверсивный счетчик, группа элементо1в И, элемент ИЛИ, формирователь одиночных импульсов, триггер, первая и втора схемы сравнения, в блок управления введены элемент ИЛИ, первый и торой триггеры, триггер режимов, первый, второй и третий элементы И счетчик циклов, счетчик тактов, второй и третий дешифраторы, групп элементов ИЛИ, первый, вторюй, тре тий, четвертый и пятый выходы перв го дешифратора соединены с nepBiSwH входами соответствующих элементов группы ИЛИ, первый вход шестого элемента группы ИЛИ соединен с первым выходом второго дешифратора, второй выход которого соединен с вторыми входами элементов группы ИЛИ, выходы элементов группы ИЛИ с первого по шестой соединены соответственно с управляющими входами регистра основания, матрицы возведе ния десятичной цифры в квадрат, десятичного счетчика, матрицы умножения двух разрядов, преобразователя десятичного числа в число-импуль ный код, управляющим входом первой и второй схем сравнения, первая гру па информационных входов первой схе мы сравнения соединена с первой гру пой информационных входов второй схемы сравнения и разрядными ,выходами регистра основания, вторые группы информационных входов первой и второй схем сравнения соединены с разрядными выходами десятичного счетчика, выход первой схемы сравне ния соединен с входом установки в единицу триггера, информационным входом формирователя одиночных импульсов, первым входом первого эле мента группы И, входом установки в единицу второго триггера блока упра ления, выход второй схемы сравнения соединен. с первым входом второго элемента группы И, первый вход третьего элемента группы И соединен с третьим выходом второго дешифратора, входы начальной установки в ноль триггера, реверсивного счетчица и формирователя одиночных импульсов соединены с вторым выходом второго дешифратора, выход генератора импульсов соединен с вторыми входами всех элементов группы И, выходы которых соединены с первой группой . входов элемента ИЛИ, второй вход которого соединен с выходом формирователя одиночных импульсов, выход первого элемента ИЛИ соединен со .счетным входом реверсивного счетчика, вход перевода в режим вычитания импульсов которого соединен .с инверсным выходом триггера, разрядные выходы реверсивного счетчика соединены с вторыми группами разрядных входов матриц умножения двух разрядов и возведения десятичной цифры в квадрат, информационные вхоры регистра основания соединены с входом устройства, в блоке управления прямой выход первого триггера соединен с первым входом первого элемента И, выход которого соединен со счетным входом счетчика циклов, разрядные ВЫХОДЫ которого соединены с информа(ционными входами второго дешифратора, второй выход которого соединен е с входом установки в ноль второго триггера и первым входом второго элемента ИЛИ, выход генератора тактов соединен с входом первого элемента И и первым входом второго элемента И, второй вход которого соединен с инверсным выходом первого триггера, вход сброса которого соединен с третьим выходом второго дешифратора, вход установки в единицу первого триггера соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И и входом сброса счетчика циклов, первый вход третьего элемента И соединен с первым выходом третьего дешифратора, информационные входы которого соединены с |разряднЕ1Ми выходами счетчика тактов, ючетный вход которого соединен с выходом второго элемента И, второй вход третьего элемента И соединен с прямым выходом второго триггера, стробир1пощие входы первого и второго дешифраторов соединены с первым выходом триггера режимов, а второй выход последнего - со стробирующим входом третьего дешифратора, второй, третий, четвертый, пятый, шестой и седьмой выходы третьего дешифратора соединены соответственно с управляющими входами регистра основания, матрицы возведения десятичной цифры в квадрат десятичного счетчика, матрицы умножения двух разрядов, преобразователя десятичного числа в число-дашульсный код и упра ляющим входом первой и второй схем сравнения. на фиг.1 представлена блок-схема устройства; на фиг. 2 - б 1ок-схема преобразователя десятичного числа в число-импульсный код; на . фиг. 3 - блок-схема блока управлени Устройство для возведения в стег пень (фиг.) содержит регистр 1 основания, матрицу 2 возведения десятичной цифры в квадрат , десятичный счетчик 3, преобразователь 4 десятичного числа в число-импульсиы код, генератор 5 импульсов, блок б управления, матрицу 7 умножения дву разрядов, реверсивный счетчик 8, элемент ИЛИ 9, группу элементов И 1 формирователь 11 одиночных импульсов, триггер 12, первую схему 13 сравнения, вторую схему 14 сравнени Преобразователь десятичного числа в число-импульсный код (фиг. 2 содержит сдвиговый регистр 15, схемы И 16 и 17, схему ИЛИ 18, триггер 19, схему И 20. Блок управления (фиг.З) содержит генератор 21 тактов, счетчик 22, пе вый дешифратор.23, первый элемент И 24, счетчик 25 циклов, второй дешифратор 26, первый триггер 27, сче чик 28 тактов, третий дешифратор 29 второй триггер 30, второй элемент И 31, третий элемент И 32, элемент ИЛИ 33, группу элементов ИЛИ 34, триггер 3 5 режимов. В предлагаемом устройстве возведение десятичного числа в квадрат .производится с использованием табли цы умножения. При таком способе воз ведение числа, например, в квадрат, где а - первый разряд числа, Ь - второй разряд, с - третий разряд, алгоритм работы устройства следующий. Сначала первый разряд а числа умножается на все разряды числа А, начиная с первого разряда. Затем на все разряды числа А умно жается орой разряд и т.д. Полученные частные произведения суммиру ются, причем каждое последующее час мое произведение сдвигается относите льно предыдущего на один разряд влево 1 При основании числа, равном деся ти, произведение одного разряда на другой ( а Ъ , а с, Ь с) занимает два а их удвоенное произведение три раз ряда. Преобразуем приведенную форму за писи в форму, удобную для анализа 6р 5р 4р Зр 2р 1р Как видно из приведенной формы записи, суммирование частных произведений для возведения десятичного числа в квадрат реализуется при помощи десятичного счетчика. Частные произведения, равные удвоенным произведениям двух разрядов (зсЬ, 2са , 2boi) i преобразуются в число-импульсный код и поступают в определенные разряды счетчика, где суммируются с находящимся там числом . Число-импульсный ,код удвоенного произведения 2сЬ поступает на счетный вход 2-го разряда счетчика (единицы) и на счетный вход 3-го разряда счетчика (десятки). Число-импульсный код удвоенного произведения 2cq поступает на счетный, вход 3-го разряда счетчика единицы) и на счетный вход 4-го разряда счётчика (десятки) . Число-импульсный код удвоенного произведения 2 bqi поступает на счетный вход 4-го разряда счетчика (единицы) и на счетный вход 5-го.разряда счетчика (десяткиу. Извлечение квадратного корня в предлагаемом устройстве из десятичного числа А производится методом последовательных проб за несколько циклов. Для этого последовательно возводятся в квадрат числа натурального ряда а, а2 i Q отличающиеся друг от друга на. одну гра дацию (единицу), начиная с младшего разряда, и сравниваются: с числом А. Последовательность таких операций продолжается до тех пор, пока выполняется неравенство oi А, т.е. осуществляется условие df-AtO. Операция извлечения квадратного корня из десятичного числа А оканчивается в тот момент,.когда выполнено неравенство « А. Квадратный корень из числа А будет меньше на од«у гргщацию того числа р, когда . впервые будет получена положительная разность . Блок 6 управления, реализующий описанные алгоритмы возведения числа в квадрат и извлечения квадратного корня, работает следующим об.разом. Операция возведения в квадрат производится следующим образом. При поступлении первого импульса из генератора 21 тактов в счетчик 22 первый дешифратор 23 выдает разрешающий потенциал на регистр 1 основания, по которому в него записывается число , которое необходимо возвести в квадрат. При поступлении в счетчик 22 второго импульса из генератора 21 тактов первый дешифратор 23 выдает разрешающий потенциал на матрицу возведения десятичной цифры в квадрат. По этому сигналу квадрат каждого разряда а, Ь, с. числа А поступает .на соответствующие разрядные входы десятичного счетчика 3.

При поступлении в счетчик 22 тре его импульса из генератора 21 так|Тов, первый дешифратор 23 выдает разрешакяций сигнал на матрицу 7 умнжения двух разрядов и на преобразователь 4 десятичного числа в числоимпульсный.код. По этому сигналу удвоенное произведение 2сЬ С единицы) из матрицы 7 умножения двух раз рядов поступает на преобразователь 4 десятичного числа в число-импульс ный код.

При поступлении в.счетчик 22 :четвертого импульса из генератора 21 тактов первый дешифратор 23 выдает разрешавяций сигнал на матрицу 7 умножения двух разрядов и на преобразователь 4 десяти ого чйсла в число-импульсный код .По : этому сигналу удвоенное произведе ние 2сЬ (десятки) из матрицы 7 умножения двух разрядов поступает на преобразователь 4 десятичного числа в число-импульсный код.

При поступлении пятого и шестого импульсов из генератора 21 тактов в счетчик 22 производится преобразо вание удвоенного произведения в пропорциональное число импульсов, KOT6i ie поступают в счетчик 3.

При поступлении седьмого и восьмого импульсов из тактового генератора.21 в счетчик 22 первый дешифратор 23 выдает разрешающий сигНсШ на матрицу 7 умножения двух разрядов и преобразователь 4. десятичного числа в число-импульсный код, по которому производится преобразование удвоенного произведения 2Ьа , находящегося в матрице 7, в пропорциональное число импульсов, которые поступают в счетчик 3.

Операция извлечения квадратного корня производиться следующим образом. .

При поступлении первого импуль-т са из генератора 21 тактов в счетчик 25 циклов второй дешифратор 26 вьщает сигнал начальной установки НУ, устанавливающий все блоки : устройства, имеющие цифровую память в исходное состояние. При поступлении в счетчик циклов второго импульса из генератора 21 тактов второй дешифратор 26 выдает разрешающий потенциал на регистр 1 основания. По этому сигналу в регистр 1 основания записывается число , v из которого необходимо извлечь квадратный корень. Кроме того, по сигналу второго дешифратора 26 формирователь 10 счетных импульсов выдает импульс, поступающий на реверсивный

счет ик 8, а первый триггер 27 устанавливается в исходное состояние При этом выходной сигнал первого триггера 27 запрещает прохождение сигналов генератора 21 тактов через первый элемент И. 24 на счетчик .25 циклов и разрешает прохождение этих сигналов чвзрез третий элемент И 32 на счетчик 28 тактов.

По первому импульсу,.поступившему из генератора 21 тактов в счетчик 28 тактов через третий элемент Л 32, третий дешифратор 29 выдает разрешающий потенциал на матрицу 2 возведения десятичной цифры в квадрат. По этому сигналу квадрат каж дого разряда и, Ь, с числа, находящегося в реверсивном счетчике 8, пбступает на соответствующие разрядные входы десятичного счетчика 3. При поступлении в счетчик 28 тактов второго импульса из генератора 21 тактов третий дешифратор 29 выдает разрешающий сигнал на матрицу 7 умножения двух разрядов и на преобразователь 4 десятичного числа в число-импульсный код. По этому сигналу удвоенное произведение 2сЬ (единицы) из матрицы 7 умножения двух разрядов поступает на преобразователь 4 десятичного числа в число-импульсный код. При поступлении в счетчик 28 тактов третьего импульса из генератора 21 тактов третий дешифратор 29 вьщает разрешающий потенциал на матрицу 7 умножения двух разрядов и на преобразователь 4 десятичного числа в число-импульсный код. По этому сигналу удвоенное произведение 2сЪ (десятки) из матрицы 7 умножения двух разрядов поступает на преобразователь 4 десятичного числа в число-импульсный код.

При поступлении четвертого и пятого импульсов из генератора 21 тактов в счетчик 28 тактов производится преобразование удвоенного произведения 2ccf в пропорциональное число импульсов, которые поступают в счетчик 3.

При поступлении шестого и седьмого импульсов из генератора 21 тактов в счетчик 28 тактов третий дешифратор 29 выдает разрешающий сигнал на матрицу 7 умножения двух разрядов и преобразователь 4. десятичного числа в число-импульсный код, по которому производится преобразование удвоенного произведения 2 Ьа , находящегося в матрице 7 умножения двух разрядов, в пропорциональное число импульсов, которые поступают в счетчик 3.

При поступлении восьмого импульса из генератора 21 тактов в счетчик 28 тактов третий дешифратор .29 19ыдает разрешгиоший потенциал н. схе му 13 сравнения, по которол4у производится сравнение числа А, хранящегося, в регистре 1, из которого производится извлечение квгшратного корня и числа (а Ъс f -находящегося в счетчике 3. Кроме того, по это му сигналу формирователь 10 счетных импульсов, если AXabc), выдает импульс, поступающий через элемент ИЛИ 9 на реверсивный счетчик 8 Восьмой импульс генератора 21 тактов устанавливает счетчик 28 тактов в исходное состояние. Последователь ность работы устройства при поступлении следующих групп из восьми импульсов на счетчик 28 тактов аналогична описанной выше.когда будет выполнено условие (.аЬс схема .14 сравнения, выдает управляющий сигнал на формирователь 10 счетных икщульсов и единичный вход второго триггера 30. По этому сигналу второй триггер 30 выдает разрешающий потенциал на элеjyjeHT И 31, через который проходит сигнал третьего дешифратора 29. 3TOt сигнал поступает на нулевой вход первого триггера 27, который выдает разрешающий сигнал на первый элемент И 24 и запрещающий сигнаЛ на третий элемент И 32. Сигнал генерато|; а 21 тактов поступает через первый элемент И 24 на счетчик 25 циклов к переводит его в нулевое состояние. По ЭТОМУ сигналу дешифратор 25 выдает управляющий сигнёьл на схему 14 сравнения. На этом операция извлечения квадратного корня из десятичного числа окамгчивается. Использование новых элементов реверсивного счетчика, триггера, схё,мы ИЛИ, формирователя счетных цмпулы сов, формирователя одиночных импульсов и двух схем сравнения выгодно отличает предлагаемое устройство от известного, так как позво-г ляет выполнять две операции: возведение в квадрат и извлечение квадратного корня.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровое устройство для возведенияВ КВАдРАТ | 1979 |

|

SU836634A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ | 0 |

|

SU391560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-07—Публикация

1982-02-18—Подача