(54) УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ СИГНАЛОВ В СИСТЕМАХ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое коммутационное устройство | 1985 |

|

SU1378088A1 |

| ЦИФРОВАЯ КОММУТАЦИОННАЯ СИСТЕМА | 1994 |

|

RU2127025C1 |

| Устройство для вывода информации | 1983 |

|

SU1124279A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Адаптивный цифровой групповой приемник сигналов управления и взаимодействия с дельта - модуляцией | 1990 |

|

SU1800658A1 |

| Устройство уплотнения для системы связи с импульсно-кодовой модуляцией | 1978 |

|

SU777875A1 |

| МНОГОФУНКЦИОНАЛЬНАЯ СИСТЕМА ВНУТРИКОРАБЕЛЬНОЙ СВЯЗИ | 2005 |

|

RU2304349C2 |

| Автоматическая система единого времени | 1976 |

|

SU657397A1 |

| Ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией | 1990 |

|

SU1786671A1 |

| Устройство для сопряжения двух вычислительных машин | 1983 |

|

SU1111150A1 |

Изобретение относится к многоканальным системам связи и может использоваться в цифровых системах связи с импульсно-кодовой модуляци-. ей (ИКМ), учитьюающих статические свойства передаваемой речевой информации. ,

Известно устройство для приема и передачи сигналов в системах с импульсно-кодовой модуляцией, содержащее блок обнаруже1шя речевых сигналов, первый и второй выходы которого соединены соответственно с первым и вторым входами первого коммутационного блока, первый и второй выходы которого соединены соответственно с информационным и адресным входами певого передающего регистра,, третий и четвертый выходы первого коммутационного блока соединены соответственн с информационным и адресным входами второго передающего регистра, а также второй коммутационньй блок, первый и второй выходы которого соединены соответственно с первыми информационньаад входами первого и второго приемных регистров, первый и второй адресные выходы которых подключены соответственно к первому и второму входам второго коммутационного блока, третий и четвертый входы которого соединены с информационными выходами первого и второго приемных регистров, а также тактовый генератор l .

Однако в известном устройстве воэможен сбой адресных сигналов в процессе передачи информации по тракту, что приводит к неправильной коммутации на приемной стороне не только .информационного сигнала с данным искаженным адресом, но и всех следующих за ним информационных сигналов в цикле передачи. При этом в худшем положении находится информационный сигнал, к которому относится послед-, няя адресная посылка.

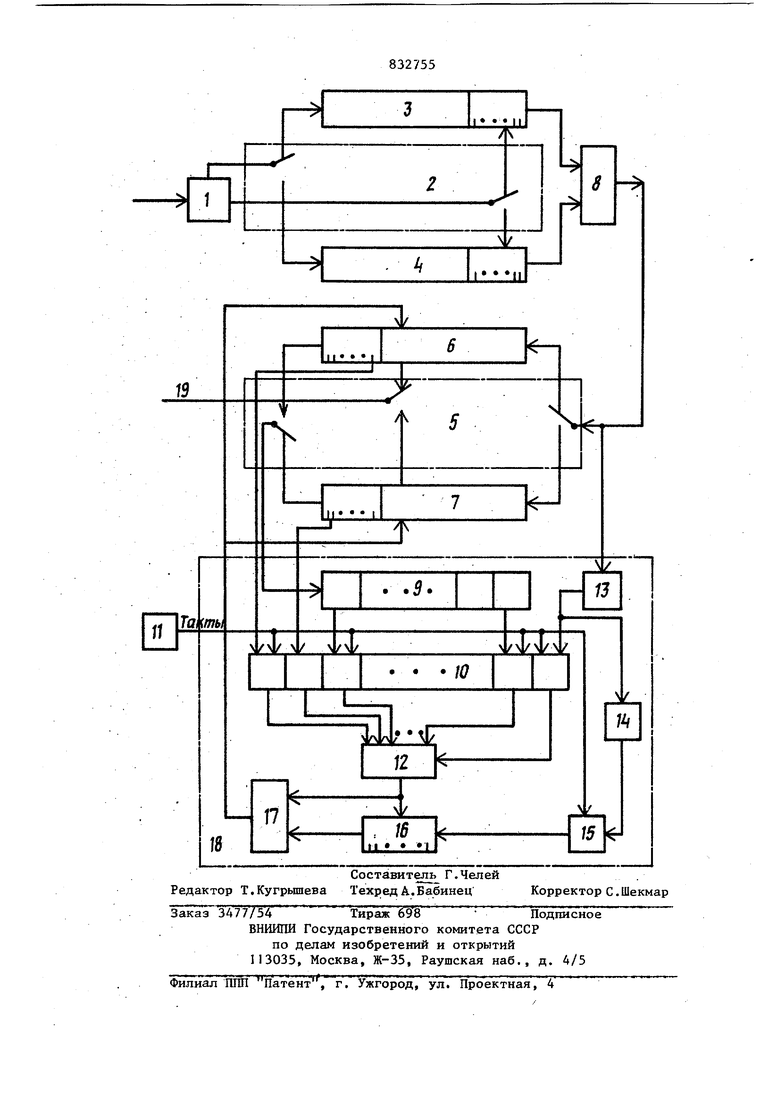

Цель изобретения - повьшение точности приема. Поставленная цель достигается тем. что в УСТРОЙСТВО для приема и пе редачи сигналов в системах с импульс.но-кодовой модуляцией содержащее блок обнаружения речевых сигналов первый и ВТОРОЙ выходы которого соединены соответственно с первым и ВТОРЫМ входами первого коммутационного блока, первый и второй выходы которого соединены соответственно с инФормационным. и адресным входами первого передающего регистра, третий и четвертый выходы первого коммутационного блока соединены соответственно с информационным и адресным входом второго передающего регистра, а также второй-коммутационный блек, первый и второй выходы которого соединены с ответственно спервыми информационными входами первого и второго приемных регистров, перйый и второй адресные выходы которых подключены со ответственно к первому и второму вхо дам второго коммутационного блока, третий и четвертьй входы которого со единены с информационными выходами первого и второго приемных регистров а также тактовый генератор,, введены накопитель, первый элемент ИЛИ., реша ющий блок, блок элементов И и последовательно соединенные делитель циклов, инвертор, элемент И блок памяти адреса и второй элемент ИЛИ, выход которого соединен со вторыми информационными входами первого и второго приемных регистров, причем информационные выходы первого и второго передающих регистров соединены соответственно с. первым и вторым вхо дами первого элемента ИЛИ, выход которого соединен с пятым входом второго коммутационного блока и с входом делителя циклов, выход которого подключен к первому входу блока элементов И, второй и третий входы кото рого соединены со вторыми.адресными выходами первого и второго приемного регистров, при этом третий выход вто рого коммутационного блока соединен со входом накопителя, выходы которог . соединены с соответствующими четвертыми входами блока элементов И, выхо ды которого соединены с соответствующими входами рещающего блока, выход которого подключен ко вторым вхо дам второго элемента ИЛИ и блока памяти адреса, причем выход тактового .генератора соединен с пятыми входам, блока элементов И и вторым входом элемента И. На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство дпя приема и передачи сигналов в системах с импульсно-кодовой модуляцией содержит блок 1 обнаружения речевых сигналов, первый коммутационный блок 2, первый 3 и второй 4 передающие регистры, второй коммутационный блок 5, первый 6 и второй 7 приемные регистры, первый элемент ИЛИ 8, накЪпитель 9, блок 10 элементов И, тактовый генератор 11, решающий блок 12,.делитель 13 циклов, инвертор 14, элемент И 15, блок 16 памяти адреса и- второй элемент ИЛИ 17, блок 18 выбора адресных сигналов по больщинству из К циклов и линию 19. Предлагаемое устройство работает следующим образом. В каждом цикле передаваемых на вход блока 1 сигналов импульсно-кодовой модуляции с помощью этого блока осуществляется анализ временных отрезков, отведенных определенным каналам связи, и в соответствующей, возрастающей по порядку последовательности происходит маркировка тех каналов, по которым в данном цикле передаются информационные сигналы путем записи на адресные входы первого 3 и второго 4 передающих регистров сигнала 1. Одновременно с этим сам информационньй сигнал записывается в соответствующую информаци-. онную ячейку первого 3 и второго 4 передающих регистров. Первый коммутационньй блок 2 обеспечивает поочередное накопление информационных и адресных сигналов в передающих регистрах 3 и 4 в течение соответствующего цикла, по окончании которого эти сигналы через первый элемент ИЛИ 8 выдаются в тракт передачи. На приемной стороне с помощью второго коммутационного блока 5 осуществляется накопление этих сигналов в первом 6 или втором 7 приемных регистрах, а также поочередное считывание как с адресного выхода приемных регистров 6 или 7 адресной .информации предыдущего цикла в накопитель 9 адресных сигналов на К-2 циклов, где К - количество циклов передачи, так и информационных сигналов с информационных выходов приемных регистров 6 и 7 в соответствии с адресами, поступающими на вторые информационные входы пр емных регистров 6 и 7 -с блока 18 выбора адресных сигналов, по большинству из К циклов. По окончании К-1 цик .ла передачи адресная информация этих циклов хранится в накопителе 9 и на адресном входе второго приемного регистра 7. В К-ом цикле первый адресный сигнал, поступающий из первого приемного регистра 6 и одновременно первые адреса, хранящиеся во втором приемном регистре 7 и в накопителе 9, подаются на входы блока 10 элемен тов И соответственно, сигналы на выходе которых, появляющиеся при наличии на других их входах тактовых импульсов с тактового генератора 11 подаются на решающий блок 12, на выходе которого сигнал появится только При наличии на одном из его входов разрешающего импульса, поступающего с первого выхода блока 10 элементов И, на первый вход которого поступают тактовые импульсы и сигнал с выхода делителя 13 циклов. Этот сигнал записывается в блоке 16 памяти адреса и одновременно через второй элемент ШШ 17 подается на вторые инфор мационные входы первого и второго приемных регистров 6, 7 для считывания в линию 19 хранящейся информации В последующих К-1 циклах считывание информации происходит по сигналам, поступающим из блока 16 памяти адреса, управляемым сигналом, поступающим с элемента И 15, на вход которого поступают тактовые импульсы с тактового генератора 11 и инвертированный инвертором 14 сигнал с -выхода де лителя 13 циклов. Предлагаемое устройство позволяет повысить точность приема и качество передачи речевой информации в статис тических системах связи с ИКМ за сче существенного повышения верности установления соединения, которое для последнего информационного сигнала можно оценить следующим образом. N количество адресных посылок в цикле передачи; РОЩ вероятность сбоев в любой адресной посылке; N.PQ... - вероятность неправильной коммутации для последнего информационного сигнала за счет сбоев адресных посылок В - - минимальное число циклов, в которых происходят сбои адресных сигналов, приводящие к неправильтой коммутации; - вероятность неправильной коммутации последнего информационного сигнапа при использовании предлагаемого устройства. Таким образом, верность установления соединения увеличивается в В раз, например при К 5 верность ус- тановления соединения для последнего информационного сигнала увеличивается в 3 раза. Формула изобретения Устройство для приема и передачи сигналов в системах с импульсно-кодовой модуляцией, содержащее блок обнаружения речевых сигналов, первый и второй выходы которого соединены соответственно с первым и вторым входами первого коммутационного блока, первый и второй выходы которого соединены соответственно с информационным и адресным входами первого передающего регистра, третий и четвертый выходы первого коммутационного блока соединены соответственно с информационным и адресным в-ходом второго передающего регистра, а также второй коммутационный блок, первьй и второй выходы которого соединены соответственно с первыми/информационными входами первого и второго приемных регистров, первый и второй адресные выходы которых подключены соответственно к первому и второму входам второго коммутационного блока, третий и четвертый входы которого соединены с информационными выходами первого и второго приемных регистров, а также тактовый генератор, отличаю- щ е е с я тем, что, с целью повьш1ения точности приема, введены накопитель, первьй элемент ИЛИ, решающий блок, блок элементов И и последовательно соединенные делитель циклов, инвертор, элемент И, блок памяти адреса и второй элемент ИЛИ, выход которого соеданен со вторыми информационными входа14и первого и второго приемных регистров, причем информацион- i ныв выходы первого и второго передакнцих регистров соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход которого

7832755

соединен с пятым входом второго коммутационного блока и с входом дели- ; теля циклов, выход которого подключён к первому входу блока элементов И, второй и третий входы которого сое- j динены со вторыми адресными выходами первого и второго приемного регистров, при этом третий выход второго коммутационного блока соединен со входом накопителя, выходы которого co-fo единены с соответствующими четвертыми входами блока элементов И, выхо8

ды которого соединены с соответствующими входами решающего блока, выход которого подключен ко вторым входам второго элемента ИЛИ и блока памяти адреса, причем выход тактовог генератора соединен с пятыми входами блока элементов И и вторым входом элемента И. . .

Источники информации, принятые во внимание при экспертизе

I. Авторское свидетельство СССР №394987, кл. Н 04 J.-6/jCL2.

II

IS

r

У

I ll

/

Авторы

Даты

1981-05-23—Публикация

1979-05-04—Подача