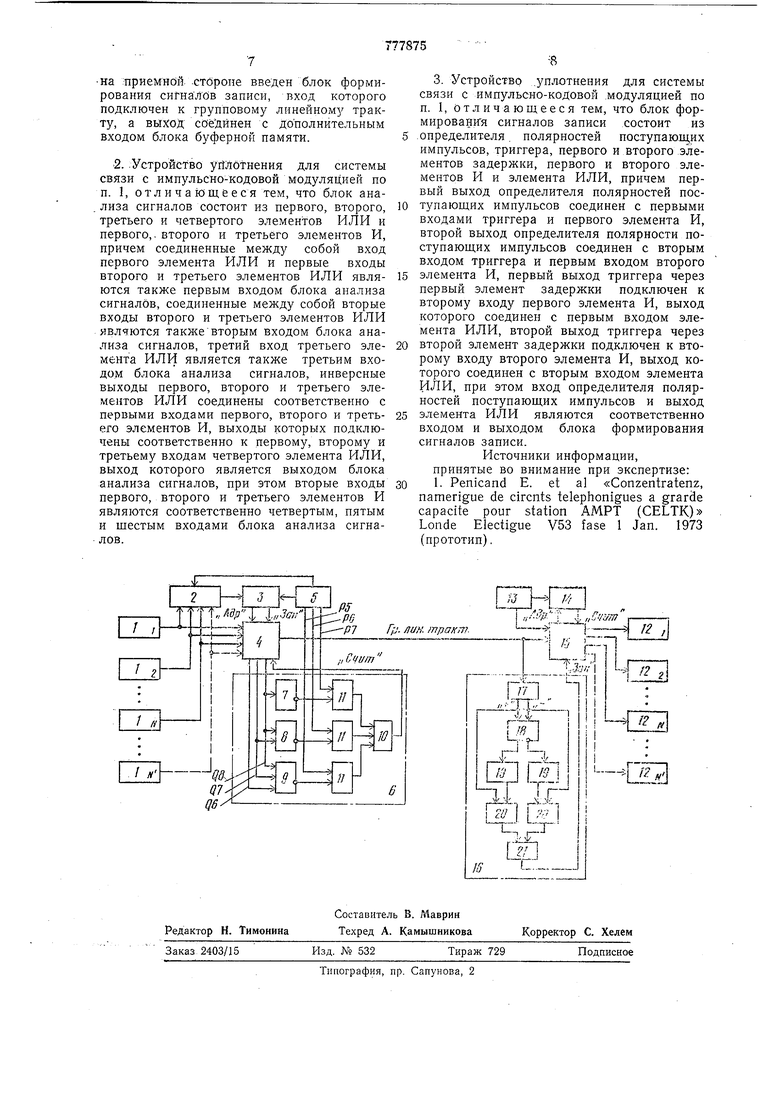

соединены с соответствующими входами блока буферной памяти, информационный выход которого через груиповой линейный тракт соединен с расположенными на приемной стороне системы связи блоком буферной памяти, каждый из «tt информационных выходов которого соединен с выходом соответствующего приемника информационных сигналов, при этом адресный выход и считывающий вход блока буферной памяти соединен соответственно с адресным входом считывающим выходом управляющего блока, з равляющий вход которого подключен к первому выходу генератора тактовой частоты, второй выход которого соединен с управляющим входом блока буферной памяти, на передающей стороне системы связи введен блок анализа сигналов, причем первый, второй и третий входы блока анализа сигналов соединены соответственно с первым, вторым и третьим дополнительными выходами блока буферной памяти, четвертый, пятый и шестой входы блока анализа сигналов соединены соответственно с первым, вторым и третьим дополнительными выходами генератора тактовой частоты, при этом выход блока анализа сигналов подключен к дополнительному входу блока буферной памяти, а на приемной стороне введен блок формирования сигналов записи, вход которого подключен к групповому линейному тракту, а выход соединен с дополнительным входом блока буферной памяти, кроме того блок анализа сигналов состоит из первого, второго, третьего и четвертого элементов ИЛИ и первого, второго и третьего элементов И, причем соединенные между собой вход первого элемента ИЛИ и первые входы второго и третьего элементов ИЛИ являются также первым входом блока анализа сигналов, соединенные между собой вторые входы второго и третьего элементов ИЛИ являются также вторым входом блока анализа сигналов, третий вход третьего элемента ИЛИ является также третьим входом блока анализа сигналов, инверсные выходы первого, второго и третьего элементов ИЛИ соединены соответственно с первыми входами первого, второго и третьего элементов И, выходы которых подключены соответственно к первому, второму и третьему входам четвертого элемента ИЛИ, выход которого является выходом блока анализа сигналов, при этом вторые входы первого, второго и третьего элементов И являются соответственно четвертым, пятым и щестым входами блока анализа сигналов, кроме того блок формирования сигналов записи состоит из определителя полярностей поступающих импульсов, триггера,, первого и второго элементов задержки, первого и второго элементов И и элемента ИЛИ, причем первый выход определиеля полярностей поступающих импульсов соединен с первыми входами триггера и первого элемента PI, второй выход определителя полярностей поступающих импульсов соединен с вторым входом триггера и первым входом второго элемента И, первый выход триггера через первый элемент задержки подключен к второму входу первого элемента ИЛИ, второй выход триггеР через второй элемент задержки подключен к второму входу второго элемента И, выход которого соединен с вторым входом элемента ИЛИ, при этом вход определителя полярностей поступающих импульсов и выход элемента ИЛИ являются соответственно входом и выходом блока формирования сигналов записи. На чертеже приведена структурная электрическая схема предложенного устройства. Устройство уплотнения для систем связи с импзльсно-кодовой модуляцией содержит на передающей стороне: источники 1 информационных сигналов, цифровой пороговый детектор (ЦПД) 2, управляющий блок 3, блок 4 буферной памяти, генератор 5 тактовой частоты, блок 6 анализа сигналов, состоящий из первого, второго, третьего и четвертого элементов или 7, 8, 9, 10 и первого, второго и третьего элементов И 11; на приемной стороне: приемники 12 информационных сигналов, генератор 13 тактовой частоты, управляющий блок 14, блок 15 буферной памяти, блок 16 формирования записи, состоящий из определителя 17 полярностей поступающих импульсов, триггера 18, первого и второго элементов 19 задержки, первого и второго элементов И 20 и элемента ИЛИ 21. Устройство работает следующим образом. На передаче ЦПД 2 анализирует поступающие от системы с импульсно-кодовой модуляцией (ИКМ) канальные коды и с помощью управляющего блока 3 произвоДит запись в блок 4 канальных кодов активных каналов (шина «Зап) и соответствующей адресной информации (щнна «Адр). Однако процессом считывания канальных кодов из блока 4 в групповой линейный тракт управляет не генератор 5, как это было ранее, а блок 6, на который из блока 4 поступают параллельно старщие информационные разряды Q6, Q7, Q8 текущего восьмиразрядного канального кода. На выходе любого элемента ИЛИ 7, 8, 9 появится импульс только в том случае, если на всех его входах будет «О. Так, например, появление импульса на выходе элемента И 11 свидетельствует о том, что в данном канальном коде разряды QQ, Q7, Q8 имеют состояние «О и могут быть устранены из передачи. Таким образом, канальные коды активных каналов на выходе блока 4 могут содержать 8 разрядов

(импульсы на выходах элементов ИЛИ 7, 8, 9 отсутствуют), 7 разрядов (импульс на выходе элемента ИЛИ 7), 6 разрядов (имнульс на выходе элемента ИЛИ 8) или 5 разрядов (имнульс на выходе элемента ИЛИ 9). На выходе одного из элементов И И, на входы которых соответствующим образом подаются от генератора 5 разрядные последовательности Р7, Р6 и Р5, в нужной временной позиции (Р7, Р6 или Р5) появится импульс, который через элемент ИЛИ 10 по шине «Счит поступает в блок 4 и свидетельствует о том, что считывание данного канального кода закончено и начинается считывание следующего канального кода, который аналогичным образом анализируется в блоке 6. Обозначение конца канального кода осуществляется путем передачи в групповой линейный тракт последнего информационного разряда в той же полярности, какую имел предыдущий разряд данного кода.

На приеме блок 16 управляет записью канальных кодов в ячейки памяти блока 15. Определитель 17 формирует свой импульс на выходе «-J- при приеме сигнала положительной полярности и на выходе «- приеме сигнала отрицательной полярности.

Выходы определителя 17 подключены к соответствующим установочным входам триггера 18 и к входам элементов И 20. К другим входам элементов И 20 через элементы 19, обеспечивающие задержку на один такт, нодключены соответствующие выходы триггера 18. Таким образом, на выходе одного из элементов И 20 появится импульс в том случае, если определитель 17 зафиксирует наличие в поступающих канальных кодах двух подряд следующих импульсов одной полярности (положительной или отрицательной). Импульс на выходе элемента ИЛИ 21 свидетельствует о том, что закончена запись в блок 15 очередного канального кода (шина «Зап) и начинается запись следующего канального кода. Вместо исключенных на передаче нулей в старших разрядах канальных кодов в ячейках памяти блока 15 записываются «О.

Р1з блока 15 в управляющий блок 14 поступает адресная ииформация (шина «Адр), на основе которой управляющий блок 14 осуществляет считывание информации (шииа «Счит) в тракты систем с

икм.

Технико-экономические показатели предлагаемого устройства можно оценить следующим образом. Как показали расчеты, среднее количество нулей Кш исключаемых при передаче речевых сигналов в расчете на один канальный код составляет . Учитывая, что в известной системе количество разрядов в каждом канальном коде составляет , можно подсчитать, что

в среднем происходит сокращение канальных кодов на величину, равную

.100 25%.

АКО

Это означает, что в предлагаемой статистической системе связи ИКМ можно в среднем на 25% увеличить коэффициент использования пропускной способности группового линейного тракта, подключив систем с ИКМ вместо Л систем в известной системе, причем

,25.

ЛЛ

Формула изобретения

1. Устройство уплотнения для системы свя зи с импульсно-кодовой модуляцией содержащее на передающей стороне системы связи цифровой пороговый детектор, каждый из «я информационных входов которого соединен с соответствующим информационным входом блока буферной памяти

и выходом соответствующего источника информационных сигналов, причем управляющий вход цифрового порогового детектора соединен с первым выходом генератора тактовой частоты, второй выход которого

подключен к первому входу управляющего блока, второй вход которого соединен с выходом цифрового порогового детектора, а адресный и записывающий выходы управляющего блока соединены с соответствующими входами блока буферной памяти, информационный выход которого через групповой линейный тракт соединен с расположенными на приемной стороне системы связи блоком буферной памяти, каждый из

«п информационных выходов которого соединен с выходом соответствующего приемника ииформационных сигналов, при этом адресный выход и считывающий в.ход блока буферной памяти соединен соответственно с адресным входом и считывающим выходом управляющего блока, управляющий вход которого подключен к первому выходу генератора тактовой частоты, второй выход которого соединен с унравляющим входом блока буферной памяти, отличающееся тем, что, с целью повышения пропускной способности группового линейного тракта, на передающей стороне системы связи введен блок анализа

сигналов, причем первый, второй и третий входы блока анализа сигналов соединены соответственно с первым, вторым и третьим дополнительными выходами блока буферной памяти, четвертый, пятый и шестой

входы блока анализа сигналов соединены соответственно с первым, вторым и третьим дополнительными выходами генератора тактовой частоты, при этом выход блока анализа сигналов подключен к дополнительному входу блока буферной памяти, а

| название | год | авторы | номер документа |

|---|---|---|---|

| Ретранслятор асинхронных сигналов с импульсно-кодовой модуляцией | 1990 |

|

SU1786671A1 |

| Устройство для статистического уплотнения линии передачи | 1984 |

|

SU1228292A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Анализатор гистограммы отклонений напряжения | 1982 |

|

SU1104530A1 |

| Электронный коммутатор | 1988 |

|

SU1626444A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Устройство для ввода информации | 1987 |

|

SU1529231A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

Авторы

Даты

1980-11-07—Публикация

1978-10-03—Подача