пульсо на выходе распределителя, т.е. угла управления 2.

Однако быстродействие устройства ограничено тем, что измерение фазы управляющих импульсов производится ,, один раз за период частоты питающей сети.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем,, что известное устройство,, содержащее фазовый детектор и последовательно включенные элемент сравнения, одним из входов подключенный к источнику управляющего сигнала,, общий управляемый генератор,, подключенный к двум источникам сигналов смещения и распределитель импульсов,, один из выходов которого подключен, к первому входу фазового детектора, второй вход которого соединен с соответствующей фазой питающей сети, снабжено интегратором с ключом сброса, двумя блоками запоминания, тремя ключами,, элементом задержки, коньюнктором, инвертором сумматором и источником опорного сигнала, входы которого подключены соответственно к выходу элемента сравнения и его входу, подключенному также к выходу первого блока запоминания, вход которого через первый ключ соединен с выходом интегратора,, а через второй ключ - с выходом второго блока запоминания, вход которого соединен с выходом сум.матора через третий ключ, вход управления которым подключен к выходу общего управляемого генератора и к первому входу коньюнктора, выход которого подключен к управляющему входу второго ключа через элемент задержки, а второй вход через инвертор соединен с управляющим входом первого ключа и первым входом фазового детектора, выход которого подключен к управляющему входу ключа сброса интегратора, вход которого подключен к источнику опорного сигнала.

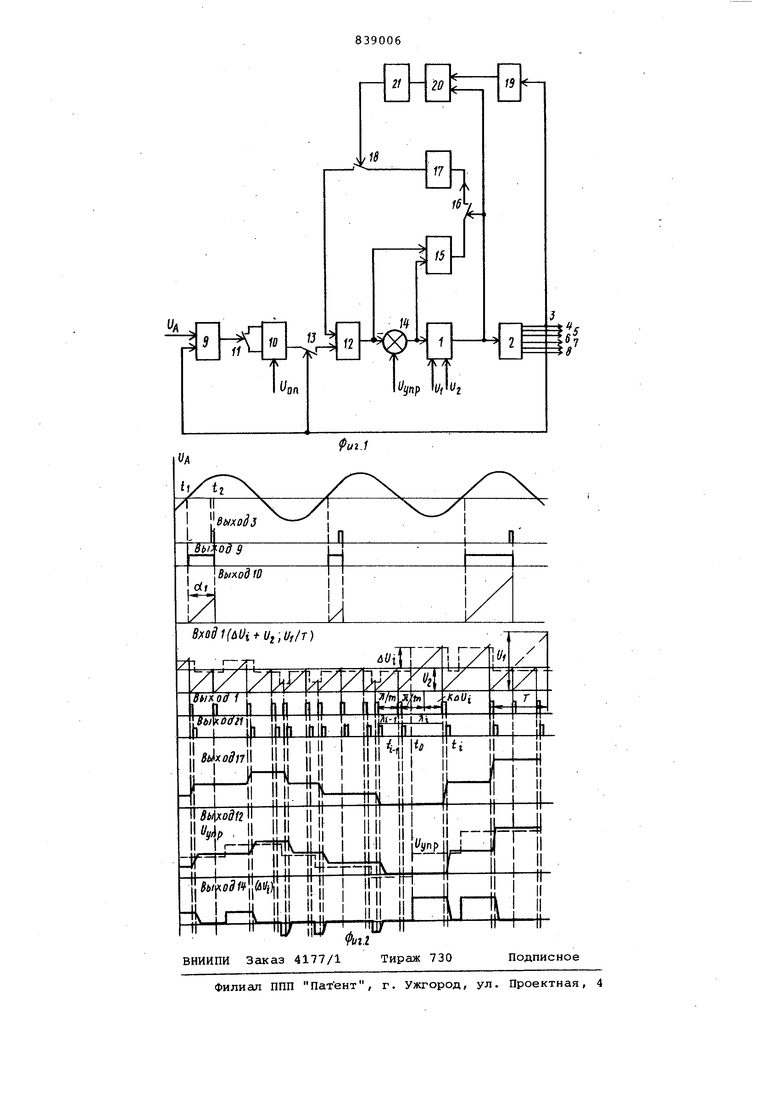

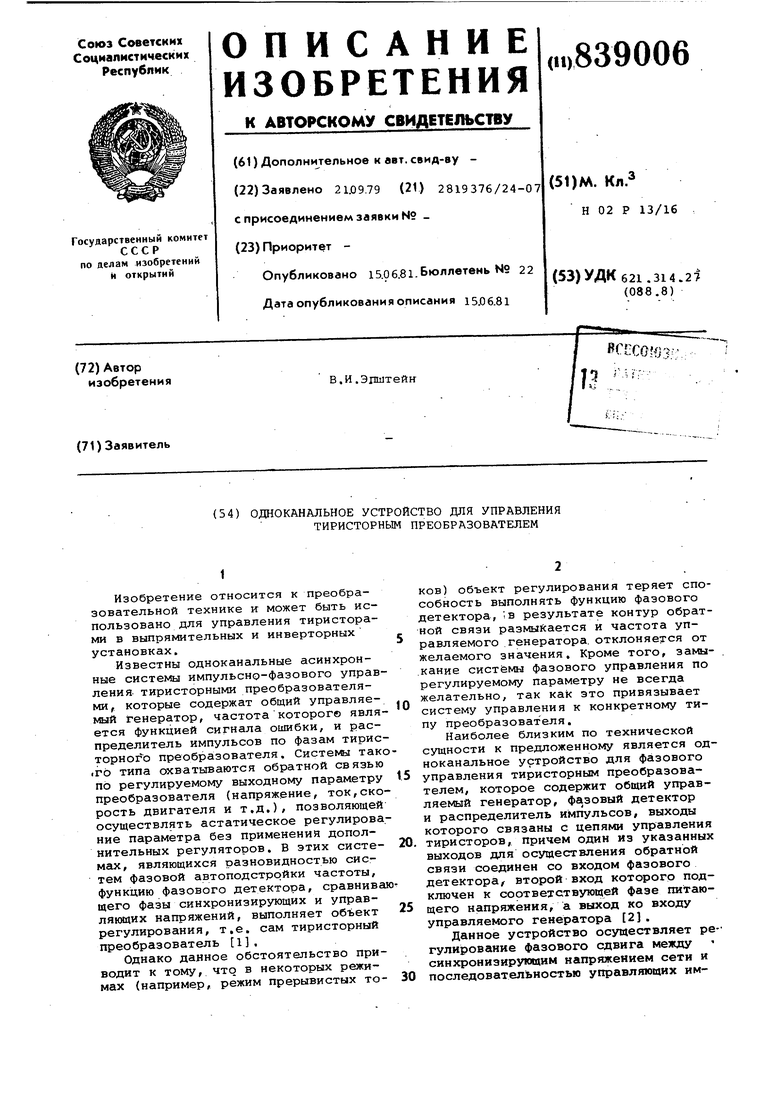

На фиг. 1 показана структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы.

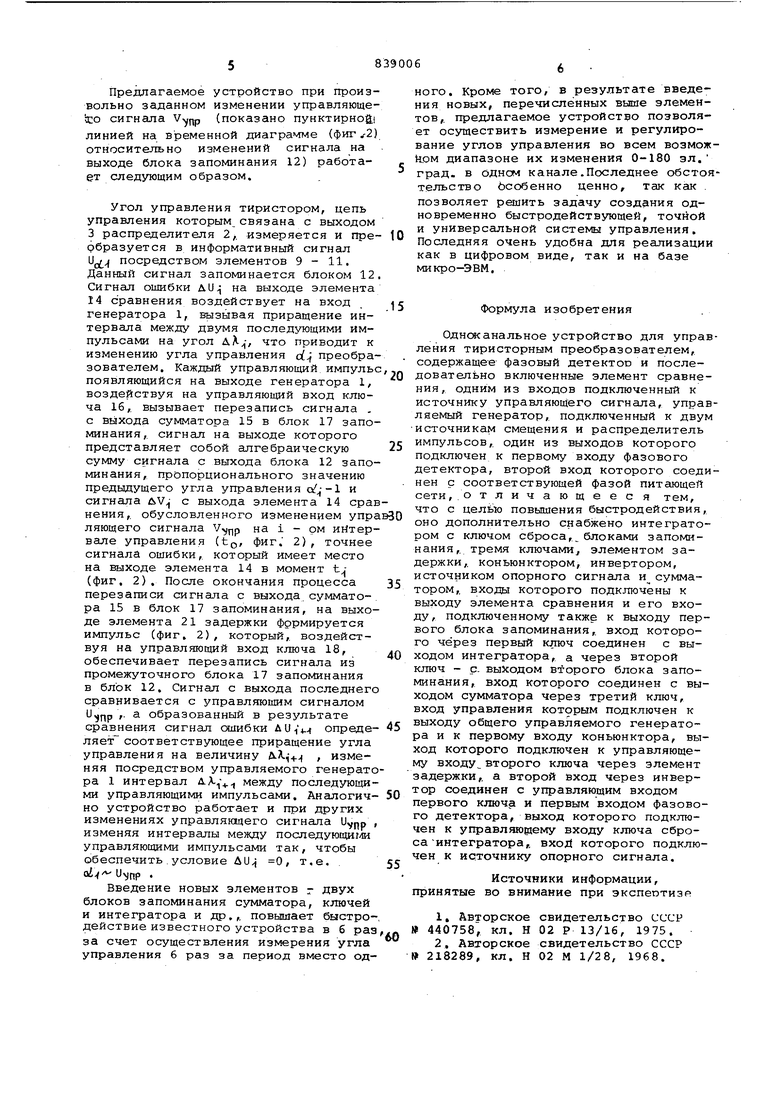

Предложенное устройство содержит общий управляемой генератор 1,. входо подключенный ко входу распределителя 2 импульсов, выходы 3-8 которого связаны с цепями управления тиристоров,, причем один из указанных выходов 3 для осуществления обратной связи по углу управления oLсоединен со входом фазового детектора 9, второй вход которого подключен к соответствующей фазе питающего напряжения Од, Угол управлений сС тиристором, соединенным с шиной 3 распределителя, определяется как,, интервал (фиг. 2) между моментом t, соответствующим переходу через ноль напряжения Уд, и моментом tt появления управляющего

импульса на выходе 3 распределителя 2. Для преобразования данного интерг вала в аналоговый сигнал используется интегратор 10,. подключенный кисточнику опорного сигнала Л , Сбро интегратора 10 осуществляется ключом 11,. вход управления которого подключен к выходу фазового детектора. Далее сигнал, пропорциональный измеренному углу управления, с выхода 10 интегратора (фиг,, 2) запоминается блоко 12 запоминания, причем момент запоминания определяется импульсом с выхода 3 распределителя, для чего указанный выход подключен к управляющему входу ключа 13, соединяющего выход интегратора 10 со входом блока 12 запоминания. Напряжение с выхода блока 12 запоминания, имеющее ступенчатую форму (фиг, 2),, подается на вход элемента 14 сравнения, другой вход которого подключен к источнику управляющего сигнала и,р , а выход ко входу управляемого генератора 1,, на выходе которого формируется последовательность управляющих импульсов, показанная на временной диаграмме (фиг. 2). Для повышения быстродействия устройства в него вводится дополнительный контур местной отрицательной обратной связи, образованный последовательно включенными сумматором 15, ключом 16 и блоком 17 запоминания. Причем выход блока 17 запоминания через ключ 18 соединен со входом блока 12 запоминания, выход которого подключен к входу сумматора 15, другой вход которого подключен к выходу элемента 14 сравнения Управляющий вход ключа 16 соединение выходом управляемого генератора 1,вы ходные импульсы которого определяют моменты перезаписи сигнала с выхода сумматора 15 в запоминающее устройство 17,

Моменты перезаписи сигнала с выхода блока запоминания 17 (фиг. 2) в блок 12 запоминания посредством ключа 18 определяются логической цепочкой, состоящей из инвертора 19,коньюктора 20 и элемента 21 задержки,

i - ый интервал Х между импульсами на выходе управляемого генератора 1 определяется в соответствии с выражением

тс

А,; - -Т 1 Tt/w- фазовый сдвиг (определяемый фазностью и структурой преобразователя) между двумя, последующими импульсами управления, при нулевом сигнале uV О на выходе элемента 14 сравнения;

- фазовый сдвиг импульсов управления, обусловленный сигналом оишбки &и на выходе Элемента 14 сравнения;

к - коэффициент пропорциональности. Предлагаемое устройство при произвольно заданном изменении управляющеico сигнала (показано пунктирно линией на временной диаграмме () относительно изменений сигнала на выходе блока запоминания 12) работает следующим образом. Угол управления тиристором, цепь управления которым связана с выходом 3 распределителя 2,, измеряется и прербразуется в информативный сигнал di посредством элементов 9-11. Данный сигнал запоминается блоком 12 Сигнал ошибки ди на выходе элемента 14 сравнения воздействует на вход генератора 1, вызывая приращение интервала между двумя последующими импульсами на угол , что приводит к изменению угла управления d. преобразователем. Каждый управляющий импульс появляющийся на выходе генератора 1, воздействуя на управляющий вход ключа 16,, вызывает перезапись сигнала . с выхода сумматора 15 в блок 17 запоминания,, сигнал на выходе которого представляет собой алгебраическую сумму сигнала с выхода блока 12 запоминания, пропорционального значению предыдущего угла управления и сигнала с выхода элемента 14 срав нения,, обусловленного изменением упра ляющего сигнала V( на i - ом иНтервёше управления (t, фиг. 2) , точнее сигнала ошибки, который имеет место на выходе элемента 14 в момент (фиг. 2). После окончания процесса перезаписи сигнала с выхода сумматора 15 в блок 17 запоминания, на выходе элемента 21 задержки фррмируется импульс (фиг. 2), который,, воздействуя на управля1ющий вход ключа 18, обеспечивает перезапись сигнала из промежуточного блока 17 запоминания в блок 12. Сигнал с выхода последнего сравнивается с управляющим сигналом ,. а образованный в результате Jllr сравнения сигнал сшибки AUi+. определяет соответствующее приращение угла управления на величину i изменяя посредством управляемого генерато ра 1 интервал . между последующими управляющими импульсами. Аналогично устройство работает и при других изменениях управлягацего сигнала Uypp изменяя интервалы между последующигли управляющими импульсами так, чтобы обеспечить . условие ULI,j 0, т.е. tti- UNjnp . Введение новых элементов г двух блоков запоминания сумматора, ключей и интегратора и др.,, повышает быстродействие известного устройства в 6 раз за счет осуществления измерения угла управления 6 раз за период вместо одного. Кроме того, в результате введения новых, перечисленных выше элементов,, предлагаемое устройство позволяет осуществить измерение и регулирование углов управления во всем возможном диапазоне их изменения 0-180 эл. град, в одном канале.Последнее обстоятельство Ьсобенно ценно, так как позволяет решить задачу создания одновременно быстродействующей, точной и универсальной системы управления. Последняя очень удобна для реализации как в цифровом виде, так и на базе микро-ЭВМ. Формула изобретения Одноканальное устройство для управления тиристорным преобразователем, содержащее фазовый детектоо и последовательно включенные элемент сравнения, одним из входов подключенный к источнику управляющего сигнала, управляемый генератор,, подключенный к двум источникам смещения и распределитель импульсов,, один из выходов которого подключен к первому входу фазового детектора, второй вход которого соединен с соответствующей фазой питаиощей сети, отличающеес я тем, что с целЬК) повышения быстродействия, оно дополнительно снабжено интегратором с ключом сброса, блоками запоминания,, тремя ключaми элементом задержки,, коньюнктором, инвертором, источником опорного сигнала и сумматором,, входы которого подключены к выходу элемента сравнения и его входу, подключенному также к выходу первого блока запоминания, вход которого через первый ключ соединен с выходом интегратора, а через второй ключ - с. выходом второго блока запоминания, вход которого соединен с выходом сумматора через третий ключ, вход управления которым подключен к выходу общего управляемого генератора и к первому входу коньюнктора, выход которого подключен к управляющему входу второго ключа через элемент задержки,, а второй вход через инвертор соединен с управляющим входом первого ключа и первым входом фазового детектора, выход которого подключен к управляющему входу ключа сброса интегратора,, вхой которого подключен к источнику опорного сигнала. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 440758, кл. Н 02 Р 13/16, 1975. 2,Авторское свидетельство СССР 218289, кл. Н 02 М 1/28, 1968.

УА

L7

| название | год | авторы | номер документа |

|---|---|---|---|

| Одноканальное устройство для фазового управления вентильным преобразователем | 1977 |

|

SU720661A1 |

| Система управления инерционным экстремальным объектом | 1986 |

|

SU1456930A1 |

| Одноканальное устройство для фазового управления статическим преобразователем | 1977 |

|

SU736344A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Устройство для управления мостовым инвертором со слежением за кривой выходного напряжения | 1984 |

|

SU1239810A1 |

| УСТРОЙСТВО ПЕЛЕНГОВАНИЯ И АНАЛИЗА СИГНАЛА ИМПУЛЬСНЫХ РЛС С КОММУТАЦИОННЫМ ОБЪЕДИНЕНИЕМ ПРИЕМНЫХ КАНАЛОВ | 1989 |

|

SU1841032A1 |

| Устройство для управления непосредственным преобразователем частоты | 1981 |

|

SU964961A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ ПОМЕХ | 1988 |

|

SU1841099A1 |

| Преобразователь координат | 1980 |

|

SU886011A1 |

Авторы

Даты

1981-06-15—Публикация

1979-09-21—Подача