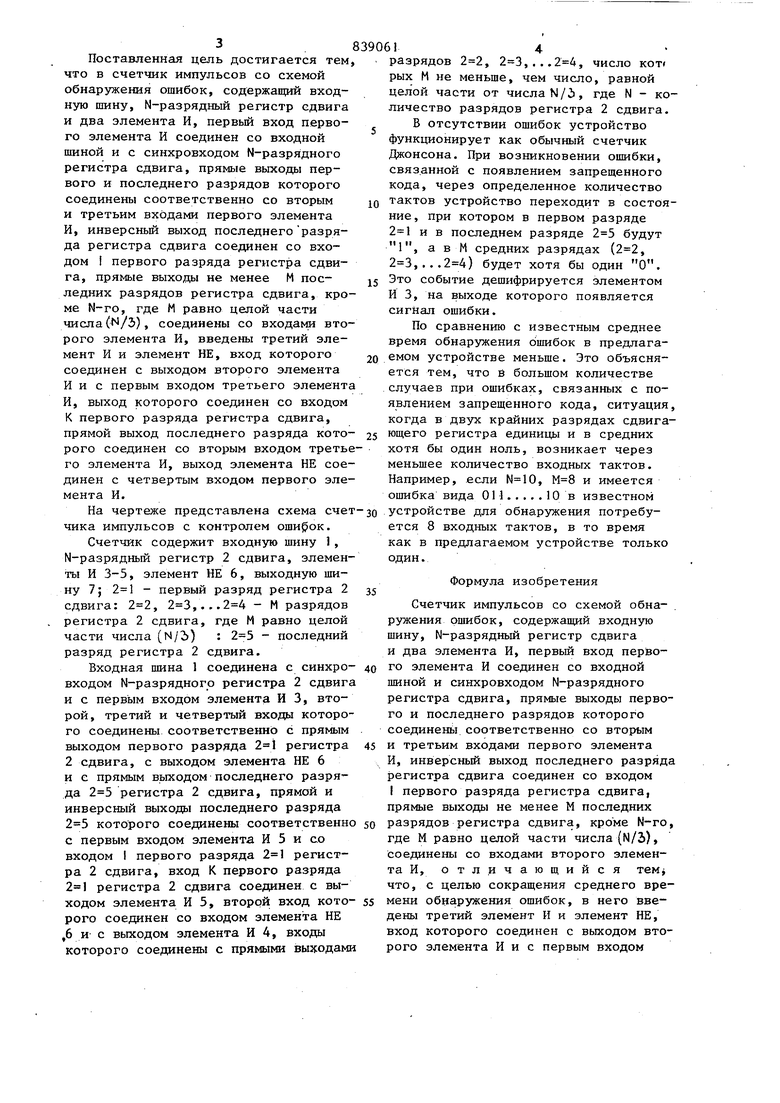

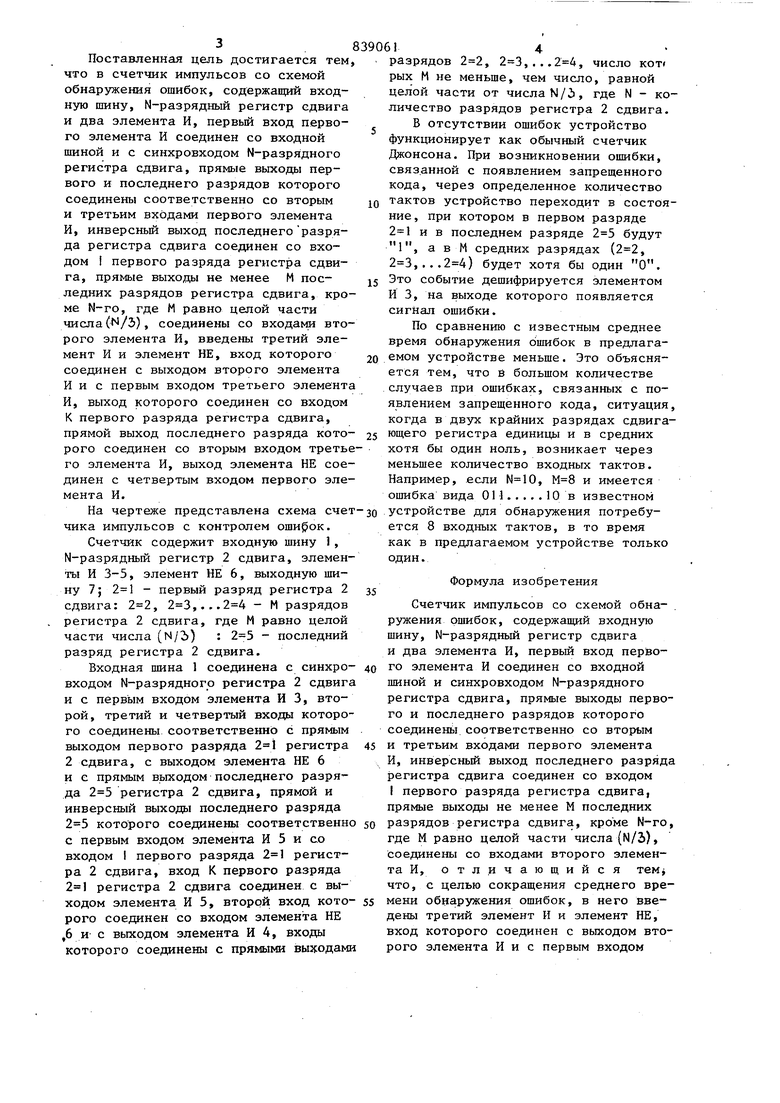

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств. Известно устройство контроля счетчиков, работаюЕцих в циклическом режиме, содержащее кольцевой регистр сдви га, два элемента И, два триггера и элемент ИЛИ l3 Недостатком этого устройства Является его относительная сложность. Известно также устройство, содержащее входную шину, N- разрядньй регистр сдвига и два элемента И, первый вход первого элемента И соединен со входной шиной и с синхровходом N-pasрядного регистра сдвига, прямые выходы первого и последнего разрядов которого соединены соответственно со вторым и третьим входами первого элемента И, инверсные выходы предпоследнего и последнего разрядов регистра сдвига соединены соответственно с чет зертым входом первого элемента И и со входом 3 первого разряда регистра сдвига, прямые выходы не менее М последних разрядов которого, кроме N-ro, где М равно целой части числа (N/3), соединены со входами второго элемента И, выход которого соединен со входом К первого разряда регистра сдвига. При отсутствии ошибок устройство функционирует как обычный счетчик Джонсона. При возникновении ошибок, связанных с появлением в счетчике запрещенного кода, в счетчике через определенное количество тактов появляется код 1ХХ....Х01, который шифруется первым элементом И, на выходе которого формируется сигнал ошибки И. Недостатком данного устройства является большое время, необходимое для обнаружения ошибки. Цель изобретения - сокращение среднего времени обнаружения ошибок. Поставленная цель достигается тем что в счетчик импульсов со схемой обнаружения ошибок, содержащий входную шину, N-разрядный регистр сдвига и два элемента И, первьй вход первого элемента И соединен со входной шиной и с синхровходом N-разрядного регистра сдвига, прямые выходы первого и последнего разрядов которого соединены соответственно со вторым и третьим входами первого элемента И, инверсньш выход последнего разряда регистра сдвига соединен со входом I первого разряда регистра сдвига, прямые выходы не менее М последних разрядов регистра сдвига, кроме N-ro, где М равно целой части числа(N/5), соединены со входами второго элемента И, введены третий элемент И и элемент НЕ, вход которого соединен с выходом второго элемента И и с первым входом третьего элемента И, выход которого соединен со входом К первого разряда регистра сдвига, прямой выход последнего разряда которого соединен со вторым входом третье го элемента И, выход элемента НЕ соединен с четвертым входом первого элемента И. На чертеже представлена схема счет чика импульсов с контролем ошибок. Счетчик содержит входную шину 1, N-разрядный регистр 2 сдвига, элементы И 3-5, элемент НЕ 6, выходную шину 7; - первый разряд регистра 2 сдвига: , ,... - М разрядов регистра 2 сдвига, где М равно целой части числа (N/i) : - последний разряд регистра 2 сдвига. Входная шина 1 соединена с синхровходом N-разрядногр регистра 2 сдвига и с первым входом элемента И 3, второй, третий и четвертый входы которо го соединены соответственно с прямым выходом первого разряда регистра 2 сдвига, с выходом элемента НЕ 6 и с прямым выходом последнего разряда регистра 2 сдвига, прямой и инверсный выходы последнего разряда которого соединены соответственн с первым входом элемента И 5 и со входом I первого разряда регистра 2 сдвига, вход К первого разряда регистра 2 сдвига соединен с выходом элемента И 5, второй вход кото рого соединен со входом элемента НЕ 6 и с выходом элемента И 4, входы которого соединены с прямыми выходам 1 разрядов , ,..., число кот рых М ие меньше, чем число, равной целой части от числа N/i, где N - количество разрядов регистра 2 сдвига. В отсутствии ошибок устройство функционирует как обычный счетчик Джонсона. При возникновении ошибки, связанной с появлением запрещенного кода, через определенное количество тактов устройство переходит в состояние, при котором в первом разряде и в последнем разряде будут 1, а в М средних разрядах (, ,...) будет хотя бы один О. Это событие дешифрируется элементом И 3, на выходе которого появляется сигнал ошибки. По сравнению с известным среднее время обнаружения ошибок в предлагаемом устройстве меньше. Это объясняется тем, что в большом количестве случаев при ошибках, связанных с появлением запрещенного кода, ситуация, когда в двух крайних разрядах сдвигающего регистра единицы и в средних хотя бы один ноль, возникает через меньшее количество входных тактов. Например, если , и имеется ошибка вида 01110 в известном устройстве для обнаружения потребуется 8 входных тактов, в то время как в предлагаемом устройстве только один. Формула изобретения Счетчик импульсов со схемой обнаружения ошибок, содержащий входную шину, N-разрядный регистр сдвига и два элемента И, первый вход первого элемента И соединен со входной шиной и синхровходом М-разрядного регистра сдвига, прямые выходы первого и последнего разрядов которого соединены соответственно со вторым и третьим входами первого элемента И, инверсный выход последнего разряда регистра сдвига соединен со входом I первого разряда регистра сдвига, прямые выходы не менее М последних разрядов регистра сдвига, кроме N-ro, где М равно целой части числа (N/3), соединены со входами второго элемента И, отличающийся тем что, с целью сокращения среднего времени обнаружения ошибок, в него введены третий элемент И и элемент НЕ, вход которого соединен с выходом второго элемента И и с первым входом

третьего элемента И, выход которого соединен со входом К первого разряда регистра сдвига, прямой выход по,следнего разряда которого соединен со вторым входом третьего элемента И, выход элемента НЕ соединен с четвер тым входом первого элемента И.

Источники информации, принятые во внимайие при экспертизе

1.Авторское свидетельство СССР № 416883, кл. Н 03 К 21/34, 1974.

2.Авторское свидетельство СССР

по заявке № 2668097/18-21, кл. Н 03 К 27.09.78.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кольцевой счетчик с устройством обнаружения ошибок | 1981 |

|

SU1015500A1 |

| Кольцевой счетчик с устройством для обнаружения ошибок | 1979 |

|

SU866749A1 |

| Счетчик джонсона | 1979 |

|

SU809582A1 |

| Устройство для контроля структурного кода | 1990 |

|

SU1748256A1 |

| Счетчик джонсона | 1978 |

|

SU746783A1 |

| Счетное устройство по модулю три с контролем | 1983 |

|

SU1190518A1 |

| Система для исправления ошибок при передаче N-разрядных кодовых слов | 1985 |

|

SU1336254A1 |

| Счетчик импульсов | 1978 |

|

SU777825A1 |

| Сигнатурный анализатор | 1985 |

|

SU1367016A1 |

| Арифметическое устройство для выполнения операций над несколькими числами | 1986 |

|

SU1348822A2 |

I

Z J

г J

f--2

г

z

Авторы

Даты

1981-06-15—Публикация

1979-09-20—Подача