Изобретение относится к области вычислительной техники и может быть использовано в системах передачи информации, ,а также для проверки системных шин или линий связи.

Цель изобретения - повышение достоверности передаваемой информации за счет исправления двойных ошибок.

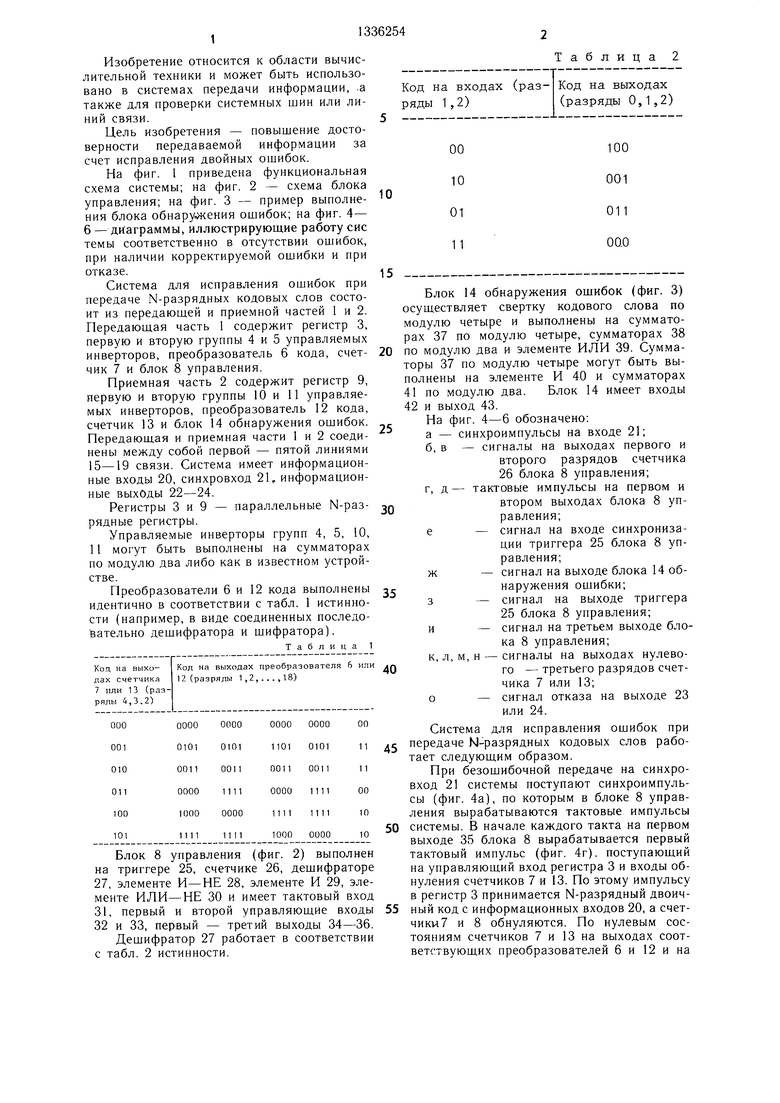

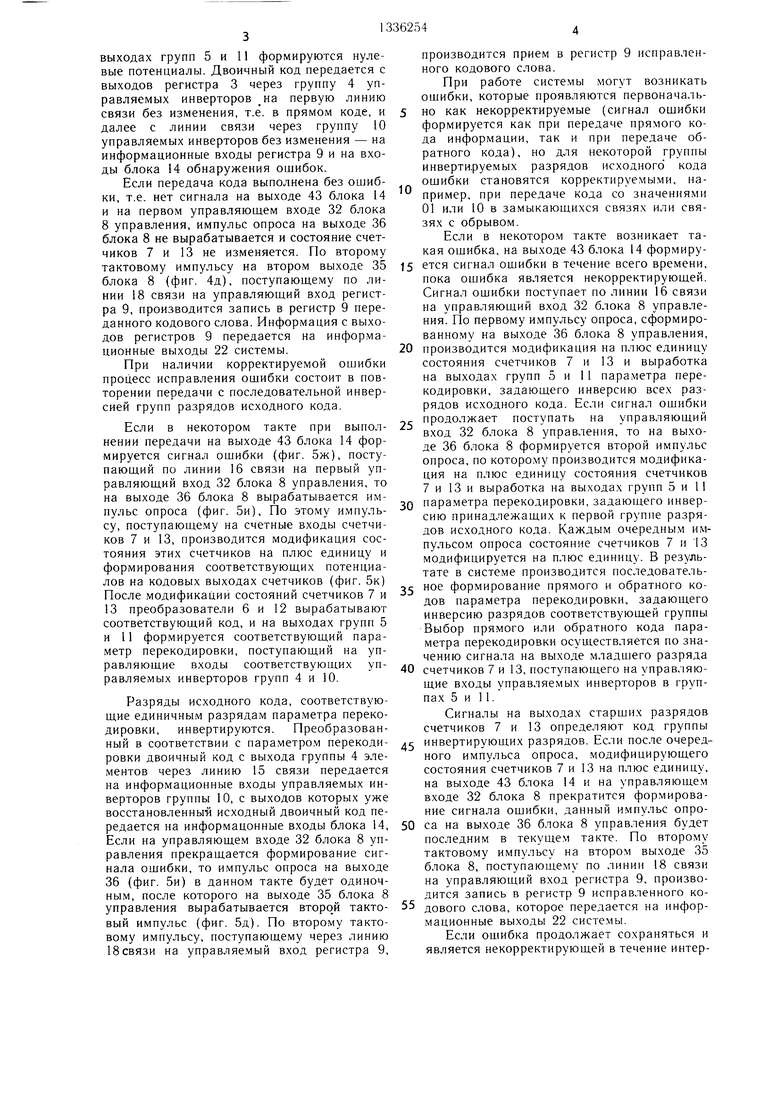

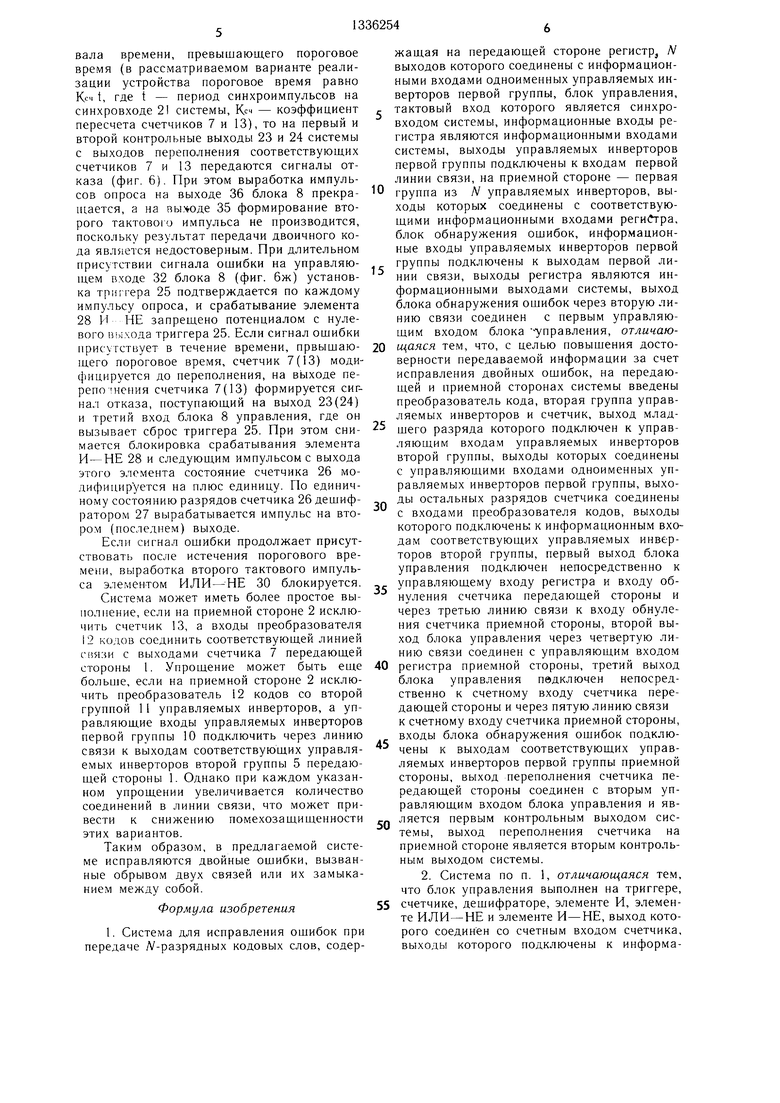

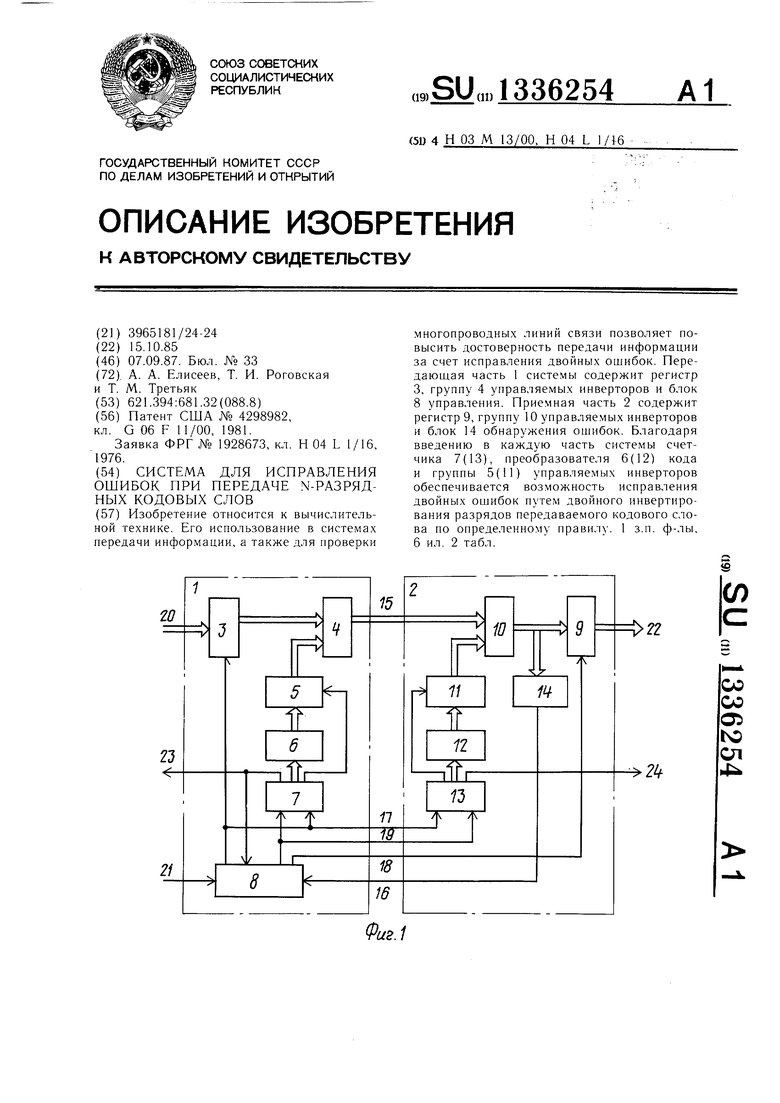

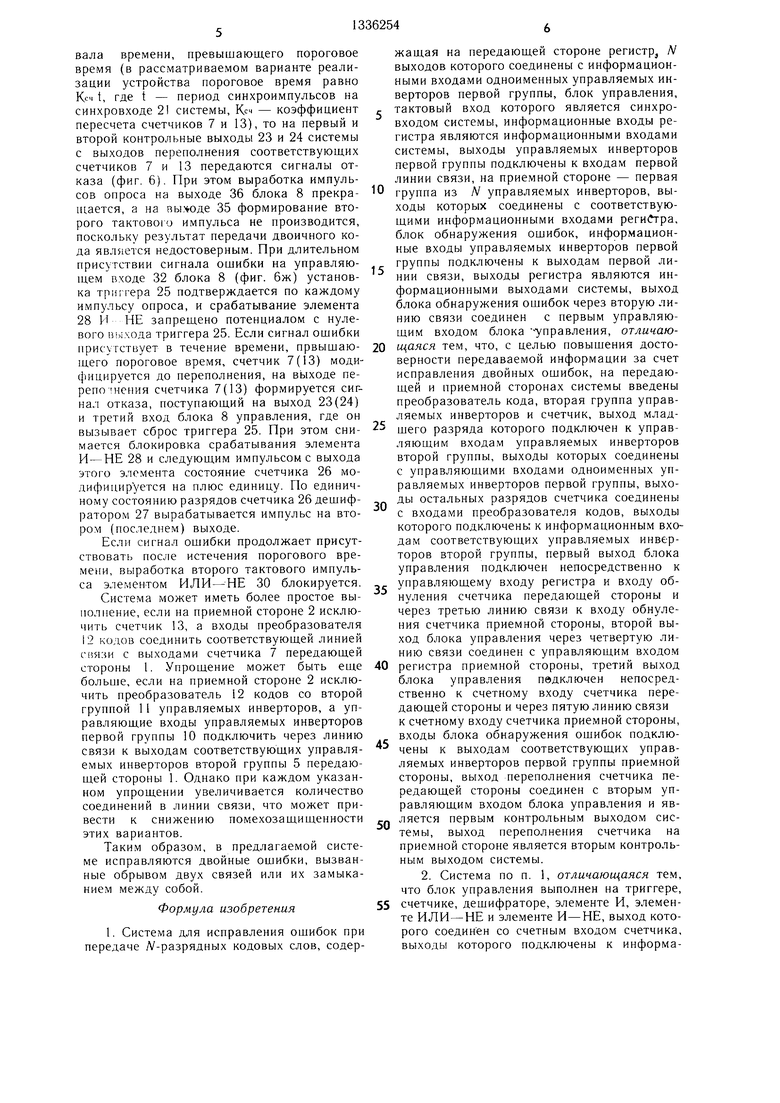

На фиг. 1 приведена функциональная схема системы; на фиг. 2 - схема блока управления; на фиг. 3 - пример выполнения блока обнаружения ошибок; на фиг. 4- 6 - диаграммы, иллюстрируюш,ие работу сие темы соответственно в отсутствии ошибок, при наличии корректируемой ошибки и при отказе.

Система для исправления ошибок при передаче N-разрядных кодовых слов состоит из передающей и приемной частей 1 и 2. Передающая часть 1 содержит регистр 3, первую и вторую группы 4 и 5 управляемых инверторов, преобразователь 6 кода, счет- чик 7 и блок 8 управления.

Приемная часть 2 содержит регистр 9, первую и вторую группы 10 и 11 управляемых инверторов, преобразователь 12 кода, счетчик 13 и блок 14 обнаружения ощибок. Передаюш,ая и приемная части 1 и 2 соединены между собой первой - пятой линиями 15-19 связи. Система имеет информационные входы 20, синхровход 21,. информационные выходы 22-24.

Регистры 3 и 9 - параллельные N-раз- рядные регистры.

Управляемые инверторы групп 4, 5, 10, 11 могут быть выполнены на сумматорах по модулю два либо как в известном устройстве.

Преобразователи 6 и 12 кода выполнены идентично в соответствии с табл. 1 истинности (например, в виде соединенных последовательно дешифратора и шифратора).

Таблица 1

Блок 8 управления (фиг. 2) выполнен на триггере 25, счетчике 26, дешифраторе 27, элементе И-НЕ 28, элементе И 29, элементе ИЛИ-НЕ 30 и имеет тактовый вход 31, первый и второй управляющие входы 32 и 33, первый - третий выходы 34-36.

Дешифратор 27 работает в соответствии с табл. 2 истинности.

Таблица 2

Код на входах (разряды 1 ,2)

Код на выходах (разряды 0,1,2)

00 10 01 11

100 001 011 00.0

0

5

0

5

5

Блок 14 обнаружения ошибок (фиг. 3) осуществляет свертку кодового слова по модулю четыре и выполнены на сумматорах 37 по модулю четыре, сумматорах 38 по модулю два и элементе ИЛИ 39. Сумматоры 37 по модулю четыре могут быть выполнены на элементе И 40 и сумматорах

41по модулю два. Блок 14 имеет входы

42и выход 43.

На фиг. 4-6 обозначено;

а - синхроимпульсы на входе 21;

б, в - сигналы на выходах первого и второго разрядов счетчика 26 блока 8 управления;

г, д - тактовые импульсы на первом и втором выходах блока 8 управления;

е- сигнал на входе синхронизации триггера 25 блока 8 управления;

ж- сигнал на выходе блока 14 обнаружения ошибки;

3- сигнал на выходе триггера

25 блока 8 управления;

и- сигнал на третьем выходе блока 8 управления;

к, л, м, н - сигналы на выходах нулевого - третьего разрядов счетчика 7 или 13;

о- сигнал отказа на выходе 23

или 24.

Система для исправления ошибок при передаче N-разрядных кодовых слов работает следующим образом.

При безошибочной передаче на синхровход 21 системы поступают синхроимпульсы (фиг. 4а), по которым в блоке 8 управления вырабатываются тактовые импульсы системы. В начале каждого такта на первом выходе 35 блока 8 вырабатывается первый тактовый импульс (фиг. 4г). поступающий на управляющий вход регистра 3 и входы обнуления счетчиков 7 и 13. По этому импульсу в регистр 3 принимается N-разрядный двоичный код с информационных входов 20, а счетчики 7 и 8 обнуляются. По нулевым состояниям счетчиков 7 и 13 на выходах соответствующих преобразователей 6 и 12 и на

выходах групп 5 и 11 формируются нулевые потенциалы. Двоичный код передается с выходов регистра 3 через группу 4 управляемых инверторов на первую линию связи без изменения, т.е. в прямом коде, и далее с линии связи через группу 10 управляемых инверторов без изменения - на информационные входы регистра 9 и на входы блока 14 обнаружения ошибок.

Если передача кода выполнена без ошибки, т.е. нет сигнала на выходе 43 блока 14 и на первом управляюш,ем входе 32 блока 8 управления, импульс опроса на выходе 36 блока 8 не вырабатывается и состояние счетчиков 7 и 13 не изменяется. По второму тактовому импульсу на втором выходе 35 блока 8 (фиг. 4д), поступающему по линии 18 связи на управляющий вход регистра 9, производится запись в регистр 9 переданного кодового слова. Информация с выходов регистров 9 передается на информационные выходы 22 системы.

При наличии корректируемой ошибки процесс исправления ошибки состоит в повторении передачи с последовательной инверсией групп разрядов исходного кода.

Если в некотором такте при выполнении передачи на выходе 43 блока 14 формируется сигнал ошибки (фиг. 5ж), поступающий по линии 16 связи на первый управляющий вход 32 блока 8 управления, то на выходе 36 блока 8 вырабатывается им- нульс опроса (фиг. 5и), По этому импульсу, поступающему на счетные входы счетчиков 7 и 13, производится модификация состояния этих счетчиков на плюс единицу и формирования соответствующих потенциалов на кодовых выходах счетчиков (фиг. 5к) После модификации состояний счетчиков 7 и 13 преобразователи 6 и 12 вырабатывают соответствующий код, и на выходах групп 5 и 11 формируется соответствующий параметр перекодировки, поступающий на управляющие входы соответствующих управляемых инверторов групп 4 и 10.

Разряды исходного кода, соответствующие единичным разрядам параметра перекодировки, инвертируются. Преобразованный в соответствии с параметром перекодировки двоичный код с выхода группы 4 элементов через линию 15 связи передается на информационные входы управляемых инверторов группы 10, с выходов которых уже восстановленный исходный двоичный код передается на информацонные входы блока 14, Если на управляющем входе 32 блока 8 управления прекращается формирование сигнала ошибки, то импульс опроса на выходе 36 (фиг. 5и) в данном такте будет одиночным, после которого на выходе 35 блока 8 управления вырабатывается второ й тактовый импульс (фиг. 5д). По второму тактовому импульсу, поступающему через линию 18 связи на управляемый вход регистра 9,

0

производится прием в регистр 9 исправленного кодового слова.

При работе системы могут возникать ошибки, которые проявляются первоначально как некорректируемые (сигнал ошибки формируется как при передаче прямого кода информации, так и при передаче обратного кода), но для некоторой группы инвертируемых разрядов исходного кода ошибки становятся корректируемыми, например, при передаче кода со значениями 01 или 10 в замыкающихся связях или связях с обрывом.

Если в некотором такте возникает такая ощибка, на выходе 43 блока 14 формиру5 ется сигнал ощибки в течение всего времени, пока ошибка является некорректирующей. Сигнал ошибки поступает по линии 16 связи на управляющий вход 32 блока 8 управления. По первому импульсу опроса, сформированному на выходе 36 блока 8 управления,

0 производится модификация на плюс единицу состояния счетчиков 7 и 13 и выработка на выходах групп 5 и 11 параметра перекодировки, задающего инверсию всех разрядов исходного кода. Если сигнал ошибки

r продолжает поступать на управляющий вход 32 блока 8 управления, то на выходе 36 блока 8 формируется второй импульс опроса, по которо.му производится модификация на плюс единицу состояния счетчиков 7 и 13 и выработка на выходах групп 5 и 11

0 параметра перекодировки, задающего инверсию принадлежащих к первой группе разрядов исходного кода. Каждым очередным импульсом опроса состояние счетчиков 7 и 13 модифицируется на плюс единицу. В результате в системе производится последователь5 ное формирование прямого и обратного кодов параметра перекодировки, задаюн1,его инверсию разрядов соответствующей группы Выбор прямого или обратного кода параметра перекодировки осуществляется по значению сигнала на выходе младшего разряда

0 счетчиков 7 и 13, поступающего на управ.чяю- щие входы управляемых инверторов в группах 5 и 1 1.

Сигналы на выходах старших разрядов счетчиков 7 и 13 определяют код группы

5 инвертирующих разрядов. Если после очередного импульса опроса, модифицирующего состояния счетчиков 7 и 13 на плюс единицу, на выходе 43 блока 14 и на управляющем входе 32 блока 8 прекратится формирование сигнала ошибки, данный импульс опро0 са на выходе 36 блока 8 управления будет последним в текущем такте. По второму тактовому импульсу на втором выходе 35 блока 8, поступающему по линии 18 связи на управляющий вход регистра 9, производится запись в регистр 9 исправленного ко5 дового слова, которое передается на информационные выходы 22 системы.

Если ошибка продолжает сохраняться и является некорректирующей в течение интервала времени, превышающего пороговое время (в рассматриваемом варианте реализации устройства пороговое время равно Кс 1 t, где t - период синхроимпульсов на синхровходе 2 системы, Кеч - коэффициент пересчета счетчиков 7 и 13), то на первый и второй контрольные выходы 23 и 24 системы с выходов переполнения соответствующих счетчиков 7 и 13 передаются сигналы отказа (фиг. 6). При этом выработка импульсов опроса на выходе 36 блока 8 прекращается, а на выводе 35 формирование второго тактовою импульса не производится, поскольку результат передачи двоичного кода является недостоверным. При длительном присутствии сигнала ошибки на управляющем входе 32 блока 8 (фиг. 6ж) установка триггера 25 подтверждается по каждому импульсу опроса, и срабатывание элемента 28 И НЕ запрещено потенциалом с нулевого триггера 25. Если сигнал ощибки присутствует в течение времени, првышаю- щего пороговое время, счетчик 7(13) модифицируется до переполнения, на выходе переполнения счетчика 7(13) формируется сигнал отказа, поступающий на выход 23(24) и третий вход блока 8 управления, где он вызывает сброс триггера 25. При этом снимается блокировка срабатывания элемента И-НЕ 28 и следующим импульсом с выхода этого элемента состояние счетчика 26 модифицируется на плюс единицу. По единичному состоянию разрядов счетчика 26 дешифратором 27 вырабатывается импульс на втором (последнем) выходе.

Если сигнал ошибки продолжает присутствовать после истечения порогового времени, выработка второго тактового импульса элементом 30 блокируется.

Система может иметь более простое выполнение, если на приемной стороне 2 исключить счетчик 13, а входы преобразователя 12 кодов соединить соответствующей линией сиязи с выходами счетчика 7 передающей стороны I. Упрощение может быть еще больше, если на приемной стороне 2 исключить преобразователь 12 кодов со второй группой 11 управляемых инверторов, а управляющие входы управляемых инверторов первой группы 10 подключить через линию связи к выходам соответствующих управляемых инверторов второй группы 5 передающей стороны 1. Однако при каждом указанном упрощении увеличивается количество соединений в линии связи, что может привести к снижению помехозащищенности этих вариантов.

Таким образом, в предлагаемой системе исправляются двойные ошибки, вызванные обрывом двух связей или их замыканием между собой.

Формула изобретения

1. Система для исправления ощибок при передаче УУ-разрядных кодовых слов, содер0

5

0

5

0

5

0

5

0

5

жащая на передающей стороне регистр ;V выходов которого соединены с информационными входами одноименных управляемых инверторов нервой группы, блок управления, тактовый вход которого является синхро- входом системы, информационные входы регистра являются информационными входами системы, выходы управляемых инверторов первой группы подключены к входам первой линии связи, на приемной стороне - первая группа из N управляемых инверторов, выходы которых соединены с соответствующими информационными входами peги(гpa, блок обнаружения ошибок, информационные входы управляемых инверторов первой группы подключены к выходам первой линии связи, выходы регистра являются информационными выходами системы, выход блока обнаружения ощибок через вторую линию связи соединен с первым управляющим входом блока управления, отличающаяся тем, что, с целью новыщения достоверности передаваемой информации за счет исправления двойных ошибок, на передающей и приемной сторонах системы введены преобразователь кода, вторая группа управляемых инверторов и счетчик, выход младшего разряда которого подключен к управляющим входам управляемых инверторов второй группы, выходы которых соединены с управляющими входами одноименных управляемых инверторов первой группы, выходы остальных разрядов счетчика соединены с входами преобразователя кодов, выходы которого подключены к информационным входам соответствующих управляемых инверторов второй группы, первый выход блока управления подключен непосредственно к управляющему входу регистра и входу обнуления счетчика передающей стороны и через третью линию связи к входу обнуления счетчика приемной стороны, второй выход блока управления через четвертую линию связи соединен с управляющим входом регистра приемной стороны, третий выход блока управления пвдключен непосредственно к счетному входу счетчика передающей стороны и через пятую линию связи к счетному входу счетчика приемной стороны, входы блока обнаружения ошибок подключены к выходам соответствующих управляемых инверторов первой группы приемной стороны, выход переполнения счетчика передающей стороны соединен с вторым управляющим входом блока управления и является первым контрольным выходом системы, выход переполнения счетчика на приемной стороне является вторым контрольным выходом системы.

2. Система по п. 1, отличающаяся тем, что блок управления выполнен на триггере, счетчике, дещифраторе, элементе И, элементе ИЛИ-НЕ и элементе И-НЕ, выход которого соединен со счетным входом счетчика, выходы которого подключены к информационным входам дешифратора, выход нулевого разряда является первым выходом блока управления, выход первого разряда дешифратора подключен к. первому входу элемента И и входу синхронизации триггера, выход второго разряда дешифратора соединен с первым входом элемента ИЛИ-НЕ, инверсный выход триггера подключен к первому входу элемента И-НЕ, второй вход которого и вход разрешения записи дешифратора объединены и являются тактовым входом блока управления, вторые входы элементов И и ИЛИ-НЕ и информационный вход триггера объединены и являются первым управляющим входом блока управления, вход обнуления триггера является вторым управляющим входом блока управления, выход элемента ИЛИ-НЕ и выход элемента И являются соответственно вторым и третьим выходами блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| Устройство для сопряжения модулейВычиСлиТЕльНОй СиСТЕМы C KOHTPO-лЕМ | 1978 |

|

SU807258A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| Устройство для контроля работы оператора | 1987 |

|

SU1497631A1 |

| Оперативное запоминающее устройство с самоконтролем | 1988 |

|

SU1554030A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

Изобретение относится к вычислительной технике. Его использование в системах передачи информации, а также для проверки многопроводных линий связи позволяет повысить достоверность передачи информации за счет исправления двойных ошибок. Передающая часть 1 системы содержит регистр 3, группу 4 управляемых инверторов и блок 8 управления. Приемная часть 2 содержит регистр 9,группу 10 управляемых инверторов и блок 14 обнаружения ошибок. Благодаря введению в каждую часть системы счетчика 7(13), преобразователя 6(12) кода и группы 5(11) управляемых инверторов обеспечивается возможность исправления двойных ошибок путем двойного инвертирования разрядов передаваемого кодового слова по определенному правилу. 1 з.п. ф-лы, 6 ил. 2 табл. со со 05 tsD 01 4;

2 S

Я

б 6

г д

П

П

л

фиг Л

Такт п

Такт

fo.6

Составитель О. Ревинский

Редактор Н. ЕгороваТехред И. ВересКорректор Е. Рошко

Заказ 3815/57Тираж 901Подписиое

ВНИИПИ Государственного комитета СССР,но делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Патент США № 4298982, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Заявка ФРГ № 1928673, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-09-07—Публикация

1985-10-15—Подача