(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1986 |

|

SU1383363A1 |

| Сигнатурный анализатор | 1984 |

|

SU1171797A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1430956A1 |

| Сигнатурный анализатор | 1989 |

|

SU1737452A2 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1837291A1 |

| Сигнатурный анализатор | 1985 |

|

SU1256031A1 |

| Многоканальный сигнатурный анализатор | 1989 |

|

SU1797118A1 |

| Сигнатурный анализатор | 1986 |

|

SU1472907A1 |

| Сигнатурный анализатор | 1984 |

|

SU1262501A1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - расширение функцнональ- возможностей за счет обеспечения дифференцированного контроля последовательностей многоразрядных векторов. Устройство содержит формирователь 3 временных сигналов, элементы И 4, 14, формирователь 5 сигнатур, блок 6 индикации,- формирователь 8 временных интервалов, группу регистров сдвига .11, группу злементов ИСКЛЮЧАЮВЩЕ ИЛИ 12, группу злементов №-НЕ 13, два бу ферных регистра J5, J6. Устройство позволяет дифференцировать ошибки формирования последовательностей горазрядных векторов. 2 ил.

Ш fffU--- 7ff фие.1

00 Од 4

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля дискретных объектов.

Цель изобретения - расширение функциональных возможностей за счет обеспечения дифференцированного конроля последовательностей многоразряных векторов,.

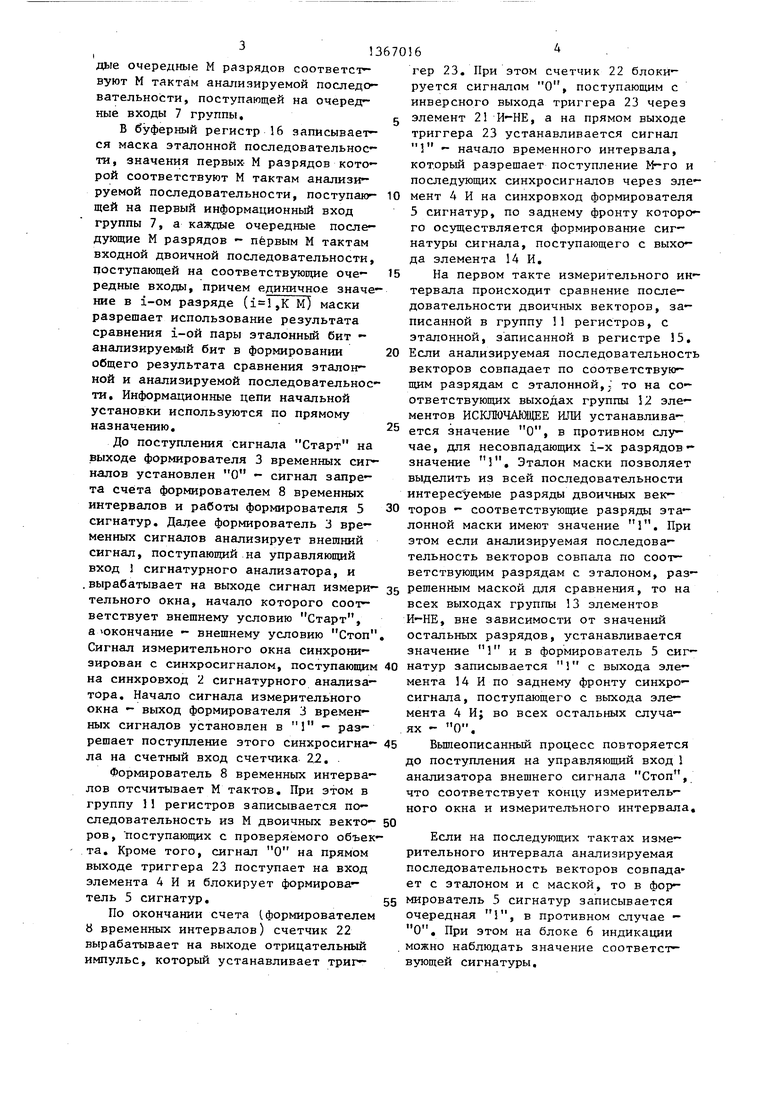

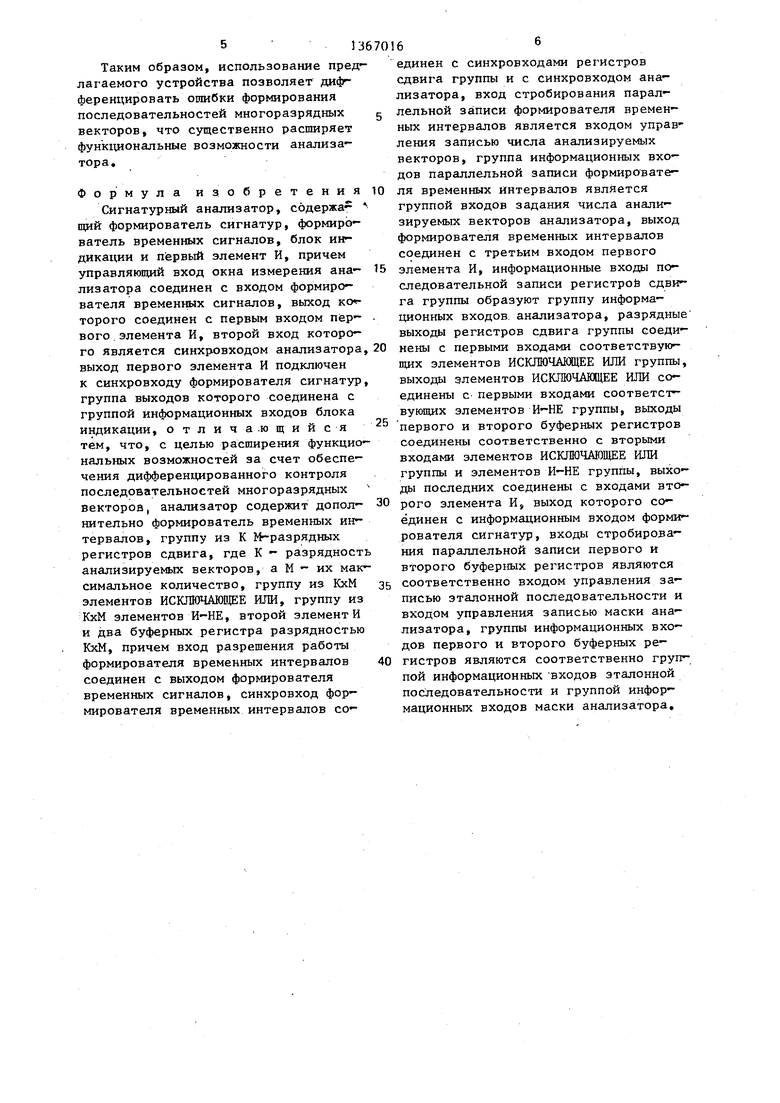

На фиг,1 представлена структурна схема сигнатурного анализатора; на фиг.2 - пример построения формирователя временных интервалов.

Устройство содержит управляющий вход 1 окна измерения, синхровход 2 формирователь 3 временных сигналов, первый элемент 4 И, формирователь 5 сигнатур, блок 6 индикации, группу 7 информационных входов, формирователь 8 временных интервалов, вход 9 управления записью числа анализируемых векторов, группу 10 входов задания числа анализируемых векторов, группу 1 регистров сдвига, группу

12элементов ИСКЛЮЧАЮВдаЕ ИЛИ, группу

13элементов И-НЕ, второй элемент 14 И, два буферных регистр 15 и 16 соответственно, вход 17 управления записью эталонной последовательности, группу 18 информационных входов эталонной последовательности, вход. 19 управления записью маски и группу 20 информационных входов маски анализатора.

Формировател) 3 временных сигналов, первый элемент 4 И, формирователь 5 сигнатур и блок 6 индикации представляют собой известные устройства.

Формирователь 8 временных интервалов представляет, собой устройство, отсчитывающее число тактов, за которое должна происходить запись двоич- ньпс последовательностей в группу 11 регистров.

На фиг.2 приведен пример формирователя 8 временнь х интервалов, который содержит элемент 21 И-НЕ, реверсивный счетчик 22 и триггер 23, второй вход которого соединен с первым входом элемента 21 И-НЕ, выход которого соединен с счетным входом счетчика 22, информационные входы которого являются группой информационньпс входов параллельной записи формирователя 8 временных интервалов, управляющий вход - входом стробирования параллельной записи формирователя 8

временных интервалов и соединен с вторым входом триггера 23, первый вход которого соединен свыходом счетчика.

22, а выход является выходом формирователя 8 временных интервалов,причем второй и третий входы элемента 21 И-НЕ являются соответственно входом разрешения работы и синхровходом формирователя 8 временных интервалов.

Все остальные блоки предлагаемого устройства являются стандартными и легко реализуются на интегральных схемах-, например серии К155, чем разрядность регистров группы 51 и буферных регистров 15 и 16 соответственно выбирается в соответствий с числом проверяемых выходов дискрет ного объекта.

Сигнатурньй анализатор работает следующим образом.

В исходном состоянии анализатор подключается к проверяемому объекту

не показан) следующим образом: управляющий вход 1 - к источнику сигнала; Старт . (Стоп), синхровход 2 - к источнику главного синхросигнала проверяемого объекта, каждый из информа ционных входов группы 7 - к соответ ствзпощим разрядам источника анализируемых последовательностей векторов (например, к разрядам шины проверяемого микропроцессора)о Управляющие

входы 9, 17, 19 и группы входов 10, 18, 20 также могут быть подключены к соответствующим выходам проверяемого объекта, либр к интерфейсным выходам управляющей электронно-вычислитель-

ной машины, в состав которой может быть включен анализатор, либо к лерному наборному регистру при автономном использовании анализатора с ручным управлением. В счетчик 22 форг

мирователя 8 временных интервалов через группу 10 входов записывается прямой двоичный код длины анализируе мой последовательности запрещения формирования сигнатуры фop шpoвaтe- лем 5 сигнатур. При этом триггер 23 устанавливается в О сигналом записи в счетчик 22, поступающим на вход установки в О триггера 23. В регистр 15 записывается двоичная эталонная, последовательность, значение первых М разрядов которой соответствуют М тактам анализируемой последовательности, поступающей на вход группы 7 информационных входов. Каж

дые очередные М разрядов соответст вуют М тактам анализируемой последе вательности, поступающей на очеред ные входы 7 группы,

В бу ферный регистр 16 записывается маска эталонной последовательности, значения первых М разрядов которой соответствуют М тактам анализи-

руемой последовательности, поступаю- 10 мент 4 И на синхровход формирователя

щей на первый информационный вход группы 7, а каждые очередные последующие М разрядов - первым М тактам входной двоичной последовательности, поступающей иа соответствующие очередные входы, причем единичное значение в 1-ом разряде (,К М маски разрешает использование результата сравнения i-ой пары эталонный бит - анализируемый бит в формировании общего результата сравнения эталонной и анализируемой последовательности. Информационные цепи начальной установки используются по прямому назначению.

До поступления сигнала Старт на выходе формирователя 3 временных сигналов установлен О - сигнал запрета счёта формирователем 8 временных интервалов и работы формирователя 5 сигнатур, flajjee формирователь 3 временных сигналов анализирует внешний сигнал, поступающий на управляющий вход 1 сигнатурного анализатора, и

5 сигнатур, по заднему фронту которого осуществляется формирование сигнатуры сигнала, поступающего с выхода элемента 14 И,

15 На первом такте измерительного интервала происходит сравнение последовательности двоичных векторов, записанной в группу 11 регистров, с эталонной, записанной в регистре 5,

20 Если анализируемая последовательность векторов совпадает по соответствующим разрядам с эталонной,; то на соответствующих выходах группы 12 элементов ИСКЛЮЧАЩЕЕ ИЛИ устанавлива ется значение О, в противном случае, для несовпадающих i-x разрядов - значение 1, Эталон маски позволяет выделить из всей последовательности интерес уемые разряды двоичных век-

30 торов - соответствующие разряды эталонной маски имеют значение 1, При

этом если анализируемая последовательность векторов совпала по соответствующим разрядам с эталоном, раз- .вырабатывает на выходе сигнал измери- 35 решенным маской для сравнения, то на тельного окна, начало которого соот всех выходах группы 13 элементов ветствует внешнему условию Старт, И-НЕ, вне зависимости от значений а юкончание - внешнему условию Стоп, остальных разрядов, устанавливается Сигнал измерительного окна синхрони- значение 1 и в формирователь 5 сиг- зирован с синхросигналом, поступающим 40 натур записывается 1 с выхода эле-

на синхровход 2 сигнатурного анализатора. Начало сигнала измерительного окна - выход формирователя 3 временных сигналов установлен в I - разрешает поступление этого синхросигна- ла на счетный вход счетчика 22,

Формирователь 8 временных интервалов отсчитывает М тактов. При этом в группу 11 регистров записывается последовательность из М двоичных векто- ров, поступающих с проверяемого объекта. Кроме того, сигнал О на прямом выходе триггера 23 поступает на вход элемента 4 И и блокирует формирователь 5 сигнатур.

По окончании счета формирователем 8 временных интервалов) счетчик 22 вырабатывает на выходе отрицательный импульс, который устанавливает триг-

гер 23. При этом счетчик 22 блокируется сигналом О, поступающим с инверсного выхода триггера 23 через элемент 21 И-НЕ, а на прямом выходе триггера 23 устанавливается сигнал - начало временного интервала, который разрешает поступление М-го и последующих синхросигналов через сигнатур, по заднему фронту которого осуществляется формирование сигнатуры сигнала, поступающего с выхода элемента 14 И,

На первом такте измерительного интервала происходит сравнение последовательности двоичных векторов, записанной в группу 11 регистров, с эталонной, записанной в регистре 5,

Если анализируемая последовательность векторов совпадает по соответствующим разрядам с эталонной,; то на соответствующих выходах группы 12 элементов ИСКЛЮЧАЩЕЕ ИЛИ устанавливается значение О, в противном случае, для несовпадающих i-x разрядов - значение 1, Эталон маски позволяет выделить из всей последовательности интерес уемые разряды двоичных век-

торов - соответствующие разряды эталонной маски имеют значение 1, При

мента 14 И по заднему фронту синхросигнала, поступающего с выхода элемента 4 И; во всех остальных случаях - О,

Вьш1еописанный процесс повторяется до поступления на управляюшдй вход 1 анализатора внешнего сигнала Стоп, что соответствует концу измерительного окна и измерительного интервала.

Если на последующих тактах измерительного интервала анализируемая последовательность векторов совпадает с эталоном и с маской, то в фор- мирователь 5 сигнатур записывается очередная 1, в противном случае - О, При этом на блоке 6 индикации можно наблюдать значение соответствующей сигнатуры.

5J3

Таким образом, использование пред латаемого устройства позволяет диф ференцировать ошибки формирования последовательностей многоразрядных векторов, что существенно расширяет функ1щональные возможности анализатора.

Формула изобретения

Сигнатурный анализатор, содержа формирователь сигнатур, формирователь временных сигналов, блок индикации и первый элемент И, причем управляющий вход окна измерения ана- лизатора соединен с входом формирователя временных сигналов, выход ко торого соединен с первым входом пер- вого элемента И, второй вход которого является синхровходом анализатора выход первого элемента И подключен к синхровходу формирователя сигнатур группа выходов которого соединена с группой информационных входов блока индикации, отлича-ющийся тем, что, с целью расширения функциональных возможностей за счет обеспечения дифференищрованного контроля последовательностей многоразрядных векторов, анализатор содержит допол- нительно формирователь временных интервалов, группу из К Ьразрядных регистров сдвига, где К - разрядност анализируемых векторов, а М - их максимальное количество, группу из КхМ элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу из КхМ элементов И-НЕ, второй элемент И и два буферных регистра разрядностью КхМ, причем вход разрешения работы формирователя временных интервалов соединен с выходом формирователя временных сигналов, синхровход формирователя временных интервалов со

5 0 0 5 0

5

166

единен с синхровходами регистров сдвига группы и с синхровходом анализатора, вход стробирования параллельной записи формирователя временных интервалов является входом управления записью числа анализируемых векторов, группа информационных входов параллельной записи формирователя временных интервашов является группой входов задания числа анализируемых векторов анализатора, выход формирователя временных интервалов соединен с третьим входом первого элемента И, информационные входы последовательной записи регистроЁ сдвига группы образуют группу информационных входов, анализатора, разрядные выходы регистров сдвига группы соединены с первыми входами соответствую- шлх элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первыми входами соответст- вукицих элементов И-НЕ группы, выходы первого и второго буферных регистров соединены соответственно с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы и элементов И-НЕ группы, выходы последних соединены с входами второго элемента И, выход которого соединен с информационным входом формирователя сигнатур, входы стробирования параллельной записи первого и второго буферных регистров являются соответственно входом управления записью эталонной последовательности и входом управления записью маски анализатора, группы информационных входов первого и второго буферных регистров являются соответственно группой информационньк входов эталонной последовательности и группой информационных входов маски анализатора.

itse 1к0и

ОтЗ От I

21

t

От 10

ОтЗ

У Я

2// Л2

5 US

22

ЙП

Л

i-c

23 Rl Г

фиг. 2

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

| Патент США № 3976864, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

Авторы

Даты

1988-01-15—Публикация

1985-11-20—Подача