(21)4138684/24-24

(22)22.10.86

(46) 30.04.88. Бюл. № 16

(72) Л. Ю. Николаев и Л. Е. Алехин

(53)681.325(088.8)

(56)Авторское свидетельство СССР № 760075, кл. G 06 F 13/10, 1978.

Авторское свидетельство СССР № 826332, кл. G 06 F 13/20, 1979.

(54)УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ТЕЛЕГРАФНЫМИ КАНАЛАМИ СВЯЗИ

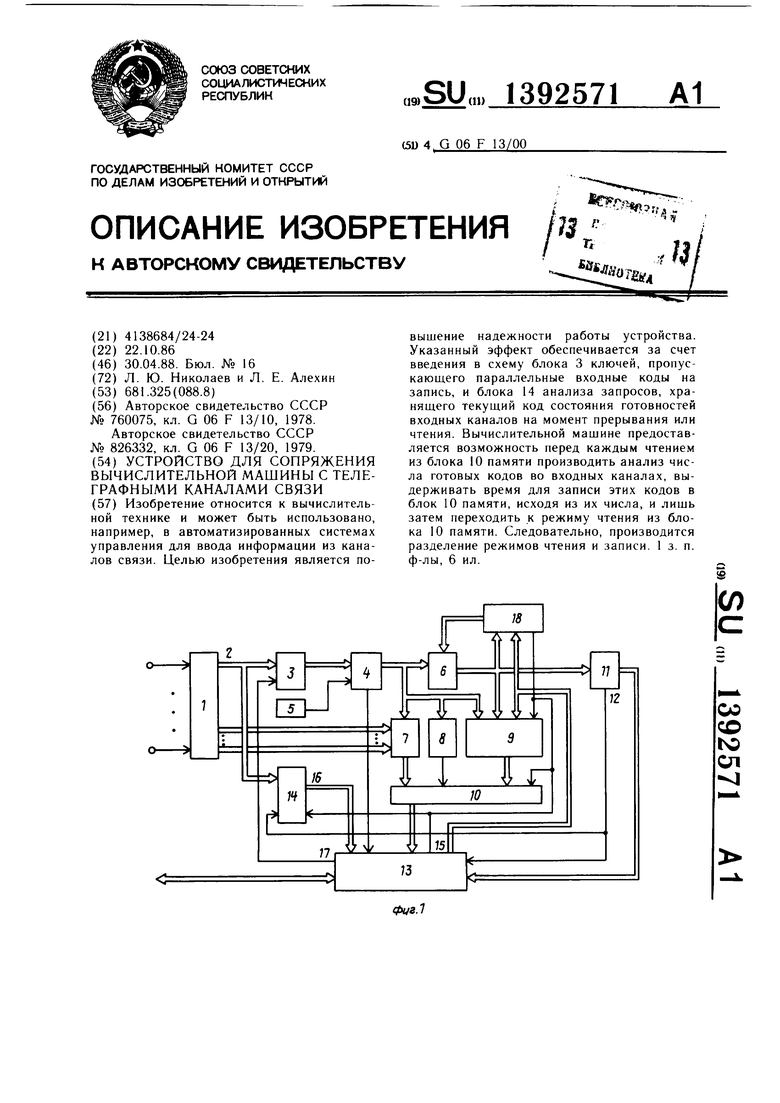

(57)Изобретение относится к вычислительной технике и может быть использовано, например, в автоматизированных системах управления для ввода информации из каналов связи. Целью изобретения является повышение надежности работы устройства. Указанный эффект обеспечивается за счет введения в схему блока 3 ключей, пропускающего параллельные входные коды на запись, и блока 14 анализа запросов, хранящего текущий код состояния готовностей входных каналов на момент прерывания или чтения. Вычислительной мащине предоставляется возможность перед каждым чтением из блока 10 памяти производить анализ числа готовых кодов во входных каналах, выдерживать время для записи этих кодов в блок 10 памяти, исходя из их числа, и лищь затем переходить к режиму чтения из блока 10 памяти. Следовательно, производится разделение режимов чтения и записи. 1 з. п. ф-лы, 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Устройство для сопряжения ЭВМ с периферийной системой | 1989 |

|

SU1635188A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения двух цифровых вычислительных машин | 1979 |

|

SU868741A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С ТЕЛЕГРАФНЫМИ КАНАЛАМИ СВЯЗИ | 1979 |

|

SU826332A1 |

| Устройство для сопряжения процессора с периферийным устройством | 1984 |

|

SU1246102A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Устройство для сопряжения внешних устройств с электронной вычислительной машиной | 1983 |

|

SU1100615A1 |

(Л

о:) со

ГчЭ 01

Изобретение относится к вычислитель)1ой технике и может быть использовано, например, в автоматизированных системах управления для ввода информации из каналов связи при наложении режимов записи и счи- тывания.

Целью изобретения является повышение надежности работы устройства. При этом ЭВМ предоставляется возможность перед каждым чтением из блока памяти производить анализ состояния входных каналов, выдерживать время для записи информации в устройство, а затем переходить к режиму чтения из устройства в ЭВМ, следовательно, производится разделение режимов чтения и записи. Тем самым достигается увеличение надежности работы устройства.

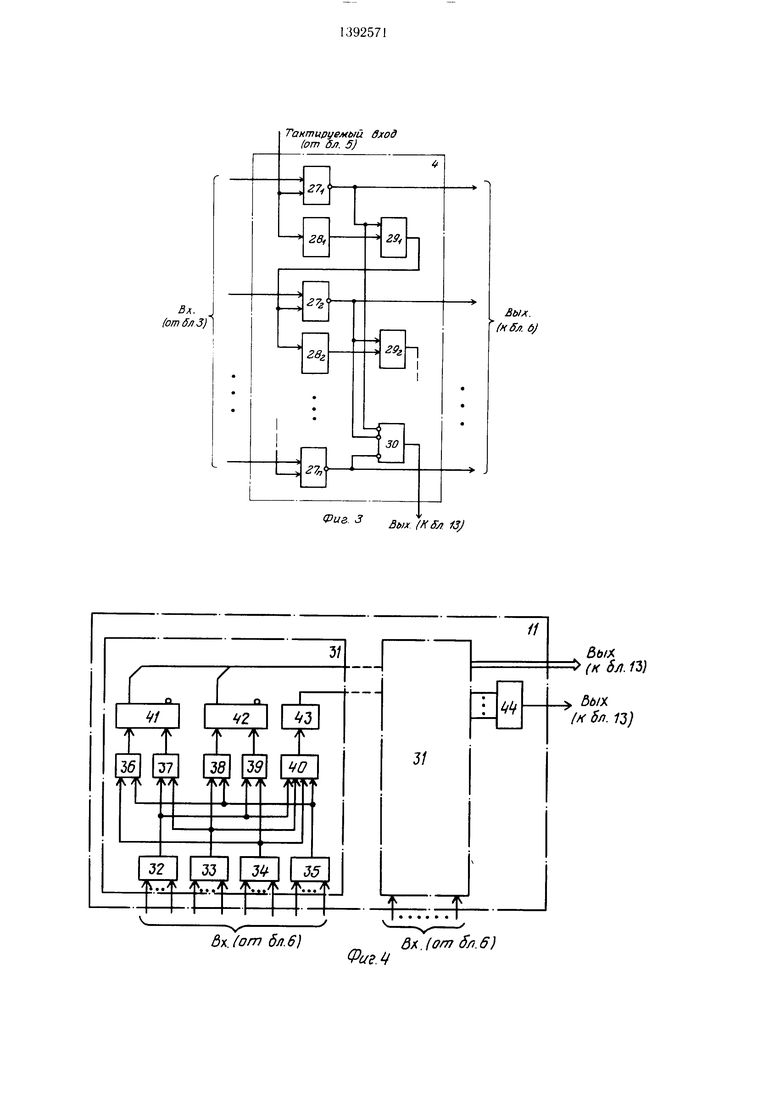

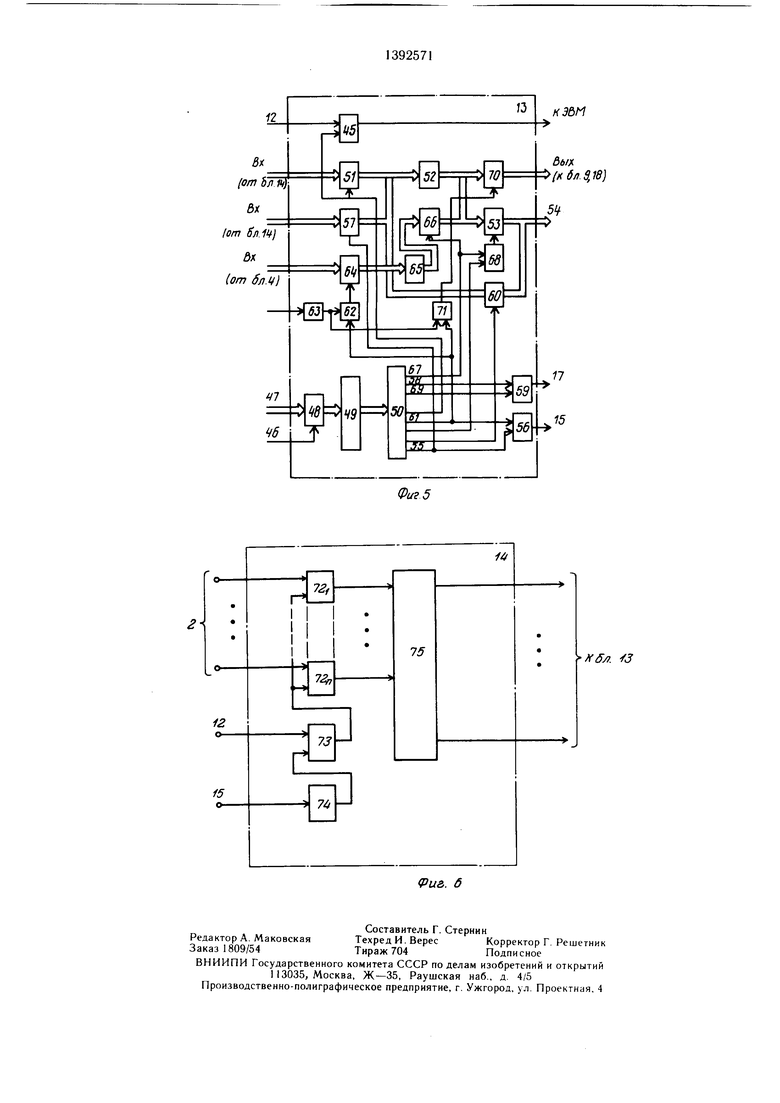

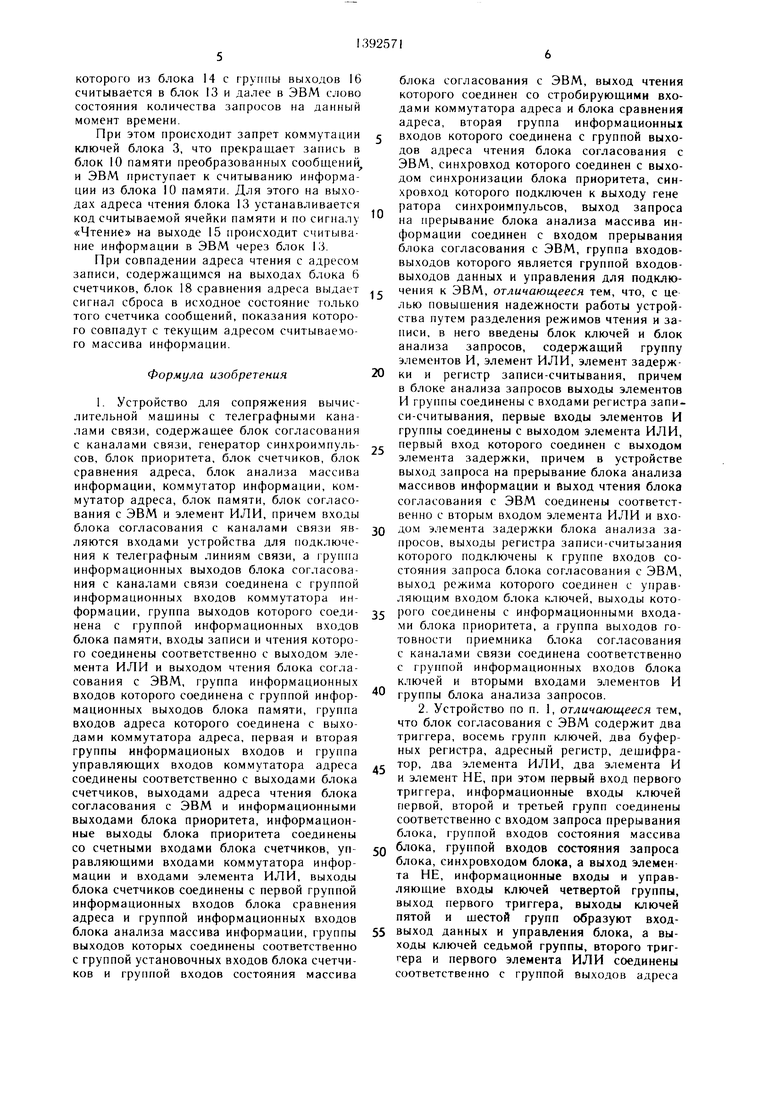

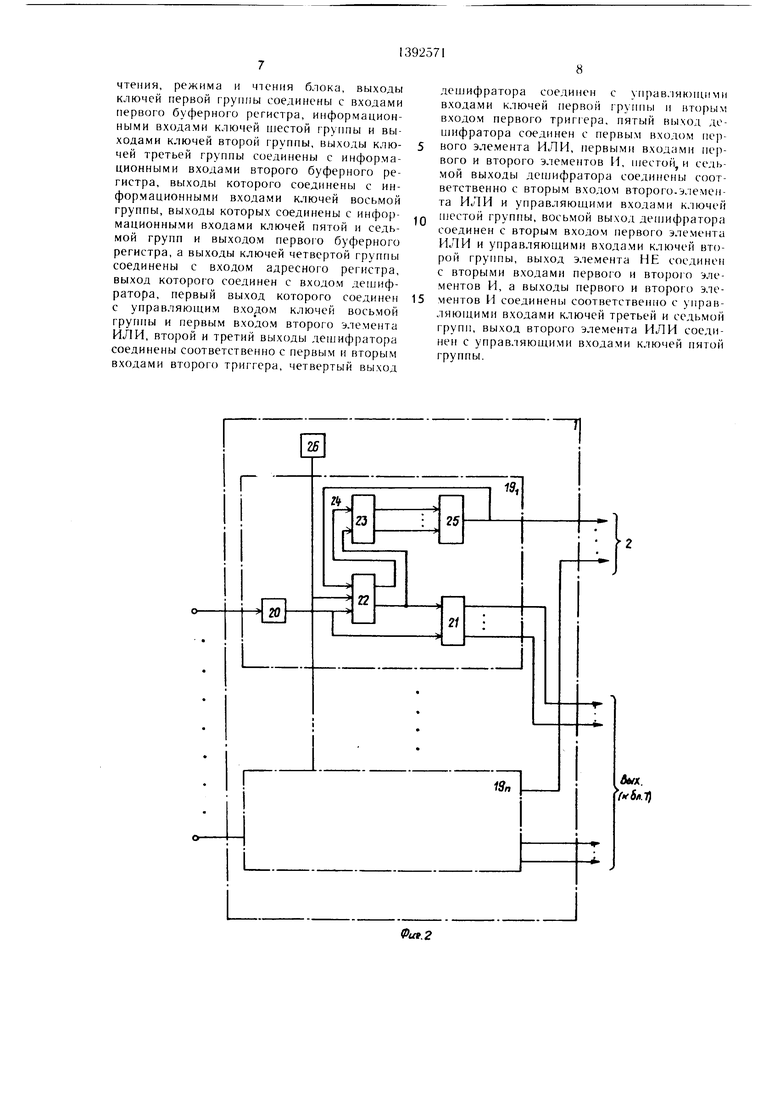

На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 - блок согласования с каналами связи; на фиг. 3 - блок приоритета; на фиг. 4 - блок анализа массива информации; на фиг. 5 - блок согласо- вания с ЭВМ; на фиг. 6 - блок анализа запросов.

Устройство (фиг. 1) включает блок 1 согласования с каналами связи, группу 2 выходов сигналов «Готовность приемника, блок 3 ключей, блок 4 приоритета, генератор 5 синхроимпульсов, блок 6 счетчиков, коммутатор 7 информации, элемент ИЛИ 8, коммутатор 9 адреса, блок 10 памяти, блок 11 анализа массива информации, выход 12 запросов прерывания, блок 13 согласования с ЭВМ, блок 14 анализа запросов, выход 15 чтения, группу 16 выходов состояния запросов, выход 17 режима, блок 18 сравнения адреса.

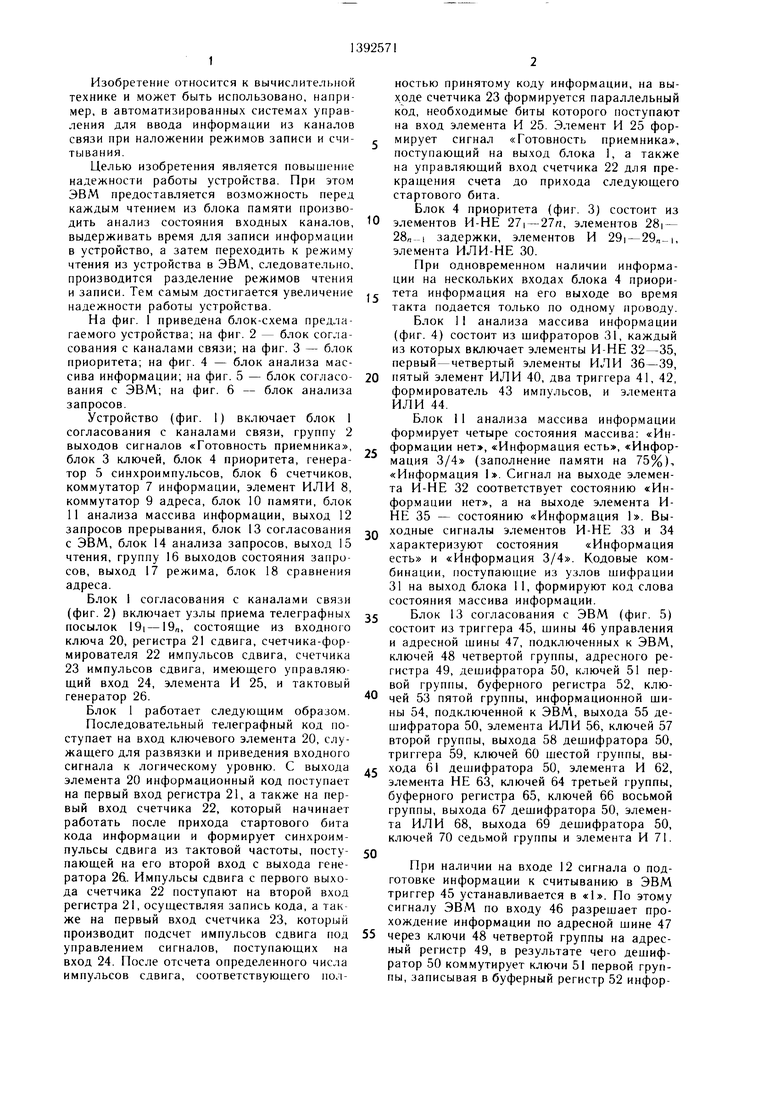

Блок 1 согласования с каналами связи (фиг. 2) включает узлы приема телеграфных посылок 19| -19„, состоящие из входного ключа 20, регистра 21 сдвига, счетчика-формирователя 22 импульсов сдвига, счетчика 23 импульсов сдвига, имеющего управляющий вход 24, элемента И 25, и тактовый генератор 26.

Блок 1 работает следующим образом.

Последовательный телеграфный код поступает на вход ключевого элемента 20, служащего для развязки и приведения входного сигнала к логическому уровню. С выхода элемента 20 информационный код поступает на первый вход регистра 21, а также на первый вход счетчика 22, который начинает работать после прихода стартового бита кода информации и формирует синхроимпульсы сдвига из тактовой частоты, посту- лающей на его второй вход с выхода генератора 26. Импульсы сдвига с первого выхода счетчика 22 поступают на второй вход регистра 21, осуществляя запись кода, а также на первый вход счетчика 23, который производит подсчет импульсов сдвига под управлением сигналов, поступающих на вход 24. После отсчета определенного числа импульсов сдвига, соответствующего пол5

,

0

Q

с 0

с о 5

ностью принятому коду информации, на вы- х.оде счетчика 23 формируется параллельный код, необходимые биты которого поступают на вход элемента И 25. Элемент И 25 формирует сигнал «Готовность приемника, поступающий на выход блока 1, а также на управляющий вход счетчика 22 для прекращения счета до прихода следующего стартового бита.

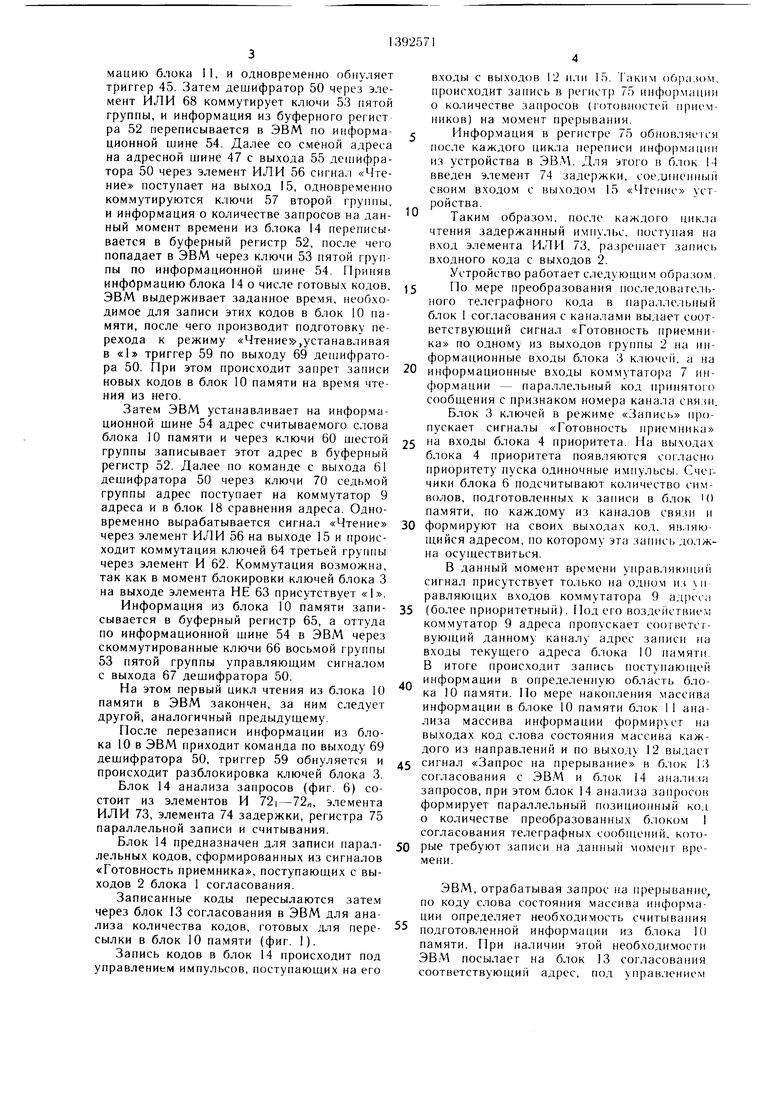

Блок 4 приоритета (фиг. 3) состоит из элементов И-НЕ 27: - 27п, элементов 28| - 28„-1 задержки, элементов И 29i-29 -1, элемента ИЛИ-НЕ 30.

При одновременном наличии информации на нескольких входах блока 4 приоритета информация на его выходе во время такта подается только по одному проводу. Блок 11 анализа массива информации (фиг. 4) состоит из шифраторов 31, каждый из которых включает элементы И-НЕ 32-35, первый - четвертый элементы ИЛИ 36-39, пятый элемент ИЛИ 40, два триггера 41, 42, формирователь 43 импульсов, и элемента ИЛИ 44.

Блок 11 анализа массива информации формирует четыре состояния массива: «Информации нет, «Информация есть, «Информация 3/4 (заполнение памяти на 75%), «Информация 1. Сигнал на выходе элемента И-НЕ 32 соответствует состоянию «Информации нет, а на выходе элемента И- НЕ 35 - состоянию «Информация 1. Выходные сигналы элементов И-НЕ 33 и 34 характеризуют состояния «Информация есть и «Информация 3/4. Кодовые комбинации, поступающие из узлов шифрации 31 на выход блока 11, формируют код слова состояния массива информации.

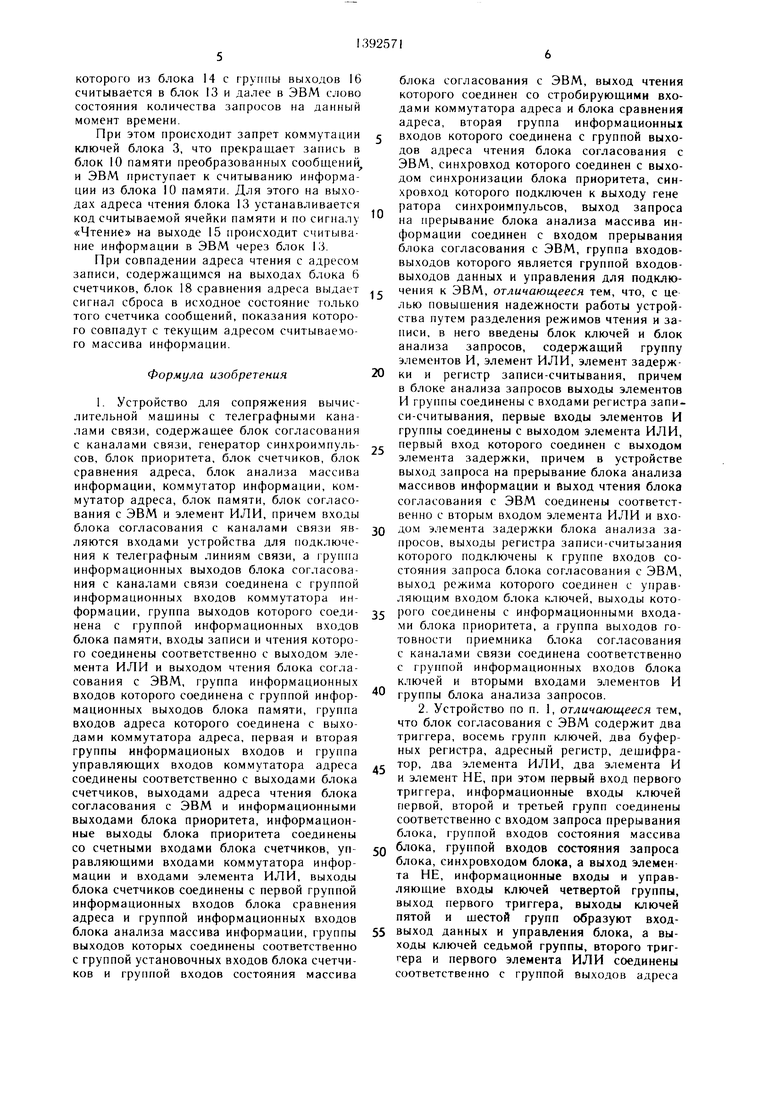

Блок 13 согласования с ЭВМ (фиг. 5) состоит из триггера 45, щины 46 управления и адресной щины 47, подключенных к ЭВМ, ключей 48 четвертой группы, адресного регистра 49, дешифратора 50, ключей 51 первой группы, буферного регистра 52, ключей 53 пятой группы, информационной щины 54, подключенной к ЭВМ, выхода 55 де- щифратора 50, элемента ИЛИ 56, ключей 57 второй группы, выхода 58 дещифратора 50, триггера 59, ключей 60 щестой группы, выхода 61 дещифратора 50, элемента И 62, элемента НЕ 63, ключей 64 третьей группы, буферного регистра 65, ключей 66 восьмой группы, выхода 67 дешифратора 50, элемента ИЛИ 68, выхода 69 дешифратора 50, ключей 70 седьмой группы и элемента И 71.

При наличии на входе 12 сигнала о подготовке информации к считыванию в ЭВМ триггер 45 устанавливается в «1. По этому сигналу ЭВМ по входу 46 разрешает прохождение информации по адресной шине 47 через ключи 48 четвертой группы на адресный регистр 49, в результате чего дешифратор 50 коммутирует ключи 51 первой группы, записывая в буферный регистр 52 информацию блока 11, и одновременно обнуляет триггер 45. Затем дешифратор 50 через элемент ИЛИ 68 коммутирует ключи 53 пятой группы, и информация из буферного регист ра 52 переписывается в ЭВМ по информационной шине 54. Далее со сменой адреса на адресной шине 47 с выхода 55 дешифратора 50 через элемент ИЛИ 56 сигнал «Чтение поступает на выход 15, одновременно коммутируются ключи 57 второй группы, и информация о количестве запросов на данный момент времени из блока 14 переписывается в буферный регистр 52, после чего попадает в ЭВМ через ключи 53 пятой группы по информационной шине 54. Приняв информацию блока 14 о числе готовых кодов, ЭВМ выдерживает заданное время, необходимое для записи этих кодов в блок 10 памяти, после чего производит подготовку перехода к режиму «Чтение,устанавливая в «1 триггер 59 по выходу 69 дешифратора 50. При этом происходит запрет записи новых кодов в блок 10 памяти на время чтения из него.

Затем ЭВМ устанавливает на инфор.ма- ционной шине 54 адрес считываемого слова блока 10 памяти и через ключи 60 шестой группы записывает этот адрес в буферный регистр 52. Далее по команде с выхода 61 дешифратора 50 через ключи 70 седьмой группы адрес поступает на коммутатор 9 адреса и в блок 18 сравнения адреса. Одновременно вырабатывается сигнал «Чтение через элемент ИЛИ 56 на выходе 15 и происходит коммутация ключей 64 третьей гругшы через элемент И 62. Коммутация возможна, так как в момент блокировки ключей блока 3 на выходе элемента НЕ 63 присутствует «1. Информация из блока 10 памяти записывается в буферный регистр 65, а оттуда по информационной шине 54 в ЭВМ через скоммутированные ключи 66 восьмой группы 53 пятой группы управляюш.им сигналом с выхода 67 дешифратора 50.

На этом первый цикл чтения из блока 10 памяти в ЭВМ закончен, за ним следует другой, аналогичный предыдущему.

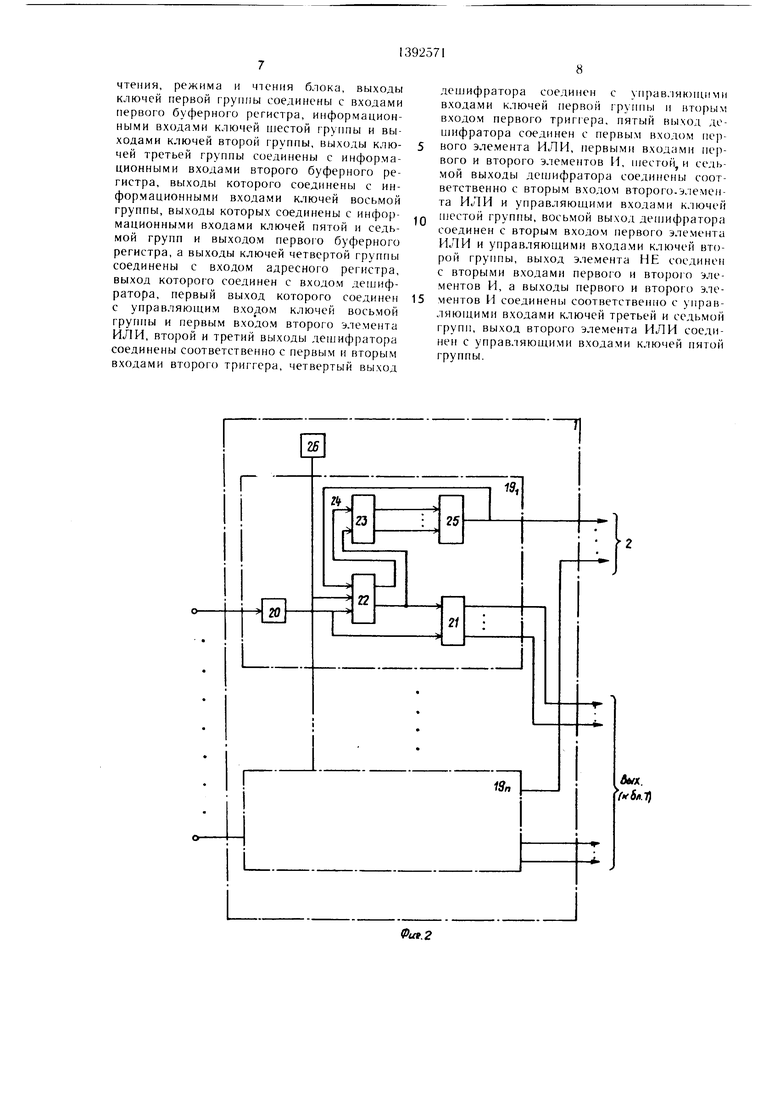

После перезаписи информации из блока 10 в ЭВМ приходит команда по выходу 69 дешифратора 50, триггер 59 обнуляется и происходит разблокировка ключей блока 3. Блок 14 анализа запросов (фиг. 6) состоит из элементов И 72|-72л, элемента ИЛИ 73, элемента 74 задержки, регистра 75 параллельной записи и считывания.

Блок 14 предназначен для записи параллельных кодов, сформированных из сигналов «Готовность приемника, поступающих с выходов 2 блока 1 согласования.

Записанные коды пересылаются зате.м через блок 13 согласования в ЭВМ для анализа количества кодов, готовых для пересылки в блок 10 памяти (фиг. 1).

Запись кодов в блок 14 происходит под управлением импульсов, поступающих на его

входы с выходов 12 или 15. Таким образом, происходит запись в регистр 75 информации о количестве запросов (г отонностей приемников) на .момент прерывания. 2Информация в регистре 75 обновляется

после каждого цикла переписи информации из устройства в ЭВМ. Для этого в блок 14 введен элемент 74 задержки, сое.и1ненный своим входом с выходом 15 «Чтение уст- ройства.

Таким образом, после каждого цикла чтения задержанный импульс, поступая на вход элемента ИЛИ 73, разрешает запись входного кода с выходов 2.

Устройство работает следующим образом. 5 По мере преобразования последовательного телеграфного кода в параллельный блок 1 согласования с каналами выдает соответствующий сигнал «Готовность приемника по одному из выходов группы 2 на информационные входы блока 3 ключей, а на 0 информационные входы коммутатора 7 информации - параллельный код принятого сообщения с признаком номера канала связи. Блок 3 ключей в режиме «Запись пропускает сигналы «Готовность приемника 5 на входы блока 4 приоритета. На выходах блока 4 приоритета появляются согласно приоритету пуска одиночные импульсы. Счег- чики блока 6 подсчитывают количество символов, подготовленных к записи в блок М) памяти, по каждому из каналов связи и 0 формируют на своих выходах код, яв.яю щийся адресом, по которому эта запись должна осуществиться.

В данный момент времени управляющий сигнал присутствует только на одном из п равляющих входов коммутатора 9 адрес;) 5 (более приоритетный). Под его воздействием коммутатор 9 адреса пропускает соответствующий данному каналу адрес записи па входы текущего адреса блока 10 памяти. В итоге происходит запись поступающей - информации в определенную область блока 10 памяти. По мере накопления массива информации в блоке 10 памяти блок I 1 анализа массива информации формирует на выходах код слова состояния массива каждого из направлений и по выходу 12 выдает 5 сигнал «Запрос на прерывание в б, 1ок 13 согласования с ЭВМ и блок 14 анализа запросов, при этом блок 14 анализа запросов формирует параллельный позиционный код о количестве преобразованных блоком 1 согласования телеграфных сообщений, кото- 0 рые требуют записи на данный момент времени.

ЭВМ, отрабатывая запрос на прерывание, по коду слова состояния массива информации определяет необходимость считывания подготовленной информации из блока 1(1 памяти. При наличии этой необходимости ЭВМ посылает на блок 13 согласования соответствующий адрес, под управ, 1ением

которого из блока 14 с группы выходов 16 считывается в блок 13 и далее в ЭВМ слово состояния количества запросов на данный момент времени.

При этом происходит запрет коммутации ключей блока 3, что прекращает запись в блок 10 памяти преобразованных сообщений и ЭВМ приступает к считыванию информации из блока 10 памяти. Для этого на выходах адреса чтения блока 13 устанавливается код считываемой ячейки памяти и по сигналу «Чтение на выходе 15 происходит считывание информации в ЭВМ через блок 13.

При совпадении адреса чтения с адресом записи, содержащимся на выходах блока 6 счетчиков, блок 18 сравнения адреса выдает сигнал сброса в исходное состояние только того счетчика сообщений, показания которого совпадут с текущим адресом считываемого массива информации.

Формула изобретения

0

0

0 5 д 50 55

блока согласования с ЭВМ, выход чтения которого соединен со стробирующими входами коммутатора адреса и блока сравнения адреса, вторая группа информационных входов которого соединена с группой выходов адреса чтения блока согласования с ЭВМ, синхровход которого соединен с выходом синхронизации блока приоритета, синхровход которого подключен к выходу гене ратора синхроимпульсов, выход запроса на прерывание блока анализа массива информации соединен с входом прерывания блока согласования с ЭВМ, группа входов- выходов которого является группой входов- выходов данных и управления для подключения к ЭВМ, отличающееся тем, что, с це лью повыщения надежности работы устройства путем разделения режимов чтения и записи, в него введены блок ключей и блок анализа запросов, содержащий группу элементов И, элемент ИЛИ, элемент задержки и регистр записи-считывания, причем в блоке анализа запросов выходы элементов И группы соединены с входами регистра записи-считывания, первые входы элементов И группы соединены с выходом элемента ИЛИ, первый вход которого соединен с выходом элемента задержки, причем в устройстве выход запроса на прерывание блока анализа массивов информации и выход чтения блока согласования с ЭВМ соединены соответственно с вторым входом элемента ИЛИ и входом элемента задержки блока анализа запросов, выходы регистра записи-считывания которого подключены к группе входов состояния запроса блока согласования с ЭВМ, выход режима которого соединен с управляющим входом блока ключей, выходы которого соединены с информационными входами блока приоритета, а группа выходов готовности приемника блока согласования с каналами связи соединена соответственно с группой информационных входов блока ключей и вторыми входами элементов И группы блока анализа запросов.

чте}1ия, режима и чтения блока, выходы ключей первой группы соединены с входами первого буферного регистра, ипформацион- ными входами ключей шестой группы и выходами ключей второй группы, выходы ключей третьей группы соединены с информационными входами второго буферного регистра, выходы которого соединены с нн- формационными входами ключей восьмой группы, выходы которых соединены с информационными входами ключей пятой и седьмой групп и выходом первого буферного регистра, а выходы ключей четвертой группы соединены с входом адресного регистра, выход которого соединен с входом дешифратора, первый выход которого соединен с управляющим входом ключей восьмой гругигы и первым входом второго элемента ИЛИ, второй и третий выходы дешифратора соединены соответственно с первым и вторым входами второго триггера, четвертый выход

2Б

Г

0

де1иифратора соединен с управляюпщми входами ключей первой гругшы и вторым входом первого , пятый выход дешифратора соединен с первым входом первого элемента ИЛИ, первыми входами первого и второго элементов И, цестой и седьмой выходы дешифратора соединены соответственно с вторым входом второго.элемента ИЛИ и управляюшими входами ключей п естой группы, восьмой выход дешифратора соединен с вторым входом первого элемента ИЛИ и управляющими входами ключей второй группы, выход элемента НЕ соединен с вторыми входами первого и второго элементов И, а выходы первого и второго элементов И соединены соответственно с управляющими входами ключей третьей и седьмой групп, выход второго элемента ИЛИ соединен с управляющими входами ключей пятой группы.

fsH

Г

Z3

25

..J

Зп

6tfX. )

Дл. 1от6лЗ)

ди..{от бл.6)

Выл. (н5л 6)

Вы/. (К 8л. 1Ъ)

/А- бл. 13)

ФидМ

3x.(0f7 бл.6}

12

12

о-

73

15

Редактор А. Маковская Заказ 1809/54

Составитель Г. Стерннн

Техред И. ВересКорректор Г. Решетник

Тираж 704Подписное

ВНИИПИ Государственного комитета СССР поделай изобретеннй и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 КЭ5П

5ь/и (кбл.18}

75

/(5л /J

Риа. 6

Авторы

Даты

1988-04-30—Публикация

1986-10-22—Подача