I

Изобретение относится к вычислительной технике и может быть применено а автоматических системах управления движуиХихся объектов, а также может быть использовано для построения электронных устройств различного назначения (усилительных устройств со специальными видами передаточных функций, генераторов,, функциональных преобразователей, аналоговых запоминающих устройств, стабилизаторов, различных схем компенсации и др.). в частности для построения ИЗОДрОМНЫХ устройств

с неограниченным временем хранения результата интегрирования, широко применяемых в системах управления движущихся объектов.

Известен больщой ряд интегрирующих устройств с ограниченным вре.менем хранения результата интегрирования, основным элементом в которых является операционный усилитель с интегрирующим конденсатором в цепи отрицательной обратной связи и коммутирующее устройство, подключаемое своим выходом ко входу интегратора 1)

Предельное значение про.межутка времени, в течение которого интегратор необратимо теряет И9ходпое напряжение результата интегрирования в заданных пределах, определяется величиной дрейфа тока смещения применяемого класса операционного усилителя и значением сопротивления утечки применяемого типа конденсатора.

Это время весьма ограничено и не превышает, в случае применения специальных мер стабилизации, значения 3-4 , что является недостаточным для решения целого ряда технических задач и приводит к необходимости использования механических устройств больщих габаритов, веса и низкой надежности.

Наиболее близким по технической сущности к предлагаемому является аналоговое запоминающее устройство, которое содержит операционный усилитель с интегрирующим конденсатором в цепи отрицательной обратной связи, коммутирующее устройство, выход которого подключен непосредственно ко входу операционного усилителя, на который через один вход ком.мутирующего устройства и его нормально-замкнутые контакты поступает входной сигнал, выход операционного усилителя соединяется со входом преобразователя напряжения в периодическую знакопеременную функцию, выход

которого подключается к другому входу коммутирующего устройства 2.

В замкнутый контур интегратора введен преобразователь напряжения в периоди-ческую знакопеременную функцию. При этом значение напряжения Ueu. , соответствующее компенсирующему узлу функции Un f {Ugt« ), в устройстве не сохраняется независимо от времени, а продолжает изменяться в установившемся направлении благодаря действию в замкнутом контуре цепи задержки, являющейся причиной накопления статической ощибки рассогласования при этом скорость движения Uj, уменьшается, но не равна нулю.

Полная компенсация может быть только при наличии формирования устройством в замкнутом контуре интегратора зон «захвата (гистерезиса) вокруг соответствующих узловых точек с периодическим из.менением знака управляющего сигнала.

Рекомендуемое в схеме устройства непосредственное подключение выхода преобразователя ко входу операционного усилителя создает реальные предпосылки для возникновения генерации в интеграторе и потере устойчивости устройства в цело.м.

Основным недостатком известного устройства является ограниченное время хранения результата интегрирования при сложных технических предпосылках к реализации преобразователя напряжения в периодическую знакопеременную функцию.

ЦелЬ изобретения - увеличение времени хранения устройства.

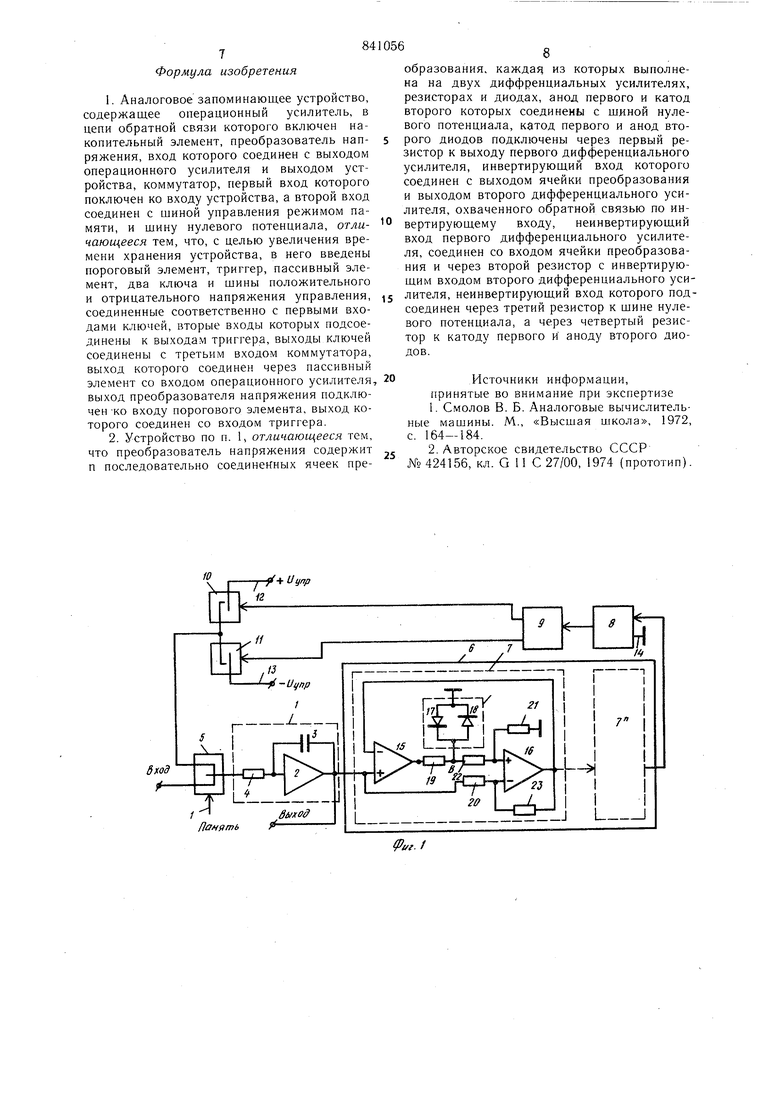

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее операционный усилитель, в цепи обратной связи которого включен накопительный элемент, преобразователь напряжения, вход которого соединен с выходом one рационного усилителя и выходом устройства, коммутатор, первый вход которого подключен ко входу устройства, а второй вход соединен с шиной управления режимом памяти, и шину нулевого потенциала, введены пороговый элемент, триггер, пассивный элемент, два ключа и шины положительного и отрицательного напряжения управления, соединенные соответственно с первыми входами ключей, вторые входы которых подсоединены к выходам триггера выходы ключей соединены с третьим входом коммутатора, выход соединен через пассивный элемент со входом операционного усилителя, выход преобразователя напряжения подключенко входу порогового элемента, выход которого соединен со входом триггера.

Кроме того, преобразователь напряжения содержит п последовательно соединенных ячеек.преобразования, каждая из которых выполнена на двух диффренциальных усилителях, резисторах и диодах, анод первого и катод второго которых соединены с шиной нулевого потенциала, катод первого и анод второго диодов подключены через первый

резистор к выходу первого дифференциально го усилителя, инвертирующий вход которого соединен с выходом ячейки преобразования и выходом второго дифференциального усилителя, охваченного обратной связью по инвертирующему входу, неинвертирующий вход первого дифференциальногоусилителя соединен со входом ячейки преобразования и через второй резистор с инвертирующим входом второго дифференциального усилителя, неинвертирующий вход которого подсоединен через третий резистор к шине нулевого потенциала, а через четвертый резистор к катоду первого и аноду второго диодов.

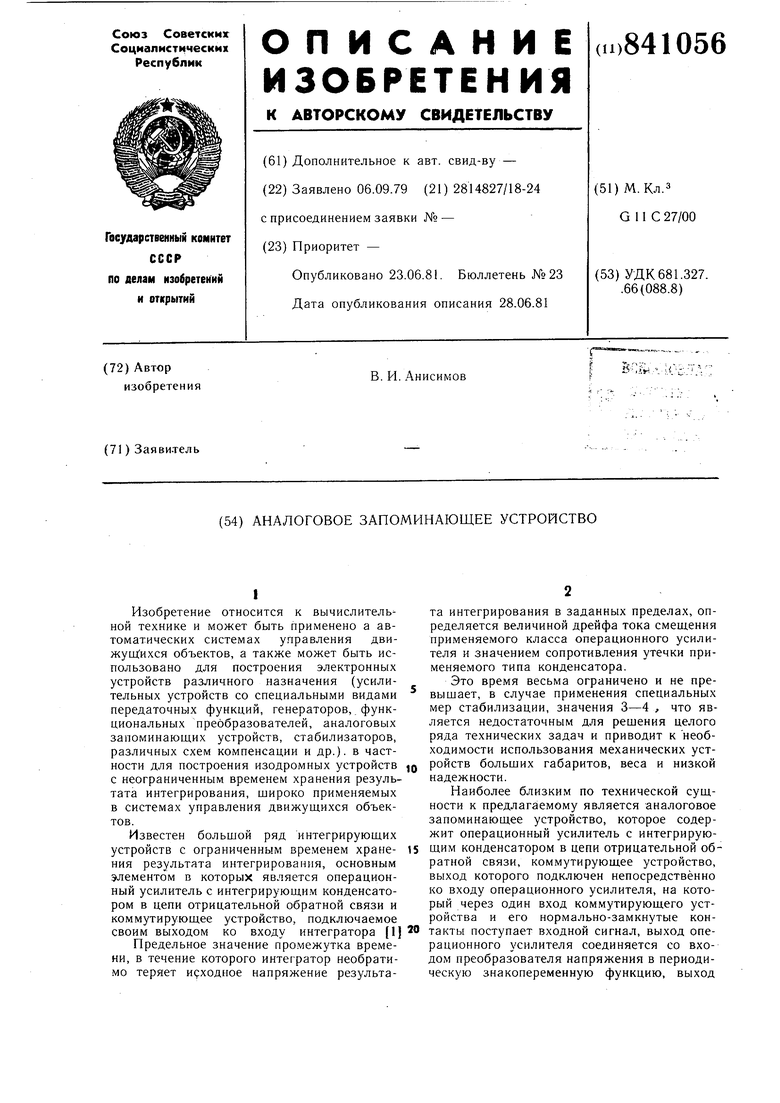

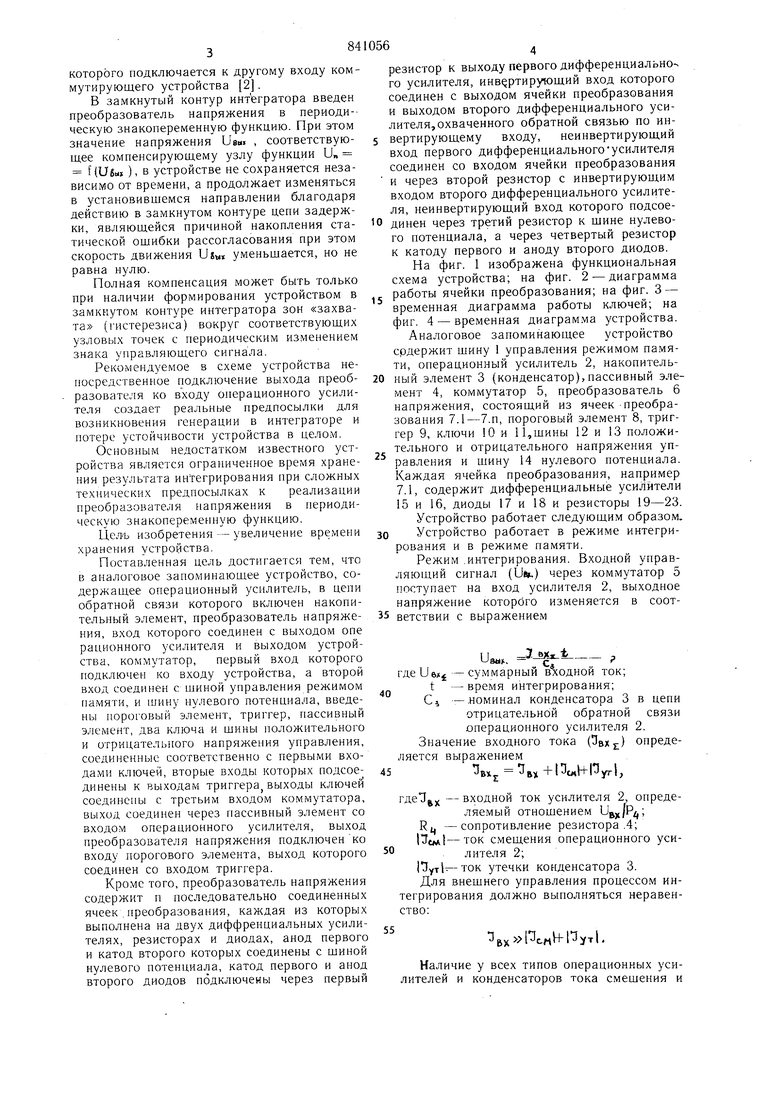

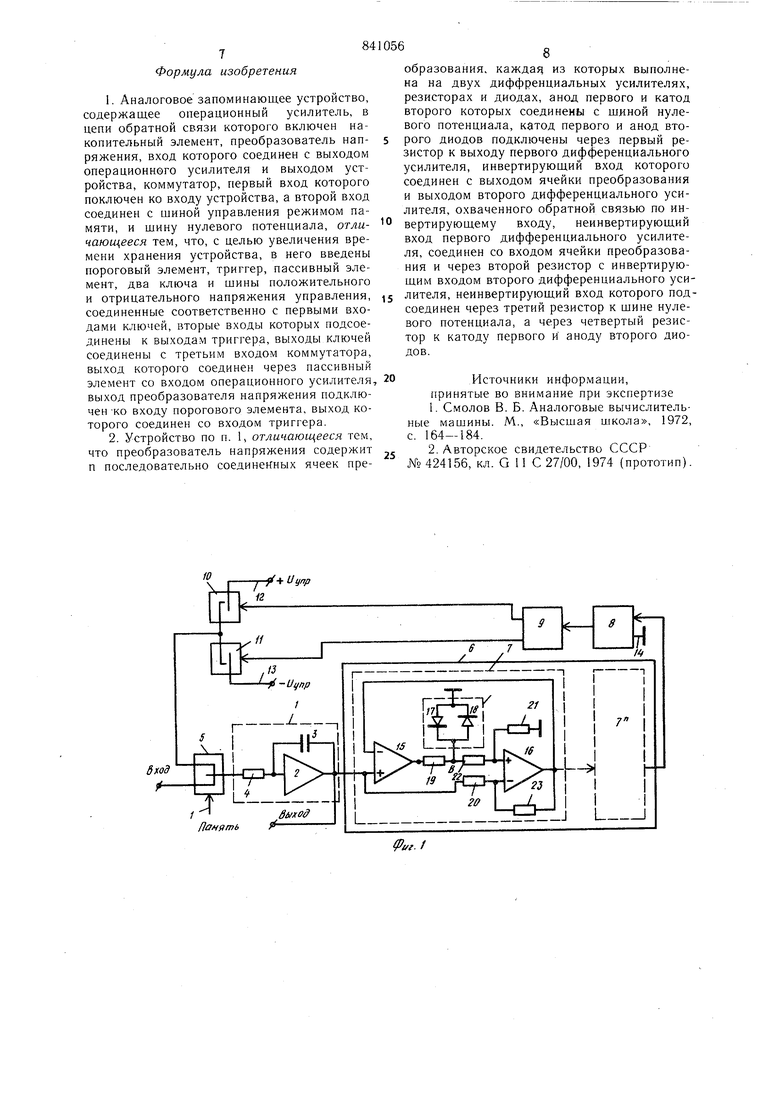

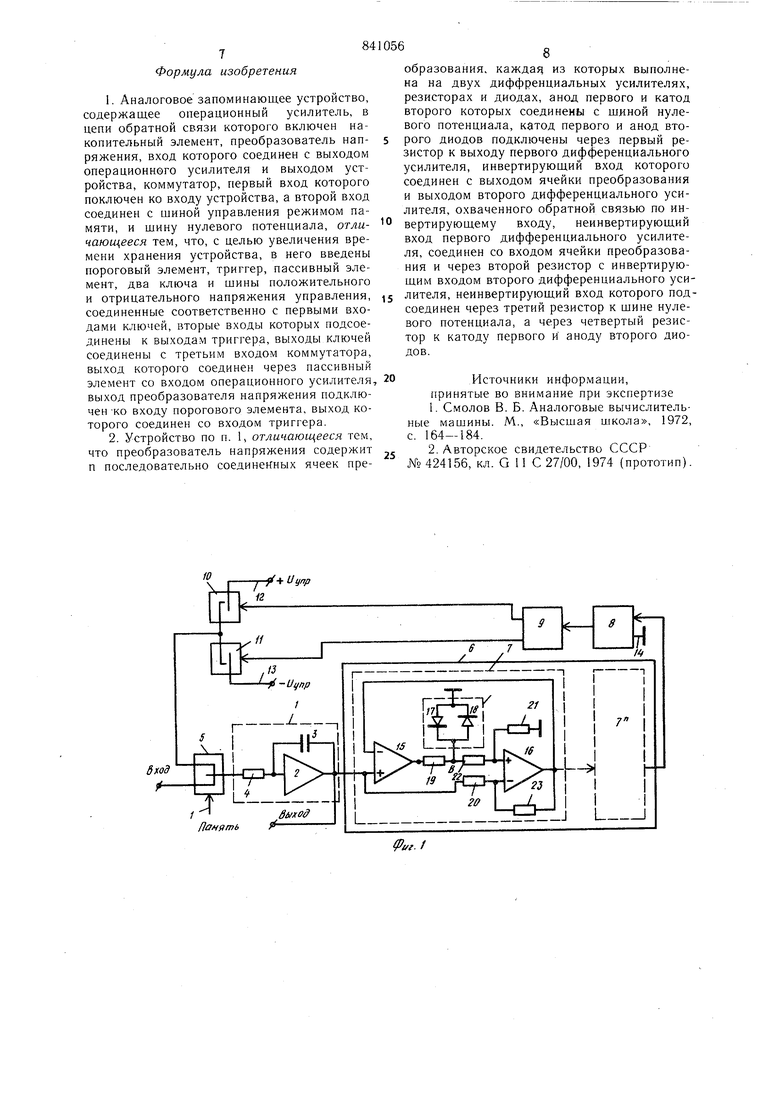

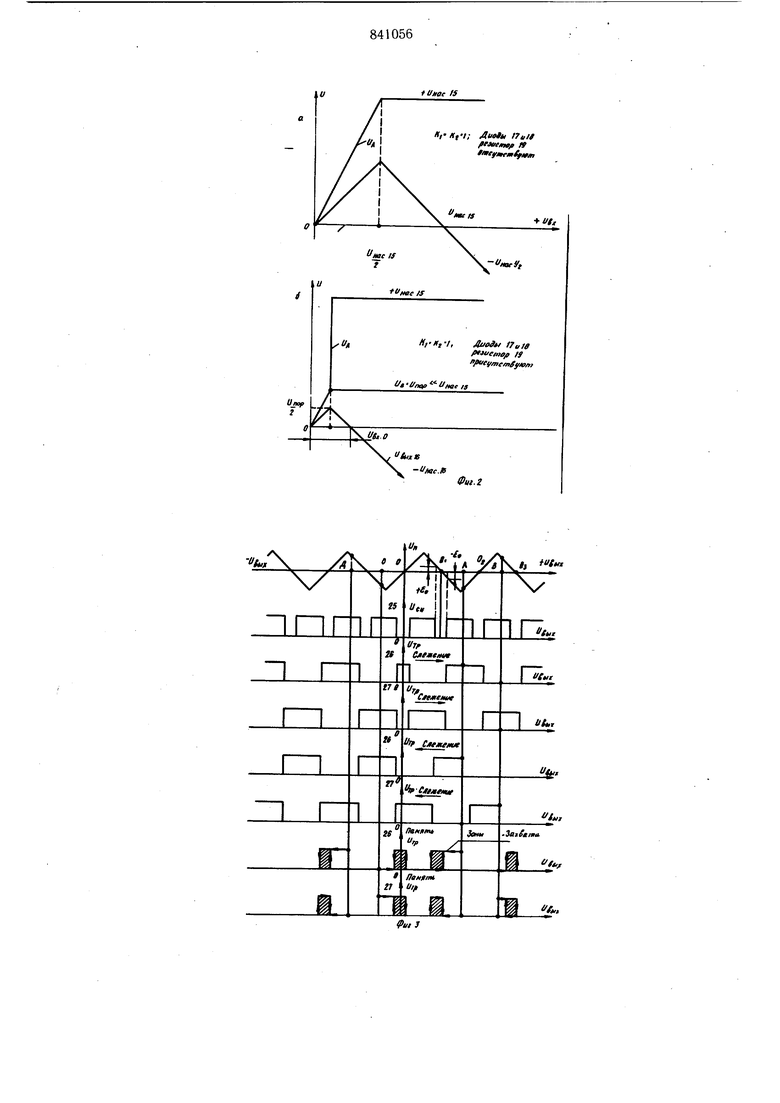

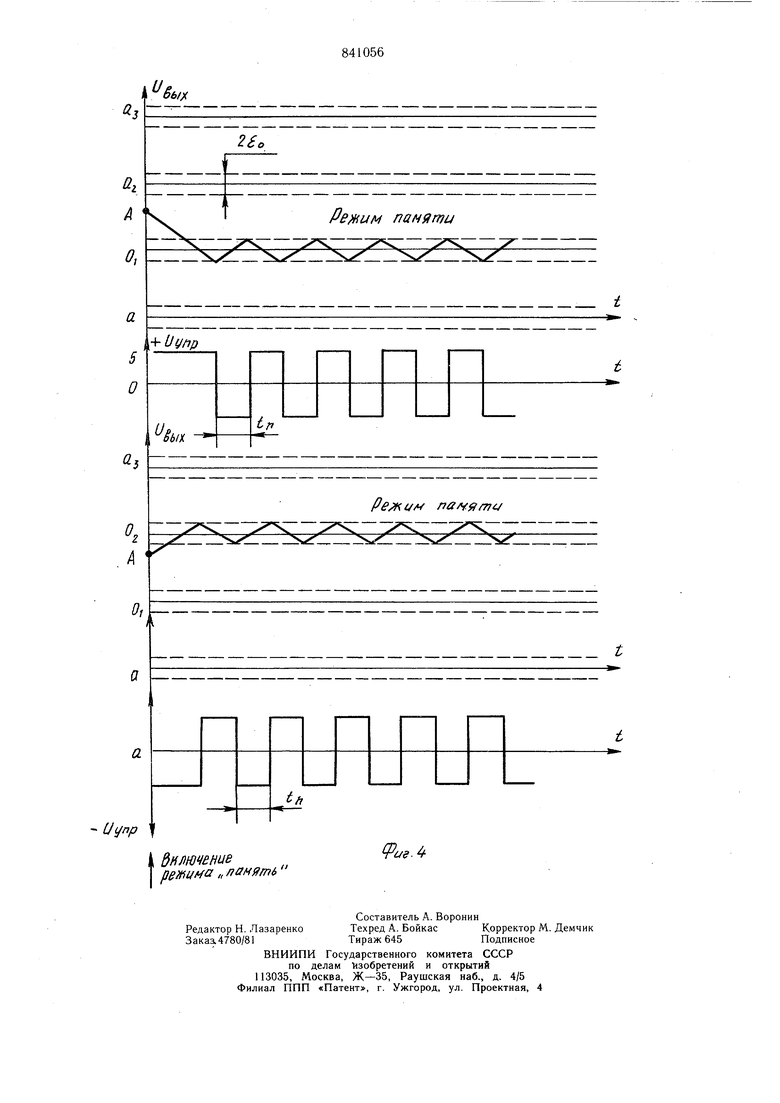

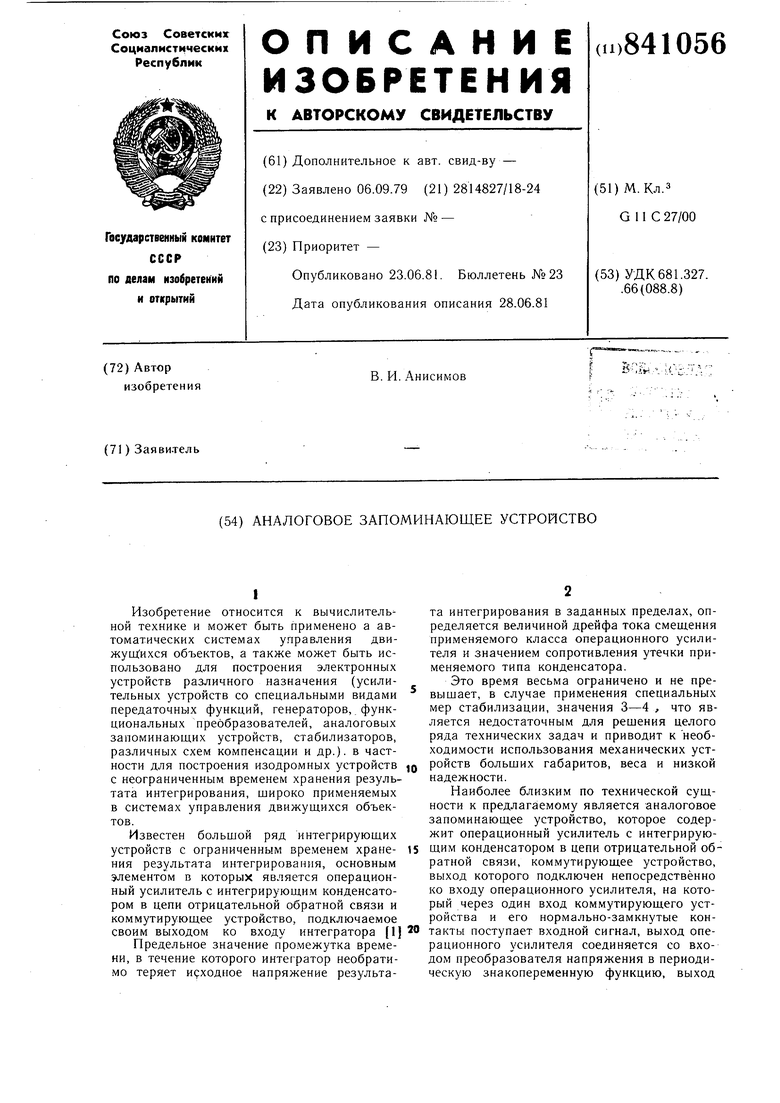

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - диаграмма

работы ячейки преобразования; на фиг. 3 - временная диаграмма работы ключей; на фиг. 4 - временная диаграмма устройства. Аналоговое запоминающее устройство содержит шину 1 управления режимом памяти, операционный усилитель 2, накопительный элемент 3 (конденсатор),пассивный элемент 4, коммутатор 5, преобразователь 6 напряжения, состоящий из ячеек-преобразования 7.1-7.П, пороговый элемент 8, триггер 9, ключи 10 и 11,шины 12 и 13 положительного и отрицательного напряжения управления и шину 14 нулевого потенциала. Каждая ячейка преобразования, например 7.1, содержит дифференциальные усилители 15 и 16, диоды 17 и 18 и резисторы 19-23. Устройство работает следующим образом.

0 Устройство работает в режиме интегрирования и в режиме памяти.

Режим .интегрирования. Входной управляющий сигнал (U.) через коммутатор 5 поступает иа вход усилителя 2, выходное напряжение которого изменяется в соответствии с выражением

Ue«..

где - суммарный входной ток; дt - время интегрирования;

С4 -.номинал конденсатора 3 в цепи отрицательной обратной связи операционного усилителя 2. Значение входного тока () определяется выражением 5 в +ПсмЬЬРуг1,

где1) - входной ток усилителя 2, определяемый отношением U jt/P/;,; R -сопротивление резистора .4; 1 см1-ток смещения операционного уси°лителя 2;

I yrl--ток утечки конденсатора 3. Для внешнего управления процессом интегрирования должно выполняться неравенство;

,(1Л у- Наличие у всех типов операционных усилителей и конденсаторов тока смешения и сопротивления утечки (т) является опреде ляющим факторйм ограниченного времени хранения результата интегрирования с заданной точностью. Количество узловых точек, в которых нап ряжение проходит через нулевое значение определяется количеством элементарных ячеек преобразованиянапряжения 7.1.-7.п, которое выбирается исходя из заданного тре бования максимального рабочего уровня выходного напряжения усилителя и точности работы устройства в режиме памяти результата интегрирования. Требуемое количество элементарных ячеек преобразователя 6 определяется выражением/оо/о 51, где6% - заданное значение относительной ошибки памяти результата интегрирования. Значение максимальной абсолютной ошибки устройства в режиме памяти определяется выражением - J . . ., lOOlo 6bl)l.. Режим памяти. При подаче управляющей команды режима памяти коммутатор 5 замыкает цепь обратной связи, состоящую из преобразователя 6 напряжения, порогового элемента 8, триггера 9 и ключей 10 и 11. Пороговый элемент 8 реализует передаточную функцию, определяемую выражениемс 0«при- Е и ЕО уровень напряжения на выходе преобразователя 6; - установочный порог элемента 8. Изменение функции f(y) представлено графиком 25 на фиг. 3. В триггере 9 используется счетный вход, а его выходы в логическом «I состоянии управляют попеременно замыканием ключей (графики 26 и 27 на фиг. 3). Уровень напряжения ()..) выбирается из условия: JOVnpJ IBK. + VI « Рассмотрим временной процесс «захвата результата интегрирования на примере потенциала т.А (фиг. 4). Для значения U вых усилителя 2, равного потенциалу т.А, один выход триггера 9, управляющий ключом 10 (+ ) начинает смещать выходное напряжение усилителя 2 в сторону его уменьшения до значения (Uoi ) при котором происходит срабатывание элемента 8 и вызванное этим изменение логических состояний выходов триггера 9 в противоположное исходному. Ключ 10 размыкается, а ключ 11 замыкается и на вход усилителя 2 начинает поступать напряжение (Uynp), которое уменьщает выходное напряжение усилителя 2 в сторону увеличения до значения (Uo( + + с о), при котором вновь происходит срабатывание элемента 8, изменение состояний выходов триггера 9 на исходное. Этот процесс повторяется неограниченно во времени, образуя вокруг узловой точки О| устойчивую зону «захвата (гистерезис «залвата) результата интегрирования. Рассмотрев аналогичный процесс «захвата потенциала т.В (фиг. 3) можно обнаружить, что зона «захвата для потенциала т.В формируется вокруг ближайшей к ней узловой точки Оз. При изменении полярности напряжения Ujnp на входах ключей 10 и 11 на обратную устойчивыми узловыми точками, вокруг которых устройство формирует зоны «захвата, станут точки выходной характеристики преобразователя б-О j, Оц и т.д. Процесс памяти в замкнутом контуре имеет автоколебательный характер (фиг. 4). Время переключения (ta) определяется выражением Т, И т-Р где Г Rx-Ca-постоянная времени интегрирования усилителя 2.. Для исключения «сбоев в работе устройства при наличии внешних помех импульсного характера необходимо выполнение неравенствап. Э -время переключения; tnoM - время действия внешней импульсной помехи; tj - гарантированное максимальное время переключения входящих в замкнутый контур релейных элементов. При выполнении условия исключения сбоев устройство полностью гарантировано от воздействия внешних импульсных помех, имеющих место в системах управления с большим количеством индукционных коммутаторов. Предлагаемое устройство, реализованное способами современной технологии производства БИС, позволяет повысить надежность устройства путем исключения механических устройств аналогичного назначения, уменьшить габариты, вес, стоимость. Формула изобретения 1.Аналоговое запоминающее устройство, содержащее операционный усилитель, в цепи обратной связи которого включен накопительный элемент, преобразователь напряжения, вход которого соединен с выходом операционного усилителя и выходом устройства, коммутатор, первый вход которого поключен ко входу устройства, а второй вход соединен с шиной управления режимом памяти, и щину нулевого потенциала, отличающееся тем, что, с целью увеличения времени хранения устройства, в него введены пороговый элемент, триггер, пассивный элемент, два ключа и шины положительного и отрицательного напряжения управления, соединенные соответственно с первыми входами ключей, вторые входы которых подсоединены к выходам триггера, выходы ключей соединены с третьим входом коммутатора, выход которого соединен через пассивный элемент со входом операционного усилителя выход преобразователя напряжения подключен -ко входу порогового элемента, выход которого соединен со входом триггера. 2.Устройство по н. 1, отличающееся тем, что преобразователь напряжения содержит п последовательно соединенных ячеек пре84образования, кажда5 из которых выполнена на двух диффренциальных усилителях, резисторах и диодах, анод первого и катод второго которых соединены с щиной нулевого потенциала, катод первого и анод второго диодов подключены через первый резистор к выходу первого дифференциального усилителя, инвертирующий вход которого соединен с выходом ячейки преобразования и выходом второго дифференциального усилителя, охваченного обратной связью по инвертирующему входу, неинвертирующий вход первого дифференциального усилителя, соединен со входом ячейки преобразования и через второй резистор с инвертирующим входом второго дифференциального усилителя, неинвертирующий вход которого подсоединен через третий резистор к шине нулевого потенциала, а через четвертый резистор к катоду первого и аноду второго диодов. Источники информации, принятые во внимание при экспертизе 1.Смолов В. Б. Аналоговые вычислительные MaujHHbi. М., «Высшая школа, 1972, с. 164-184. 2.Авторское свидетельство СССР №424156, кл. G 11 С 27/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1981 |

|

SU1015444A1 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Источник калиброванных напряжений | 1985 |

|

SU1283726A1 |

| Устройство для перемножения электрических сигналов | 1984 |

|

SU1242991A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU858111A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Функциональный аналого-цифровой преобразователь | 1983 |

|

SU1113813A1 |

| Оптоэлектронное входное устройство | 1981 |

|

SU1030983A2 |

| Устройство для решения нелинейных задач теории поля | 1982 |

|

SU1042039A1 |

| Функциональный преобразователь | 1982 |

|

SU1111181A1 |

noftamb

OfXI-H,-, JlaoiM 17 ate

Unof

to нас IS

/,-/; Auoli, 17tH fruaiatf № titfifemtfifin

f uemef IS

,,„

.А/ж

-Utac.K

Фиг. г

и

Вы)(

а,

А

памяти

х

Uijnp

ёык ч: ч па/V я/7 с/ .:vr

Авторы

Даты

1981-06-23—Публикация

1979-09-06—Подача