Изобретение относится к электро- , имическим вычислительным устройстам и может быть .использовано в ана отовых вычислительных магаинах.

Целью изобретения является повыение точности работы и быстродейстия.

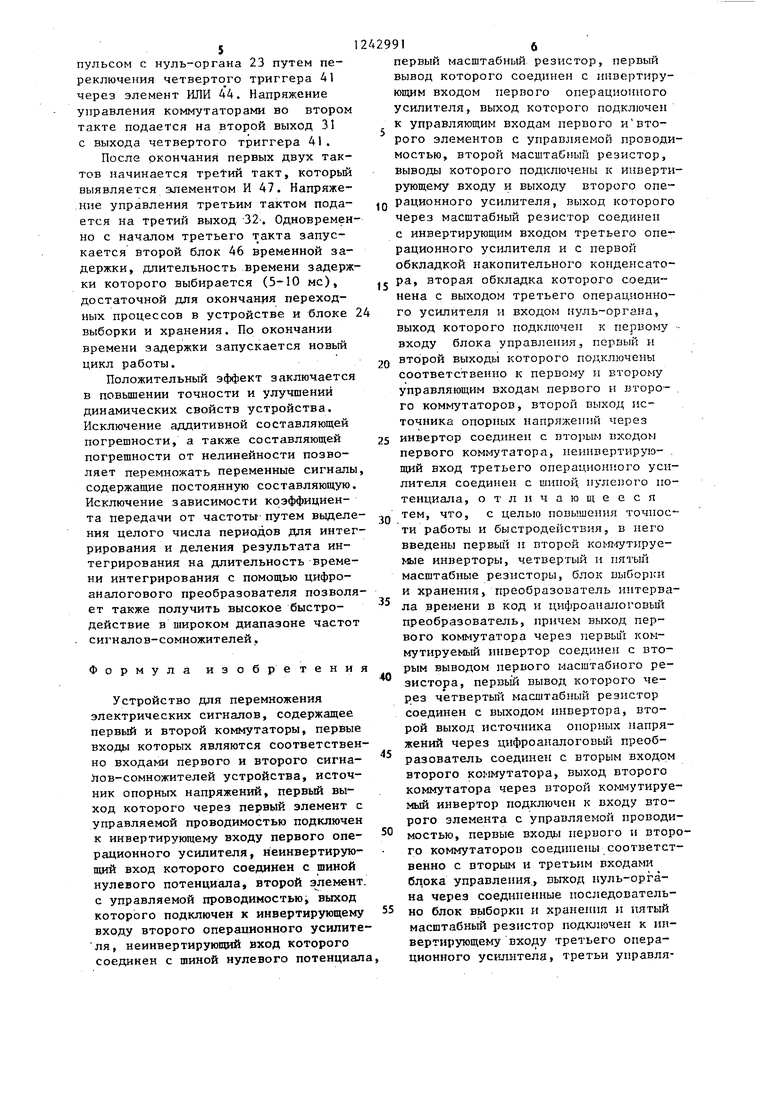

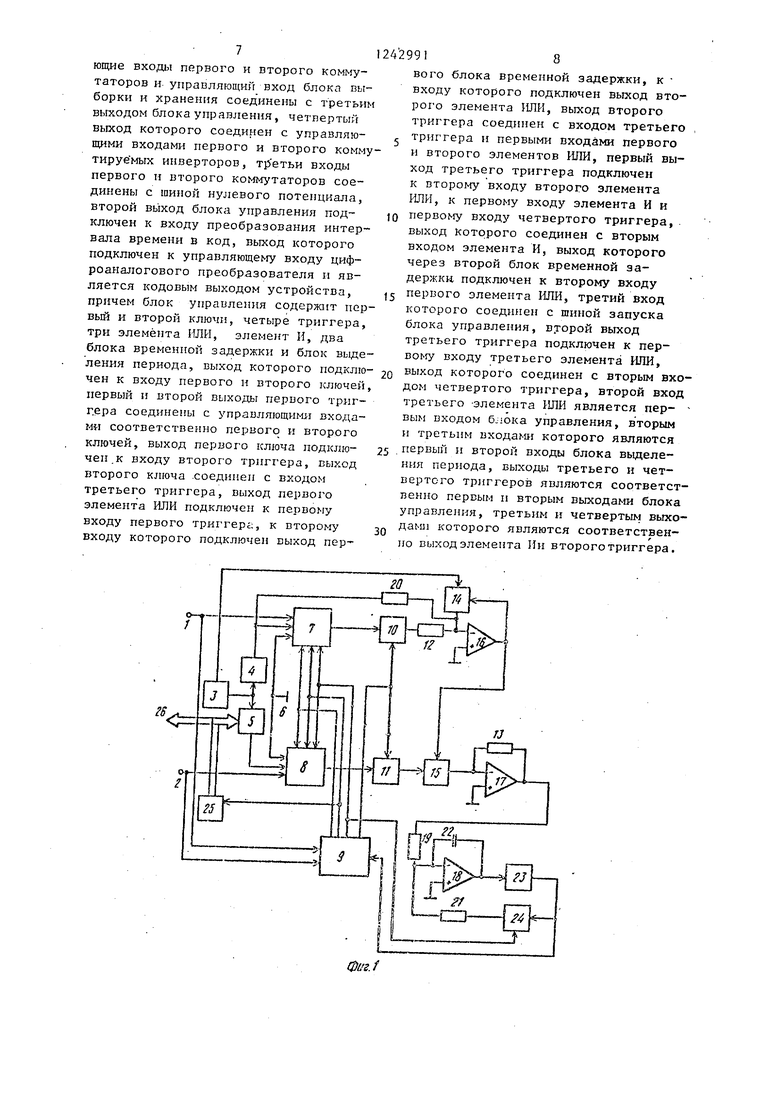

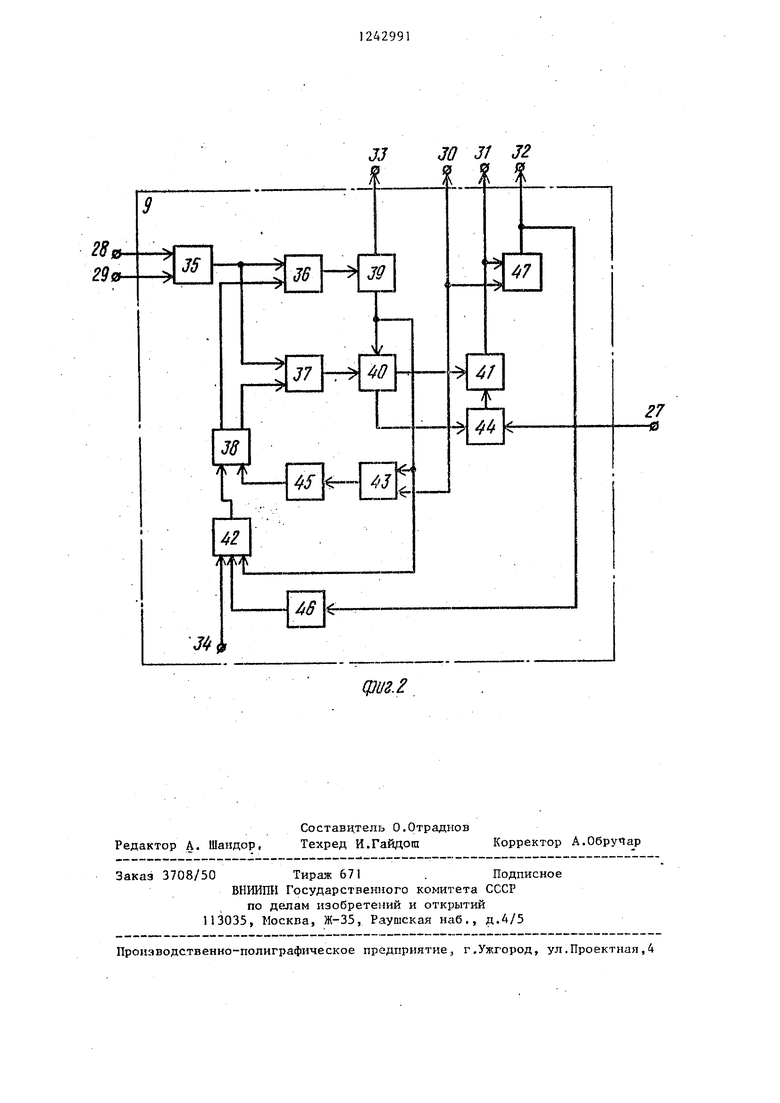

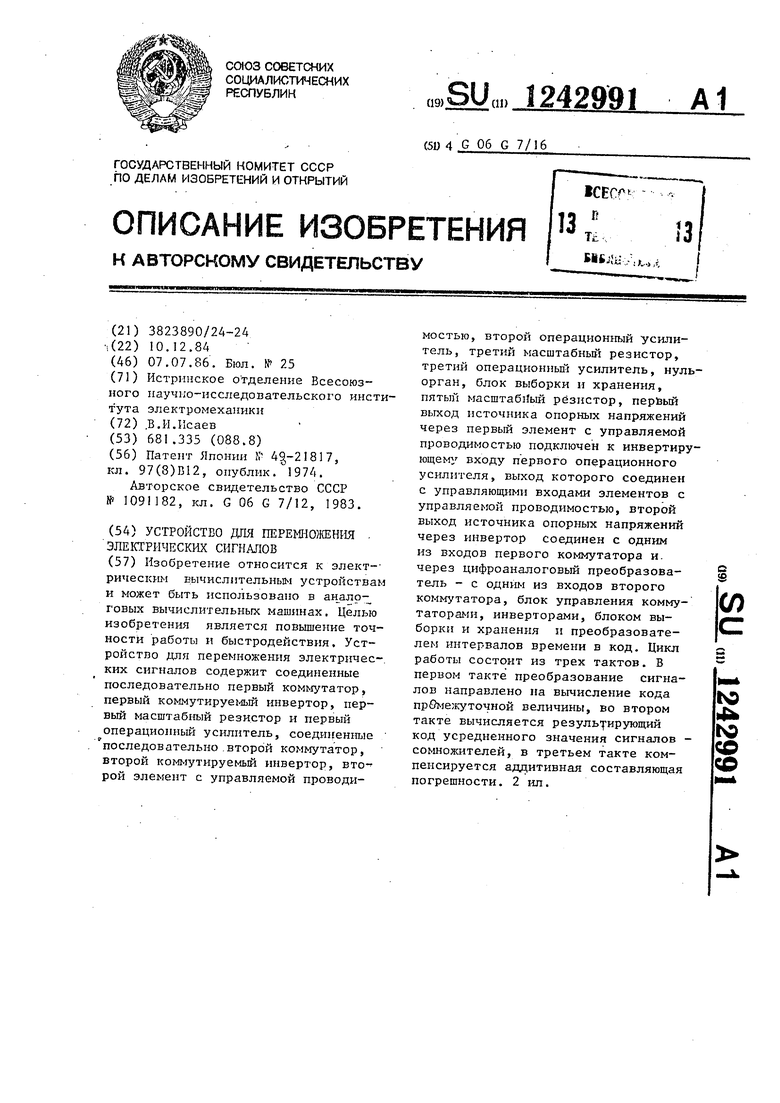

На фиг, 1 изобр&зкена функциональая схема устройства для перемножения электрических сигналов; на фиг,2- ункциональная схема блока управления.

Схема содержит входы 1 и 2 первого и второго сигналов-сомножителей, сточник 3 опорных напряжений, инвертор 4, цифроаналоговый преобразователь 5, шину 6 нулевого потенциаа, первый 7 и второй 8 коммутаторы, блок 9 управления, нервый 10 и вторе. 11 коммутируемые инверторы, первый 12 и второй 13 масштабные резисторы, первый 14 и второй 5 элемен- ть; с управляемой проводимостью, пер- вы 16, второй 17 и третий 18 операционные уС1шители, третий 19, четвертый 20 и пятый 21 масштабные резисторы, накопительньй конденсатор 22, нуль-орган 23, блок 24 выборки и хранения, нреобразователь 25 . интервала времени в код, кодовый выход 2G устройства, первый 27, ато- poii 28 И третий 29 входы блока управления, нервый 30, второй 31, третий 32 и четвертый 33 выходы, шину 34 запуска блока управления, блок 35 вы- ; деления периода, первый 36 и второй 37 ключи, первый 38, второй 39, третий 40 и четвертый 41 триггеры, пер- ный 42, второй 43 и третий 44 элементы 1ШИ, первьш 45 и второй 46 блоки временной задержки, элемент И 47. Цикл работы устройства для перемножения электрических сигналов состоит из трех тактов,

В нервом такте с блока 9 управле- ния с первого выхода 30 выдается команда, по которой к входам первого и второго коммутируемых инверторов 10 и 11 ;подключаются с помощью первого и второго коммутаторов 7 и 8 нервый и второй сигнал-сомножители с )зходов 1 п 2, В первой половине первого такта значения коэффициентов передачи первого и второго коммутиру- ei-bix инверторов 10 и 11 устанавливаются равными единице, с помощью команды 55 боты, в течение которого к входам выдаваемой блоком 9 управления с чет- первого и второго коммутируемых ин- вертого выхода 33. С первого выхода верторов 10 и 11 с помощью первого источника 3 опорных напряжений сигнал и второго коммутаторов 7 и 8 по коман

5

0

5

0

5

0

S

50

через первый элемент с управляемой проводимостью 14 поступает на первый операциоиньй усилитель 16. С выхода первого коммутируемого инвертора 10 на первый операционный усилитель 16 поступает первый, си.гнал-сомножитель. Выходным -напряжением первого операционного усилителя i 6 регулируется проводимость первого и второго элементов с управляемой проводимостью 14 и 15 до равенства проводимости. Второй операционный усилитель 17 с вторым масштабным резистором 13 образуют преобразователь напряжения в ток., Выходной сигнал второго операционного усилителя 17 интегрируется с помощью третьего операционного усшн1теля 1.8 и накопительного конденсатора 22,

Во второй ноловине первого такта блок 9 управления устанавливает коэффициенты передачи нервого и второго коммутируемых инверторов 10 и 1 1 раоны1-1и .

Преобразования сигналов в это время нроисходят аналогнчно, но с учетом знака коэффициентов передачи. При этом происходит компенсация пап-. ряжения смещения на выходе второго операцнонного усилителя 17 током противоположного зпака, создаваемого напряжением с блока 24 выборки и хранения на пятом масштабном резисторе 21. Напряжение блока 24 выборки и хранения онределяется в предыдущем цикле работы при замыкании входов первого и второго коммутаторов 7 я 8 на шину 6 нулевого нотендиала, В выходном напряжении третьего операционного усилителя 18 (т.е. выходе интегратора) исключаются составляюнще, содержащие коэффициенты передачи нервого и второго коммутируемых инверторов 10 и П, так как они по окончании первой половины такта изменяют знак на про- тивополозкный. С помощью преобразователя 25 .интервала времени в код определяется цифрошз -код длительности первого такта.-По окончании первого такта цифровой код передается на управляющий вход цифроанапогового преобразователя 5.

Затем начинается второй такт радс с блока 9 управления подключаются спорные напряжения противоположной полярности с выходов источника 3 опорных напряжений. Пакопителыгьш конденсатор 22 разряжается до нулевого уровня, который фиксируется с помощью нуль-органа 23 и является моментом окончания второго такта. При этом на выходе 26 формируется цифровой код

К

U, и

N К. Щ-и., (1)

где и IS - среднее значение произведения первого и второго сигнапов-сомножите - лей;

-коэффициент преобразова- пия;

-значения папряженнй первого и второго сигналов- сомножителей с входов

1 и 2.

Из выражения (1) следует, что цифровой код пропорционален среднему зпачеиню произведения сит налов- сомножителей. о

В выходном сигнале отсутствует аддитивная составляющая погрешности, составляющая погрешности от нелипей- ности, как результат смещения операционных усилителей и постоянняя составляющая .

В третьем такте работы входы первого и второго коммутируе1Ф1Х инверторов 10 и II с помо1.цью первого и второго коммутаторов 7 и 8 по команде с блока 9 управления подключаются к шине нулевого потенциала. К выходу .нуль-органа 23 подключается вход бло ка 24 выборки и хранения, на котором запоминается аддитивная составляющая погрешности. В первом и втором тактах вход блока 24 выборки н хранения отключается от выхода нуль-органа 23 выходное напряжение которого компен- сирует аддитивную составляющую погрености .

Первый и второй сигпалы-сомножи- тели должны иметь одинаковЬе или кратные целому числу периоды.

Блок управления работает след яо- щим образом.

Но команде Пуск, подаваемой на раздельный вход тирггера 38 через первый элемент ИЛИ 42 с шины 34, триггер 38 переходит в состояние, при котором второй ключ 37 открывается, а первый ключ 36 закрывается.

,Q

15

20

25

0

5

0

5

При этом с выхода блока 35 выделения периода 35 короткие импульсы с периодом, равным больщему периоду сигнала-сомножителя (если периоды снгиа-пов-сомножителей не равны), поступают на раздельный вход третьего триггера 40. Третю триггер 40 переходит в состояние, которое соответствует nepBOhfy такту ра боты. Одновременно с началом первого такта через элемент ИЛИ 43 запускается первый блок 45 временной задержки и четвертый триггер 41 через элемент 1-ШИ 44 переходит в- состояние, не соответствующее второму такту. Длительность задержки первого блока 45 временной задержки выбирается равной половине максимального периода сигнала-сомножителя.

По окончании времени задержки первыл триггер 38 перерводится в состояние, при котором первьш ключ 36 открывается, а второй ключ 37 закрывается. Тогда первьп импульс с блока 35 выделения периода переведет второй триггер 39 в противоположное состояшге, так как он постунает на его вход. Выходное напряже- пие второго триггера 39 поступает на четвертый выход 33 блока управления , Перепадом напряжения с другого выхода второго триггера 39 запускается первый блок 45 временной задержки и первый триггер 38 переходит в состояние, при котором первый ключ 36 закрывается, а второз ключ 37 открывается. Третий триггер 40 в этом случае остается в исходном состоянии, т.е. не переключается.

По окончании времепи задержки первый триггер 38 открывает первый ключ 36 п закрывает второй ключ 37. Второй триггер 39 переходит в новое состояние с первым импульсом, приходящим от б;гока 35 выделения периода. Однако с выхода второго триггера 39 импульс возвращает только третий триггер 40 в состояние, соответствующее окончанию первого такта. Первьш блок 45 времепной задержки и первый триггер 38 в этом случае не подвергшотся В1слючениям. Напряжение управления работой коммутаторов в первом такте подается па первьш выход 30 с выхода первого триггера 38. С окоичшшем первого такта запускается четвертый триггер 41 и 1гачи-. нается второй такт работы. Окончание второго такта фиксируется импульсом с нуль-органа 23 путем переключения четвертого триггера 41 через элемент ИЛИ 44. Напряжение управления коммутаторами во втором такте подается на второй выход 31 с выхода четвертого триггера 41.

После окончания первых двух тактов начинается треФий такт, которьм выявляется элементом И 47. Напряжение управления третьим тактом подается на третий выход 32. Одновременно с началом третьего такта запускается второй блок 46 временной задержки, длительность времени задержки которого выбирается (5-10 мс), достаточной для окончания переходных процессов в устройстве и блоке выборки и хранения. По окончании времени задержки запускается новый цикл работы.

Положительный эффект заключается в повьшении точности и улучшений динамических свойств устройства. Исключение аддитивной составляющей погрешности, а также составляющей погрешности от нелинейности позволяет перемножать переменные сигналы содержащие постоянную составляющую. Исключение зависимости коэффициента передачи от частоты- путем выделения целого числа периодов для интегрирования и деления результата интегрирования на длительность времени интегрирования с помощью цифро- аналогового преобразователя позволяет также получить высокое быстродействие в широком диапазоне частот сигналов-сомножителей.

Формула изобретени

Устройство для перемножения электрических сигналов, содержащее первый и второй коммутаторы, первые входы которых являются соответственно входами первого и второго сигналов-сомножителей устройства, источник опорных напряжений, первый выход которого через первый элемент с управляемой проводимостью подключен к инвертирующему входу первого операционного усилителя, неинвертирующий вход которого соединен с шиной нулевого потенциала, второй злемент. с управляемой проводимостьюi выход которого подключен к инвертирующему входу второго операционного усилителя, неинвертирующий вход которого соединен с шиной нулевого потенциала

4

15

20

.

2429915

первый масштабный резистор, первый вывод которого соединен с инвертирующим входом первого операционного усилителя, вьосод которого подключен к управляющим входам первого и второго элементов с управляемой проводимостью, второй масштабный резистор, выводы которого подключены к инвертирующему входу и выходу второго опе- Q рационного усилителя, выход которого через масштабный резистор соединен с инвертирующим входом третьего операционного усипителя и с первой обкладкой накопительного конденсатора, вторая обкладка которого соединена с выходом третьего операционного усилителя и входом нуль-органа, выход которого подключен к первому - входу блока управления, первый и второй выходы которого подключены соответственно к первому и второму управляющим входам первого и второго комкгутаторов, второй выход ИСТОЧНИКЕ опорных напряжений через инвертор соединен с вторым входом первого коммутатора, пеиивертирую- . щий вход третьего операционного усп- лителя соединен с шипой, пулеиого потенциала, отличающееся тем, что, с целью повышения точпос- ти работы и быстродействия, в пего введены первьй и второй коммутируемые инверторы, четвертый и пятый масштабные р€;зисторы, блок выборки и хранения, преобразователь интервала времени в код и цифроанапоговый преобразовате ль, причем выход первого коммутатора через первьш: кон- мутируемьй инвертор соединен с вторым выводом первого масштабного резистора, первьш вывод которого через четвертьй масштабный резистор

25

30

35

40

соединен с выходом инвертора, второй выход источника опорных напряжений через цифроаналоговый преобразователь соединен с вторым входом второго конкутатора, выход второго коммутатора через второй коммутируемый инвертор подключен к входу второго злемента с управляемой проводимостью, первые входы первого и второго коммутаторов соединены соответственно с вторым и третьим входами блока управления., выход нуль-органа через соединенные последовательно блок выборки и хранения и пятый масштабный резистор подключен к инвертирующему входу третьего операционного усилителя, третьи управляюгдие входы первого и второго коммутаторов и управляющий вход блока выборки и хранения соединены с третьим выходом блока упрашгения, четвертый выход которого соединен с управляющими входами первого и второго комму тируе мых инверторов, тр етьи входы первого и второго коммутаторов соединены с шиной нулевого потенциала, второй выход блока управления подключен к входу преобразования интервала времени в код, выход которого подключен к yпpaвляющe ry входу циф- роаналогового преобразователя и является кодовым выходом устройства, причем блок управлешш содержит первый и второй ключи, четыре триггера, три элемента ИЛИ, элемент Н, два блока временпой задержки и блок выделения периода, выход которого подключен к входу первого и второго ключей первый и второй выходы первого триг- г.ера соединены с управляющими входами соответственно первого и второго ключей, выход первого ключа подключен, к входу второго триггера, выход второго ключа .соединен с входом третьего триггера, выход первого элемента ИЛИ подключен к первому входу первого триггера, к второму входу которого подключен выход пер

10

2429918

во го блока временной задержки, к входу которого подключен выход второго элемента ИЛИ, выход второго триггера соединен с входом третьего , триггера и первыми входами первого и второго элементов ШШ, первый выход третьего триггера подключен к второму входу второго элемента ИЛИ, к первому входу элемента И и первому входу четвертого триггера, выход Которого соединен с вторым входом элемента И, выход которого через второй блок временной задержки, подключен к второму входу первого элемента ИЛИ, третий вход которого соединен с шиной запуска блока управления, в.торой выход третьего триггера подключен к первому входу третьего элемента ШШ, выход которого соединен с вторым входом четвертого триггера, второй вход третьего -элемента Ш1И является первым входом б.-юка управления, вторым и третьим входами которого являются первый и второй входы блока выделения периода, выходы третьего и четвертого триггеров являются соответственно первым и вторым выходами блока управления, третьим и четвертым выходами которого являются соответственно выход элемента Ии второго триггера.

15

20

25

30

gjuB.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перемножения напряжений | 1983 |

|

SU1091182A1 |

| Генератор пилообразного напряжения с переменной крутизной | 1987 |

|

SU1495982A1 |

| Функциональный преобразователь | 1977 |

|

SU696490A1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347027A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| Анализатор импульсных моментовлиНЕйНыХ СиСТЕМ АВТОМАТичЕСКОгОРЕгулиРОВАНия | 1979 |

|

SU847283A1 |

| Времяимпульсный квадратичный преобразователь | 1986 |

|

SU1406610A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Элемент с управляемой проводимостью | 1986 |

|

SU1334164A1 |

Изобретение относится к элект- рическим вычислительным устройствам и может быть иснользовано в говых вычислительных машинах. Целью изобретения является повышение точности работы и быстродействия, Устройство для перемножения электричес-. ких сигналов содержит соединенные последовательно первый коммутатор, первый коммутируемый инвертор, первый масштабный резистор и первый операцио1и1ый усилитель, соедшгенные последовательно.второй коммутатор, второй коммутируемьй инвертор, вто- рой элемент с управляемой проводимостью, второй операционный усилитель, третий масштабный резистор, третий операционньш усилитель, нуль- орган, блок выборки и хранения, пятый масштаб11ый резистор, перйый выход источника опорных напряжений через первый элемент с управляемой проводимостью подключен к инвертирующему входу первого операционного усилителя, выход которого соединен с управляющими входами элементов с управляемой проводимостью, второй выход источника опорных напряжений через инвертор соединен с одним из входов первого коммутатора и. через цифроаналоговый преобразователь - с одним из входов второго коммутатора, блок управления коммутаторами, инверторами, блоком выборки и хранения и преобразователем интервалов времени в код. Цикл работы состоит из трех тактов. В перво - такте преобразование сигналов направлено на вычисление кода промежуточной величины, во втором такте вычисляется резуль ирующий код усредненного значения сигналов - сомножителей, в третьем такте компенсируется аддитивная составляющая погрешности. 2 ил. § (Л с ю « ю QD

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

| Устройство для перемножения напряжений | 1983 |

|

SU1091182A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-12-10—Подача