(54) АНАЛОГОВОЕ ЗАПОМИНАКИДЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU841056A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU832601A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU771729A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015444A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU729641A1 |

| Интегратор | 1982 |

|

SU1062726A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКОГО СОПРОТИВЛЕНИЯ ТОЧЕК АКУПУНКТУРЫ | 1992 |

|

RU2027403C1 |

| СИСТЕМА ДИАГНОСТИКИ ЗАБОЛЕВАНИЙ | 1991 |

|

RU2007755C1 |

| Устройство для автоматизированного контроля параметров реле | 1985 |

|

SU1265704A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1231610A1 |

Изобретение относится к области аналоговой вычислительной техники и может быть использовано в системах управления движущихся объектов для неограниченного во,времени хранения результата интегри рования или запоминания мгновенного ана чения напряжения непрерывного аналогового сигнала с постоянной памятью. Известно устройство для увеличения времени хранения результата интегрирования аналогового сигналы. Оно содержит операционный усилитель с интегрирующим конденсатором в цепи отрицательной обрат ной связи, коммутирующее устройство, выход которого подключен непосредственно ко входу операционного усилителя, на который через один вход коммутирующего устройства и его нормально-оамкнутые контакты поступает входной сигнал, вы-- ХОДоперационного усилителя соединяется со входом преобразователя напряжения в периодическую знакопеременную функцию, выход которого. подключается к другому входу коммутируюихего устройства 1}. Недостатки устройства - значение выходного напряжения устройства не бупёт сохраняться независимо от времени, а будет продолжать изменяться в установившемся режиме благодаря оействию в замкнутом контуре цепи задержки, явл$пощёйся причиной накопления статической ошибки рассогласования. Пра этом скорость изменения выходного напряжения будет переменной. Непосредственное подключение выхода преобразователя ко входу операционного усилителя создает реальные предпосылки для возникновения генерации в интеграторе, а следовательно, и потере устойчивости ycrpcrfiCTBoM в целом. Наиболее близким по технической сущности к предлагаемому является аналоговое запс 1инающ8в устройство, в котором решается зааач§ стабилизации исходного напряжения на накопительном конденсаторе на дискретных уровнях, вырабатываемых генератором ступенчатого сигнала 2j. Устройство .содержит запоминающий элемент на накопительном конденсаторе я

систему коррекции для стабилизации напряжений на конденсаторе, в котором система коррекции выполнена в вице генератора ступенчатого сигнала, подключенного чере последовательно соединенные ключ, диод и резистор к обкладке накопительного к:онденсагора и ко входу компаратора, другой вход которого соединен с выходом генератора ступенчатого сигнала.

Недостатки запоминающего устройства управляемое изменение напряжения на конденсаторе в проме кутках между следованиями ступенчатых импульсов с генератора Должно происходить только в сторону умень- шения уменьшение заряда на конденсаторе за период следования управляющего ступенчатого напряжения должно быть не более заданного требованиями дискретного шага запоминающего напряжения.

Необходимость выполнения первого

требования сужает функциональные возможности устройства, так как является неприемлемым, например, при построении интегрирующих устройств на базе операционных усилителей и запоминания устройством результата интегрирования входного аналогового сигнала, поскольку в этом случае, после отключения входного сигнала, изменение заряда на конденсаторе определяется, в основном, током смещения операционного усилителя, величина и знак которого в значительной степени зависят ог температуры окружающей среды и имеют вероятностный характер,

С учетом всего комплекса дестабилизирующих факторов, имеющих место в реальной аппаратуре, необходимость выполнения второго требования снижает его точность Или требует применения специальных аппаратурных мер защиты, что уве личивает габариты, вес и снижает надежность устройства.

Предъявляемое к системам управления движущихся объектов требование восстановления своих функций после перерывов в пигании, объекта накладывает дополнительные требования к запоминающим аналоговым устройствам, которые не удовлетворяет ни одно из известных устройств.

Цель изобретения - увеличение времена хранения аналогового запоминающего устройства.

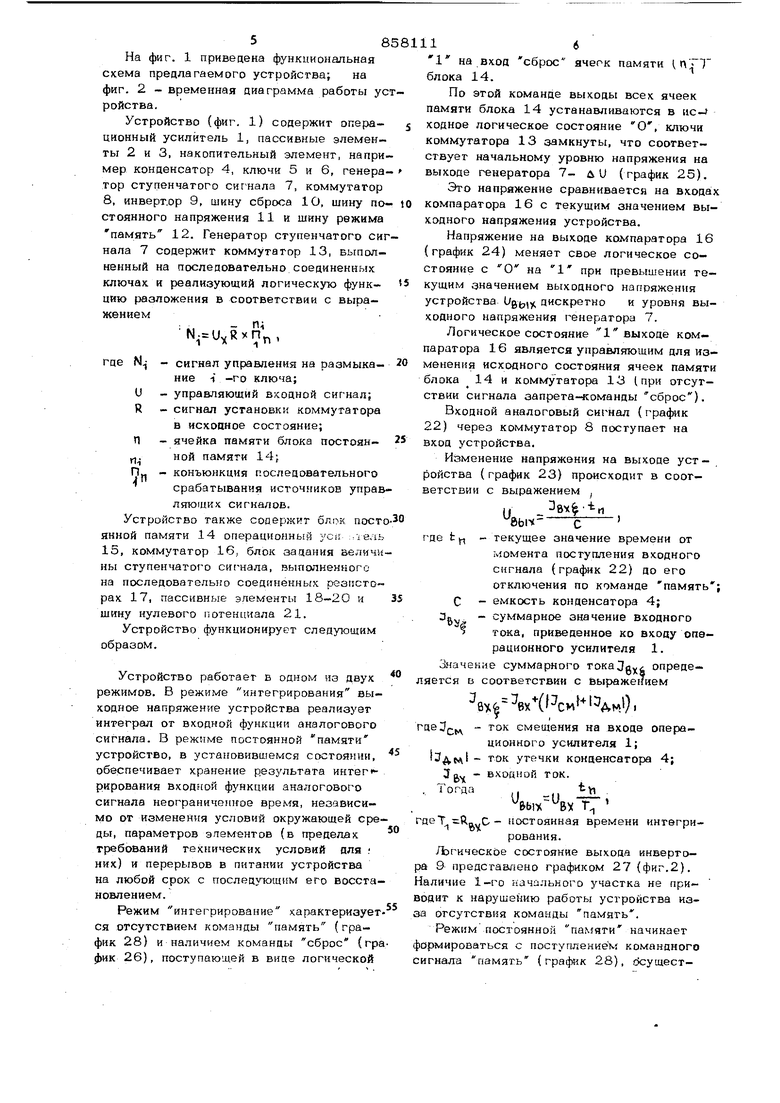

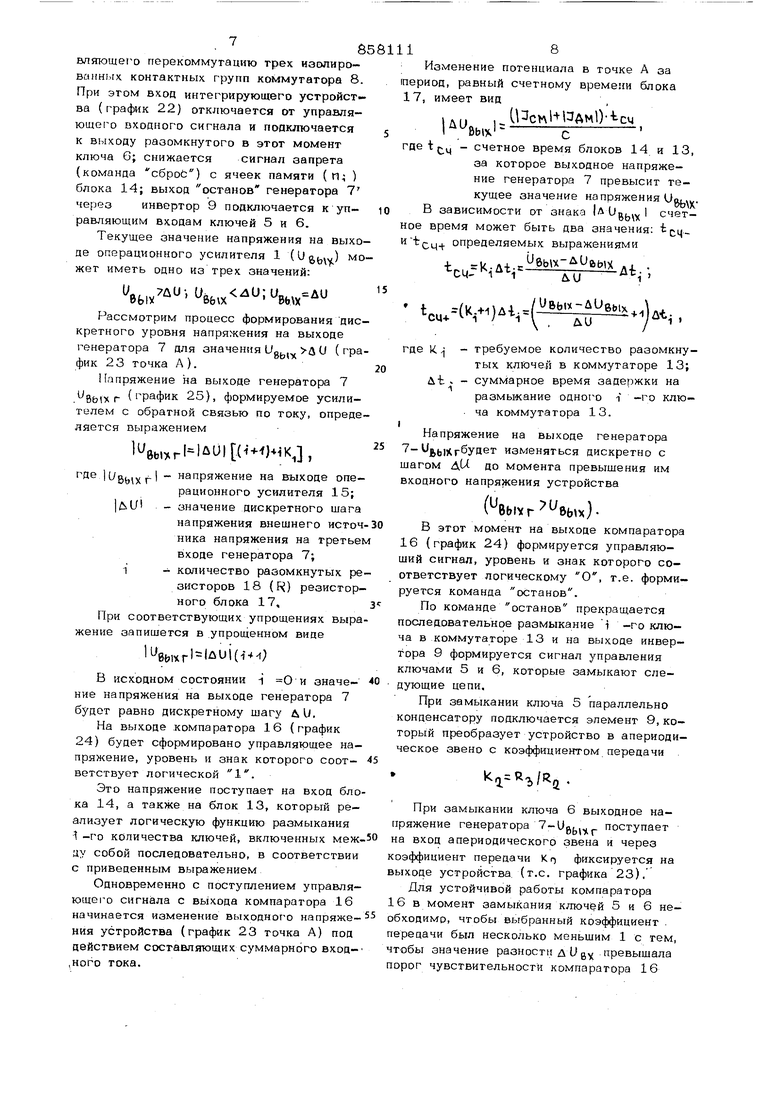

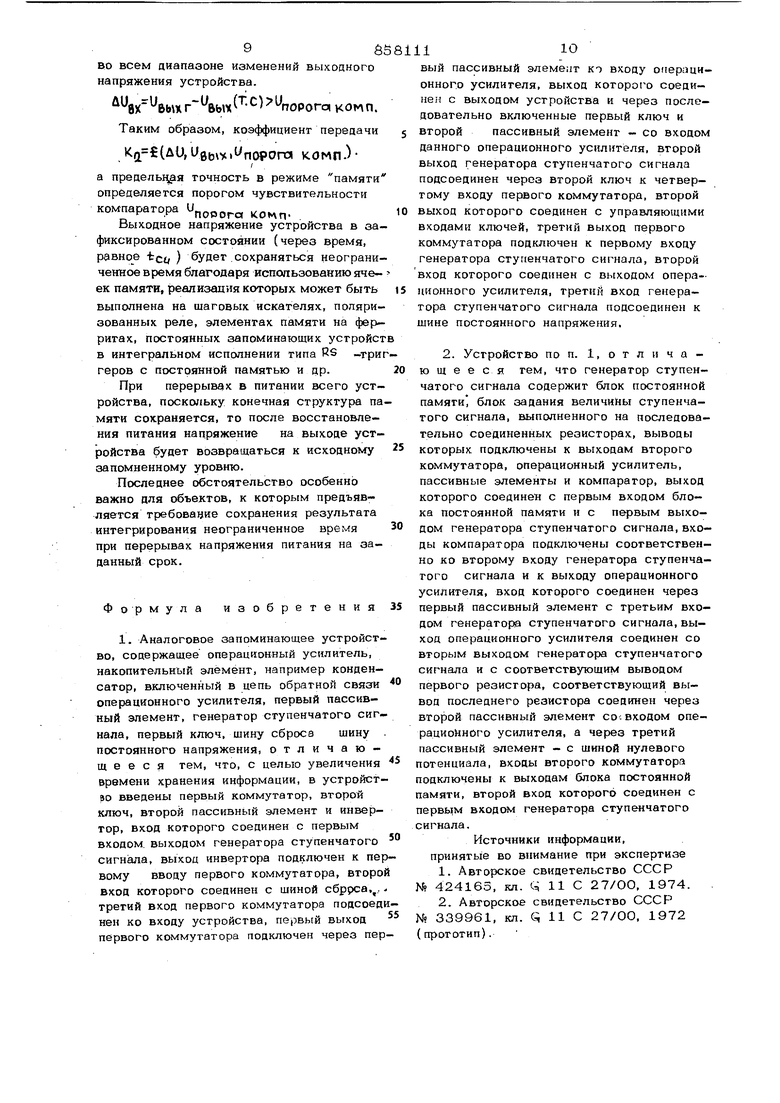

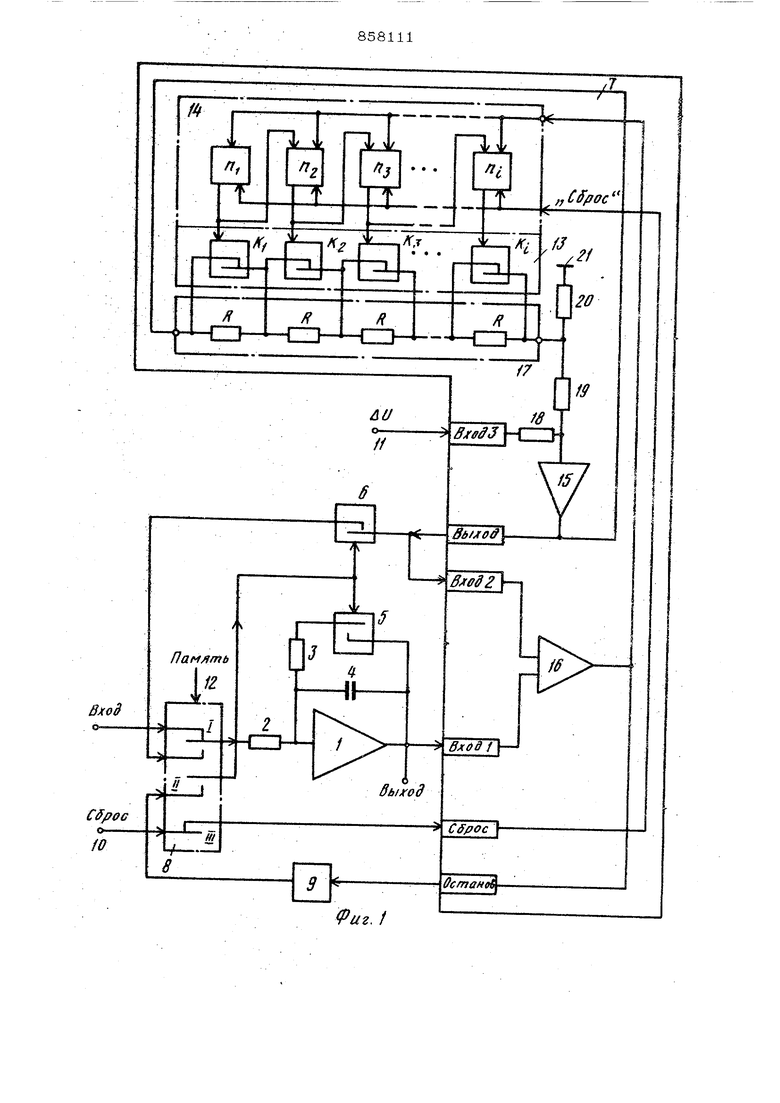

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее операционный усилитель, накопительный элемент, например, конденсатор, включенный в цепь обратной связи операционного усилителя, первый пассивый элемент, генератор ступенчатого сигнала, первый ключ, щину сброса и щину остоянного напряжения, введены первый оммутатор, второй ключ, второй пассивый элемент и инвертор, вход которого оединен с первым выходом генератора тупенчатого сигнала, выход инвертора подключен к первому входу первого коммутатора, второй вход которого соединен шиной сброса, третий вход первого оммутатора подсоединен ко входу устройства, первый выход первого коммутатора подключен через первый пассивный элемент ко входу операционного усилитея, выход которого соединен с выходом устройства и через последовательно включенные первый ключ и второй пассивный элемент - со входом данного операционного усилителя, второй выход генератора ступенчатого сигнала подсоединен через второй ключ к четвертому входу первого коммутатора, второй выход которого соединен с управляющими входами ключей, третий выход первого коммутатора, подключен к первому входу генератора ступенчатого сигнала, второй вход которого соединен с выходом операционного усилителя, третий вход генератора ступенчатого сигнала подсоединен к щине постоянного напряжения, а также генератор ступенчатого сигнала содержит блок постоянной памяти блок задания величины ступенчатого сигнала, выполненного на последовательно соединенных резисторах, выводы которь1х подключены к выходам второго коммутатора, операционный усилитель,пассивные элементы и компаратор, выход которого соединен с первым входом блока постоянной памяти с первым выходом генератора ступенчатого сигнала, входы компаратора подключены соответственно ко второму входу генератора ступенчатого сигнала и к выходу операционного усилителя, вход которого соединен через первый пассивный элемент с третьим входом генератора ступенчатого сигнала, выход операционного усилителя соединен со вторым выходом генератора ступенчатого сигнала, и с соответствующим выводом -первогорезистора, соответствующий вывод последнего резистора соединен через второй пассивный элемент со входом операционного усилителя, а через третий пассивный элемент - с шиной нулевого потенциала, входы второго коммутатора подключены к выходам блока потоянной памяти, второй вход которого соединен с первым входом генератора ступенчатого сигнала. На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временная диаграмма работы ус ройства. Устройство (фиг, 1) содержит опера- ционный усилитель 1, пассивные элементы 2 и 3, накопительный элемент, напри мер конденсатор 4, ключи 5 и 6, генера тор ступенчатого сигнала 7, коммутатор 8, инверт.ор 9, шину сброса Ю, шину по стоянного напряжения 11 и шину режима память 12. Генератор ступенчатого си нала 7 содержит коммутатор 13, выполненный на последовательно соединенных ключах и реализующий логическую функцию разложения в соответствии с выражениемN. , где N - сигнал управления на размыкание -i -го ключа; и - управляющий в/содной сигнал; R - сигнал усгановкк коммутатора в исходное состояние; П - ячейка памяти блока постоян. ной памяти 14; П„ - конъюнкция последовательного срабатывания источников управ ляющих сигналов. Устройство также содержит блок пост янной памяти 14 операционнь й ycri ::ie.ib 15, коммутатор 16, блок задания величи ны ступенчатого сигнала, выполненного на последовательно соединенных резисторах 17, пассивные элементы 18-2О и шнну нулевого потенциала 21. Устройство функционирует следующим образом. Устройство работает в одном из двух режимов. В режиме интегрирования выходное напряжение устройства реализует интеграл от входной функции аналогового сигнала. 3 режиме постоянной памяти устройство, в ycraifовившемся состоянии, обеспечивает хранение результата интег рирования входной функции аналогового сигнала неограниченное время, независимо от изменения условий окружающей сре ды, параметров элементов (в пределах требований тех;нических условий для ; них) и перерывов в питании устройства на любой срок с последующим его восстановлением. Режим интегрирование характеризует ся отсутствием команды память (график 28) и наличием команды сброс (гра фик 26), поступающей в вице логической 1 на вход сброс ячеок памяти блока 14. По этой команде выходы всех ячеек памяти блока 14 устанавливаются в nc-f ходкое логическое состояние О , ключи коммутатора 13 замкнуты, что соответствует начальному уровню напряжения на выходе генератора 7- д U (график 25). Это напряжение сравнивается на входах компаратора 16 с текущим значением выходного напряжения устройства. Напряжение на выходе компаратора 16 (график 24) меняет свое логическое состояние с О на при превышении текущим значением выходного напряжения устройства дискретно и уровня выходного напряжения генератора 7. Логическое состояние 1 выходе компаратора 16 является управляющим для изменения исходного состояния ячеек памяти блока 14 и коммутатора 13 (при отсутствии сигнала запрета-гкоманды сброс). Входной аналоговый сигнал (график 22) через коммутатор 8 поступает на вход устройства. Изменение напряжения на выходе уст - ройства ( график 23) происходу1Т в соответствии с выражением , текущее значение времени от момента поступления входного сигнала (график 22) до его отключения по команде память; емкость конденсатора 4; За - суммарное значение входного тока, приведенное ко входу операционного усилителя 1. Значение суммарного опредеяется в соответствии с выражением - aeZJj- - ток смещения на входа операционного усилителя 1; Здр - ток утечки конденсатора 4; Jg - входной ток. Я -П 1 Т цеТ Ra.C- ностоянная времени интегрирования. /Ьгическое состояние выхода инвертоа 9 представлено графиком 27 (фиг.2). аличие 1-го начального участка не приодит к нарушению работы устройства иза отсутствия команды память. Режимпостоянной памяти начинает ормироваться с поступлением командного игнала память (график 28), бсущест. 65 вляющего перекоммугацню грех изолиро- BaiiHi.rx контактных групп коммутатора 8. При этом вход интегрирующего устройст-ва (график 22) отключается от управляющего входного сигнала и подключается к выходу разомкнутого в этот момент ключа б; снижается сигнал запрета (команда сброЬ) с ячеек памяти ( п ) блока 14; выход останов генератора 7 через инвертор 9 подключается к управляющим входам ключей 5 и 6. Текущее значение напряжения на выходе операционного усилителя 1 (J g,.) жет иметь одно из грех значений: вь,. Рассмотрим процесс формирования дискретного уровня напряжения на выходе генератора 7 для значения y, Л U ( график 23 точка А ). Напряжение на выходе генератора 7 йых г (график 25), формируемое усилителем с обратной связью по току, определяется выражением l ebi rl-lul l HKj, где lUBt,,xrl напряжение на выходе операционного усилигеля 15; |М/ значение дискретного шага напряжения внешнего источ ника напряжения на третьем входе генератора 7; 1- количество разомкнутых ре зисторов 18 (f) резисторного блока 17, При соответствующих упрощениях выра жение запишется в упрощенном виде 1 вычг1 ли|( в исходном состоянии 1 О и значение напряжения на выходе генератора 7 будет равно дискретному шагу ли, На выходе компаратора 16 (график 24) будет сформировано управляющее напряжение, уровень и знак которого соответствуот логической 1. Это напряжение поступает на вход бло ка 14, а также на блок 13, который реализует логическую функцию размыкания 1 -го количества ключей, включенных меж ау собой последовательно, в соответствии с приведенным выражением Одновременно с поступлением управляющего сигнала с вЫкода компаратора 16 начинается изменение выходного напряже- ния устройства (график 23 точка А) под действием составляющих суммарного вход,ного тока. 18 Изменение потенциала в точке А за ериод, равный счетному времени блока 17, имеет вид 1Л1, 1 )--Ьси |AUg(,,l 5 где t JSц - счетное время блоков 14 и 13, за которое выходное напряжение генератора 7 превысит гекущее значение напряжениям В зависимости от знака I tJgfj y 1 счетое время может быть два значения: .Ц Сщ- определяемых выражениями t,,,.b,,,t.. tcu.-(N-)t,-( ;r-) . рде : - требуемое количество разомкнутых ключей в коммутаторе 13; д-Ь . - суммарное время задержки на размыкание одного i -го клю. ча коммутатора 13. Напряжение на выходе генератора изменяться дискретно с шагом Л( до Момента превышения им входного напряжения устройства JblVr e x)В этот момент на выходе компаратора 16 (график 24) формируется управляющий сигнал, уровень и знак которого соответствует логическому О, т.е. формируется команда останов. По команде останов прекращается последовательное размыкание i -го ключа в коммутаторе 13 и на выходе инвертора 9 формируется сигнал управления ключами 5 и 6, которые замыкают следующие цепи. При замыкании ключа 5 параллельно конденсатору подключается элемент 9, который преобразует устройство в апериодическое звено с коэффициентом передачи При замыкании ключа 6 выходное наряжение генератора 7-Ugfj. поступает а вход апериодического звена и через оэффициент передачи г) фиксируется на ыходе устройства (т.е. графика 23), Для устойчивой работы компаратора 6 в момент замыкания ключей 5 и 6 небходимо, чтобы выбранный коэффициент . ередачи был несколько меньшим 1 с тем, тобы значение разности дУцу превышала орог чувствительности компаратора 16 9S во всем диапазоне изменений выходного напряжения устройства. (- ПОРОГа| . Таким образом, коэффициент передачи К((ди,Ug(,y,Unoponoi компЗа прецелы ая точность в режиме памяти определяется порогом чувствительности компаратора U ppora . Выходное напряжение устройства в зафиксированном состоянии (через время, равно е -fcct ) будет .сохраняться неограниченное время благодаря использованию ячеек памяти, {эеализадиякоторых может быть выполнена на шаговых искателях, поляризованных реле, элеменгах памяти на ферритах, постоянных запоминающих устройст в интегральном исполнении типа RS -три геров с постоянной памятью и цр. При перерывах в питании всего устройства, поскольку конечная структура па мяти сохраняется, то после восстановления питания напряжение на выходе устройства будет возвращаться к исходному запомненному уровню. Последнее обстоятельство особенно важно для объектов, к которым предъявляется требование сохранения результата интегрирования неограниченное время при перерывах напряжения питания на заданный срок. Формула изобретения 1. Аналоговое запоминающее устройство, содержащее операционный усилитель, накопительный элемент, например конденсатор, включенный в цепь обратной связи операционного усилителя, первый пассивный элемент, генератор ступенчатого сигнала, первый ключ, шину сброса шину постоянного напряжения, отличающееся тем, что, с целью увеличения времени хранения информации, в устройство введены первый коммутатор, второй ключ, второй пассивный элемент и инвертор, вход которого соединен с первым входом, выходом генератора ступенчатого сигнала, выход инвертора подключен к пер вому вводу первого коммутатора, второ вход которого соединен с шиной сбррса,., третий вход первого коммутатора подсоед нен ко входу устройства, первый выход первого коммутатора подключен через пер 110 вый пассивный элемент кт входу операционного усилителя, выход которо1о соединен с выходом устройства и через последовательно включенные первый ключ и второй пассивный элемент - со входом данного операционного усилителя, второй выход генератора ступенчатого сигнала подсоединен через второй ключ к четвертому входу первого коммутатора, второй выход которого соединен с управляющими входами ключей, третий выход первого коммутатора подключен к первому входу генератора ступенчатого сигнала, второй вход которого соединен с ВЬЕХОДОМ операционного усилителя, третий вход генератора ступенчатого сигнала подсоединен к шине постоянного напряжения, 2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что генератор ступенчатого сигнала содержит блок постоянной памяти блок задания величины ступенчатого сигнала, выполненного на последовательно соединенных резисторах, выводы которых подключены к выходам второго коммутатора, операционный усилитель, пассивные элементы и компаратор, выход которого соединен с первым входом блока постоянной памяти и с первым выходом генератора ступенчатого сигнала, входы компаратора подключены соответственно ко второму входу генератора ступенчатого сигнала и к выходу операционного усилителя, вход которого соединен через первый пассивный элемент с третьим входом генератора ступенчатого сигнала, выход операционного усилителя соединен со вторым выходом генератора ступенчатого сигнала и с соответствующим выводом первого резистора, соответствующий вывод последнего резистора соединен через второй пассивный элемент со-, входом операционного усилителя, а через третий пассивный элемент - с шиной нулевого отенциала, входы второго коммутатора одключены к выходам блока постоянной амяти, второй вход которого соединен с ервым входом генератора ступенчатого игнала. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР b 424165, кл. С 11 С 27/ОО, 1974. 2.Авторское свидетельство СССР O 339961, кл. (5 11 С 27/ОО, 1972 (прототип).

Памлгпь

J.1

BMoS

о

Bxt)a i

CffjffGC

:5Г

o--

fO

CSpoc

Остан

. /

Авторы

Даты

1981-08-23—Публикация

1979-11-05—Подача