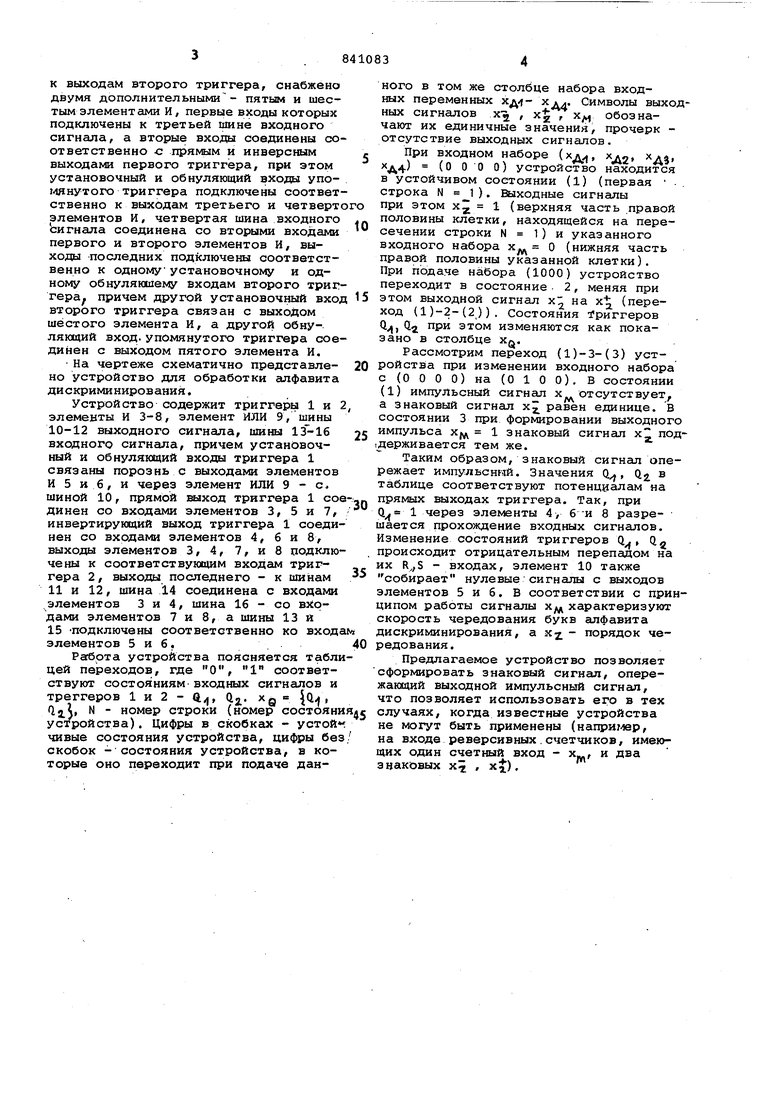

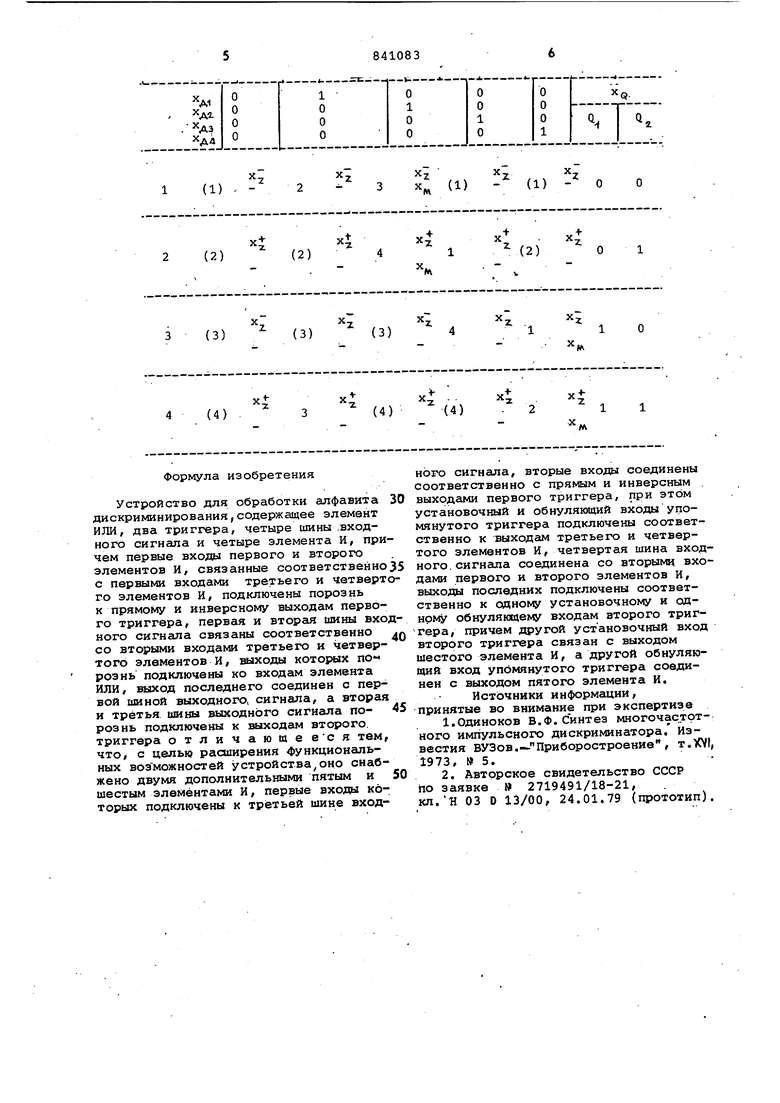

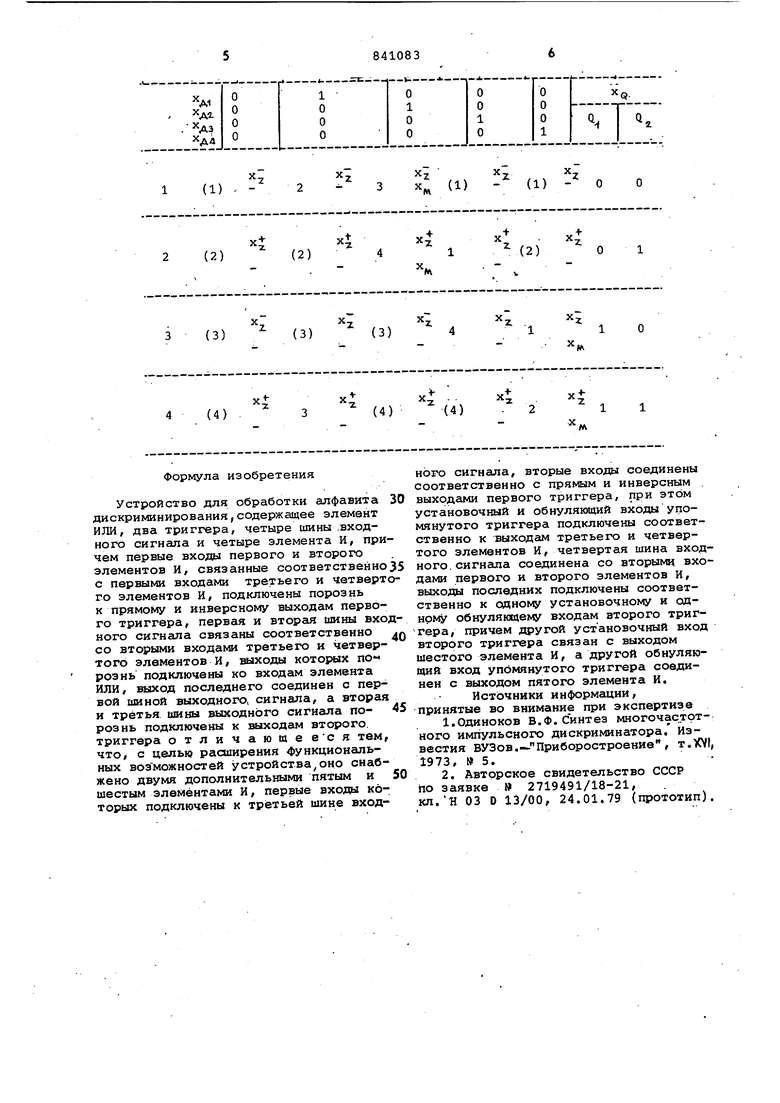

Изобретение относится к дискрет. ным системам автоматики и предназначено для использования в л:огических фазочастотных дискриминаторах. Известно устройство для обработки четырехбуквенного алфавита дискриминирования Хд Хд, хд, Хд, формирующее на выходе две импульс Hue последовательности сигналов / х каждая из которых соответствует порядку (знаку) и скорости чередования входных Сигналов Хд хд4 содер-жащее элементы И и триггеры, и выпол няющее функцию логического дискриминатораНедостатком этого устройства явля ется низкая чувствительность.. Известно также устройство для обработки алфавита дискриминирования содержащее элемент ИЛИ, два триггера четыре шиюи входного сигнала и четыре элемента И, причем первые входы первого и второго элементов И, связанные соответственно с первыми входами третьего и четвертого элбмен тов И, подклйчены порознь к прямому .и инверсному выходам первого триггера, первая и вторая шины входного сигнала связаны соответственно со вторыми входами третьего и четвертое го элементов И, выходы которых порознь подключены ко входам элемента ИЛИ, выход последнего соединен с первой шиной выходного сигнала, а вторая и третья шины выходного сигнала порознь подключены к -выходaiM второго триггера 2. Недостатком этого устройства являются низкие функциональные возможности. Цель изобретения - расширение функ циональных возможностей устройства. Поставленная цель достигается тем, что устройств-о содержащее элемент. ИЛИ| два триггера, четыре шины входного сигнала ичетыре элемента И, причем первые входы первого и второго элементов И, связанные соотвртственно с перйыми входами третьего и четвертого элементов И, подключены порознь к прямому и инверсному выхояам пер-вого триггера, первая и вторг1Я шины входного сигнала связаны соответственно со вторыми входами тре тьего и четвертого элементов И, выходы которых порознь подключены ко вход еилэлемент а ИЛИ, выход последнего соединен с первой шиной выходного сигнала, а вторая и третья шины выходного сигнала порознь подключены к выходам второго триггера, снабжено двумя дополнительными- пятым и шестым элемент ами И, первые входы которых подключены к третьей шине входного сигнала, а вторые входы соединены соответственно -С прямым и инверсным выходами первого триггера, при этом установочный и обнуляющий входы упо1донутого триггера подключены соответственно к выходам третьего и четверто элементов И, четвертая шина входного сигнала соединена со вторыми входами первого и второго элементов И, выходы последних подключены соответственно к одному установочному и одному обнуляюшему входам второго триггера, причем другой установочный вход второго триггера связан с выходом шестого элемента И, а другой обнуляющий вход, упомянутого триггера соединен с выходом пятого элемента И. На чертеже схематично представлено устройство для обработки алфавита дискриминирования, Устройство содержит триггеры 1 и элементы И 3-8, элемент ИЛИ 9, шины 10-12 выходного сигнала, шины 13-16 входного сигнала, причем установочный и обнуляющий входы триггера 1 связаны порознь с выходами элементов И 5 и б, и через элемент ИЛИ 9 - с шиной 10, прямой выход триггера 1 сое динен со входами элементов 3, 5 и 7, инвертирующий выход триггера 1 соединен со входами элементов 4, 6 и 8, выходы элементов 3,4, 7, и 8 подключены к соответствующим входам триггера 2, выходы последнего - к шинам 11 и 12, шина 14 соединена с входами элементов 3 и 4, шина 16 - со входами элементов 7 и 8, а шины 13 и 15 -подключены соответственно ко вход элементов 5 и б. Работа устройства поясняется табли цей переходов, где О, 1 соответствуют состояниям входных сигналов и треггеров 1 и 2 - ft, Qj,.. g fl, N - номер строки (номер состояни устройства). Цифры в скобках - устой« чивые состояния устройства, цифры бе скобок - состояния устройства, в которые оно переходит при подаче данного в том же столбце набора входных переменных хд-f- хд. Символы выходных сигналов Хд , х , Х; обозначают их единичные значения, прочерк отсутствие выходных сигналов. При входном наборе (хд, . хдз Хд4) - (о 00 0) устройство находится в устойчивом состоянии (1) (первая . строка N J). Выходные сигналы при этом х 1 (верхняя часть правой половины клетки, находящейся на пересечении строки N 1) и указанного входного набора х О (нижняя часть правой половины указанной клетки). При подаче набора (1000) устройство переходит в состояние 2, меняя при этом выходной сигнал х на х (переход (1)-2-(2)). Состояния т риггеров Л1 этом изменяются как показано в столбце XQ. Рассмотрим переход (1)-3-(3) устройства при изменении входного набора с (0000) на (0100). В состоянии (1) импульсный сигнал х отсутствует, а знаковый сигнал х равен единице. В состоянии 3 при формировании выходного импульса Xff 1 знаковый сигнал х поддерживается тем же. Таким образом, знаковый сигнал опережает импульсный. Значения Q, Q в таблице соответствуют потенциалам на прямых выходах триггера. Так, при 1 через элементы 4, б и 8 разре- шается прохождение входных сигналов. Изменение состояний триггеров Q., Qg происходит отрицательным перепадом на их R,,S - входах, элемент 10 также собирает нулевые сигналы с выходов элементов 5 и 6. В соответствии с принципом работы сигналы Хдд характеризуют скорость чередования букв алфавита дискриминирования, а х - порядок чередования. Предлагаемое устройство позволяет сформировать знаковый сигнал, опережающий выходной импульсный сигнал, что позволяет использовать его в тех случаях, когда известные устройства не могут быть применены (наприг-юр, на входе реверсивных.счетчиков, имеющих один счетный вход - х., и два знаковых х , х).

(3)

(3)

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обработки алфавита дискриминирования | 1979 |

|

SU873383A1 |

| Дискриминатор прямой и обратной последовательностей импульсов | 1983 |

|

SU1140225A1 |

| Устройство для обработки вторичногоАлфАВиТА | 1979 |

|

SU853774A1 |

| Автомат обработки вторичного алфавита | 1982 |

|

SU1058024A1 |

| Автомат обработки алфавита дискриминирования | 1979 |

|

SU783949A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием напряжения в частоту импульсов | 1985 |

|

SU1305856A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕЙ НАРАБОТКИ НА ПОЛНЫЙ ОТКАЗ СТРУКТУРНО-СЛОЖНОЙ СИСТЕМЫ | 1992 |

|

RU2041493C1 |

| Устройство для автоматического определения динамических характеристик аналого-цифровых преобразователей | 1985 |

|

SU1288909A1 |

| Цифровой экстраполятор | 1979 |

|

SU817727A1 |

| Параболический интерполятор | 1984 |

|

SU1231512A1 |

Формула изобретения

Устройство для обработки алфавита 30 дискриминирования,содержащее элемент ИЛИ, два триггера, четыре шины .входного сигнала и четыре элемента И, причем первые входы первого и второго элементов И, связанные соответственно35 с первыми входами третьего и четвертого элементов И, подключены порознь к прямому и инверсному выходам первого триггера, первая и вторая шины входного сигнала связаны соответственно д со вторыми входами третьего и четвертого элементов И, выходы которых по рознь подключены ко входам элемента ИЛИ, выход последнего соединен с первой шиной выходного, сигнала, а вторая и третья шины выходного сигнала по- 45 рознь подключены к шходам второго, триггера отличающеес я тем, что, с целью расширения функциональных возможностей устройства,оно снабжено двумя дополнительными пятым и 50 шестым элементами И, первые входы которых подключены к тр1етьей шине входного сигнала, вторые входы соединены соответственно с прямым и инверсным выходами первого триггера, при этом установочный и обнуляющий входы упомянутого триггера подключены соответственно к выходам третьего и четвертого элементов И, четвертая шина входного, сигнала соединена со вторыми входами первого и второго элементов и, выходы последних подключены соответственно к одному установочному и одному обнуляющему входам второго триг гера, причем другой установочный вход второго триггера связан с выходом шестого элемента И, а другой обнуляющий вход упомянутого триггера соединен с выходом пятого элемента И.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-06-23—Публикация

1979-09-20—Подача