Изобретение относится к вычислительной технике, а именно к устройствам для анализа и прогнозирования надежности сложных систем.

Известно устройство [1] для определения показателей надежности объектов, содержащее счетчик состояний, дешифратор, группы элементов И, элемент ИЛИ-НЕ и ряд других вспомогательных элементов, а также блок ассоциативной памяти, информационные выходы которого подключены к установочным входам счетчика состояний, счетные выходы которого соединены с информационными входами блока ассоциативной памяти, ассоциативные выходы которого через группу элементов И и элемент ИЛИ-НЕ подключены к входу разрешения дешифратора, основные входы которого подключены к счетным выходам счетчика состояний. В исходном состоянии модель системы надежности заносится в блок ассоциативной памяти. Счетчик состояний формирует на счетных выходах последовательность кодов путем перебора всех комбинаций 1 и 0 только в тех разрядах, в которые на установочные входы счетчика с блока ассоциативной памяти подаются нулевые сигналы. Таким образом осуществляется перебор заведомо работоспособных состояний, которые в дальнейшем используются для оценки значений вероятностных показателей стpуктурной надежности системы.

Недостатком устройства является невозможность вычисления значений временных показателей надежности структурно-сложной системы, а именно средней наработки на полный отказ (Тs).

Наиболее близким к изобретению является устройство [2] для определения работоспособных состояний структурно-сложной системы, содержащее счетчик состояний, формирователь сигналов сброса, первый и второй узлы сравнения, блок памяти, коммутатор, четыре элемента И, элемент ИЛИ/ИЛИ-НЕ, элемент ИЛИ, два элемента задержки и триггер, инверсный выход которого соединен с первыми входами третьего и четвертого элементов И, а первый установочный вход связан с первым входом элемента ИЛИ и является входом начала работы устройства, инверсный выход элемента ИЛИ/ИЛИ-НЕ является выходом остановки устройства, прямой выход соединен с первым входом первого элемента И, а его группа входов и первые группы входов первого и второго узлов сравнения связаны с группой информационных выходов счетчика состояний, вторые группы входов первого и второго узлов сравнения подключены к группе выходов блока памяти, а их выходы соединены соответственно с вторым и первым входами коммутатора, третий вход которого является режимным входом устройства, а выход подключен к первому входу второго элемента И и входу формирователя сигналов сброса, группа входов выходов последнего соединена с группой управляющих входов-выходов счетчика состояний, счетный вычитающий вход которого подключен к выходу первого элемента И. В исходном состоянии выбранная модель надежности (в виде кодов максимальных сечений отказов или минимальных путей работоспособности) заносится в блок памяти, а в n младших разрядов счетчика состояний записываются единицы. Работа устройства состоит в формировании на счетчике состояний двоичных чисел, отображающих коды возможных состояний системы, исключении с помощью формирователя сигналов сброса формирования и анализа части неработоспособных состояний, а также в отборе с помощью первого или второго узла сравнения (в зависимости от типа выбранной модели надежности) кодов работоспособных состояний. Таким образом в результате выполнения каждого цикла работы устройства на счетчике состояний формируется код работоспособного состояния системы, а на выходе второго элемента И сигнал, разрешающий дальнейший анализ кода для оценки показателей надежности системы.

Недостатком этого устройства является его ограниченные функциональные возможности, а именно невозможность вычисления значения средней наработки на полный отказ системы.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения возможности вычисления значения средней наработки на полный отказ структурно-сложной системы.

Поставленная цель достигается тем, что в устройство, содержащее счетчик состояний, формирователь сигналов сброса, первый и второй узлы сравнения, первый блок памяти, коммутатор, четыре элемента И, первый элемент ИЛИ/ИЛИ-НЕ, первый элемент ИЛИ, два элемента задержки и триггер, инверсный выход которого соединен с первыми входами третьего и четвертого элементов И, а первый установочный вход связан с первым входом первого элемента ИЛИ и является входом начала работы устройства, выход четвертого элемента И подключен к второму входу второго элемента И и входу первого элемента задержки, выход которого соединен со вторым входом третьего элемента И, выход которого подключен к второму входу первого элемента И и входу второго элемента задержки, выход которого соединен со вторым входом первого элемента ИЛИ, выход которого подключен к второму входу четвертого элемента И, выход второго элемента И соединен с вторым установочным входом триггера, инверсный выход элемента ИЛИ/ИЛИ-НЕ является выходом остановки устройства, прямой выход соединен с первым входом первого элемента И, а его группа входов и первые группы входов первого и второго узлов сравнения связаны с группой информационных выходов счетчика состояний, вторые группы входов первого и второго узлов сравнения подключены к группе выходов первого блока памяти, а их выходы соединены соответственно с вторым и первым входами коммутатора, третий вход которого является режимным входом устройства, а выход подключен к первому входу второго элемента И и входу формирователя сигналов сброса, группа входов-выходов последнего соединена с группой управляющих входов-выходов счетчика состояний, счетный вычитающий вход которого подключен к выходу первого элемента И, введены второй блок памяти, счетчик адаптивный, блок у знаковый, счетчик кольцевой, регистр, сумматор, арифметический блок, сумматор-вычитатель, блок элементов И, пятый, шестой, седьмой, восьмой, девятый и десятый элементы И, элемент И/И-НЕ, второй, третий и четвертый элемент ИЛИ, второй и третий элементы ИЛИ/ИЛИ-НЕ, третий, четвертый, пятый и шестой элементы задержки, выход последнего соединен с входом синхронизации сумматора-вычислителя и со вторыми входами пятого и шестого элементов И, первые входы которых подключены соответственно к прямому и инверсному выходу элемента И/И-НЕ, выход пятого элемента И соединен с третьим установочным входом триггера, выход шестого элемента И подключен к второму входу третьего элемента ИЛИ, первый вход которого соединен с выходом второго элемента И, а его выход подключен к счетному вычитающему входу счетчика адаптивного, входу сброса сумматора, первому входу второго элемента ИЛИ и установочному входу блока знакового, знаковый выход которого соединен с режимным входом сумматора-вычитателя, а первая группа его входов и группа управляющих входов счетчика адаптивного соединены с группой информационных выходов счетчика состояний, вторая группа входов блока знакового, первая группа входов блока элементов И и группа входов элемента И/И-НЕ соединены с группой информационных выходов счетчика адаптивного, а третья группа входов блока знакового и вторая группа входов блоков элементов И подключены к группе информационных выходов счетчика кольцевого, второй вход второго элемента ИЛИ соединен с выходом десятого элемента И, а его выход со счетным входом счетчика кольцевого и входом третьего элемента задержки, выход которого подключен к вторым входам седьмого и восьмого элементов И, первые входы которых соединены соответственно с прямым и инверсным выходами второго элемента ИЛИ/ИЛИ-НЕ, группа входов последнего и группа выходов блока элементов И подключены к группе входов второго блока памяти, группа выходов которого соединена с группой входов регистра, а группа выходов последнего подключена к группе информационных входов параметра, выход седьмого элемента И подключен к входу управления считыванием второго блока памяти и входу четвертого элемента задержки, выход которого соединен с входом синхронизации сумматора и первым входом четвертого элемента ИЛИ, второй вход последнего подключен к выходу восьмого элемента И, а его выход соединен с первыми входами девятого и десятого элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам третьего элемента ИЛИ/ИЛИ-НЕ, вход последнего соединен с информационным выходом (n 1)-го разряда счетчика кольцевого, выход девятого элемента И подключен к входу пятого элемента задержки, выход которого соединен с управляющим входом блока арифметического и входом шестого элемента задержки, группа информационных выходов сумматора подключена к группе информационных входов блока арифметического, а группа информационных выходов последнего к группе информационных входов сумматора вычитателя, вход сброса которого соединен с первым установочным входом триггера.

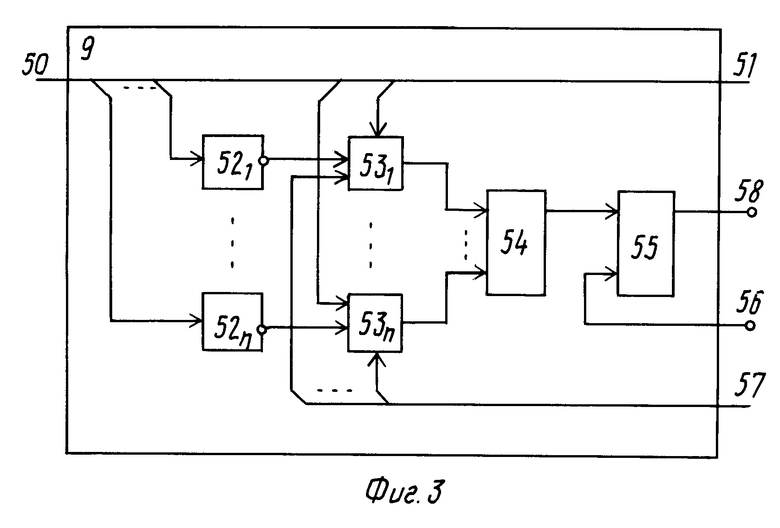

В настоящее время отсутствует методика определения временных показателей структурной надежности, учитывающих возможности выполнения сложной системой своих функций даже при отказах отдельных элементов. В устройстве реализован следующий предлагаемый вероятностный метод определения обобщенного показателя безотказности структурно-сложной системы средней наработки на полный отказ (Тs), использующий в качестве исходных статистические показатели безотказности элементов. Согласно известной методике, значение показателя Тs определяется выражением

TS=  R(t)dt (1) где R(t)- вероятность нахождения системы в состоянии работоспособности.

R(t)dt (1) где R(t)- вероятность нахождения системы в состоянии работоспособности.

Для структурно-сложной системы

R(t)  Wl(t) (2) где Wl(t) вероятность нахождения системы в l-м работоспособном состоянии;

Wl(t) (2) где Wl(t) вероятность нахождения системы в l-м работоспособном состоянии;

L количество работоспособных состояний системы.

Введем двоичную матрицу Х размером L x N (где N количество элементов в системе), каждая строка которой является кодом одного из работоспособных состояний системы. Тогда

Wl(t) (Pn(t)xl,n+(1-Pn(t))(1-xln)) (3) где Рn(t) вероятность безотказной работы n-го элемента системы.

(Pn(t)xl,n+(1-Pn(t))(1-xln)) (3) где Рn(t) вероятность безотказной работы n-го элемента системы.

После подстановки в (1) выражений (2) и (3) и вынесении суммы за знак интеграла для экспоненциальных законов распределения Рn(t) получаем

Ts=

(e

(e xln+(1-e

xln+(1-e )(1-xln))dt

)(1-xln))dt  Al (4)

Al (4)

В результате проведенного анализа выражения Аl выявлена следующая закономерность в его формировании:

Al=

ρm (5) где Мl 2rl количество частных сумм, соответствующих l-му состоянию системы;

ρm (5) где Мl 2rl количество частных сумм, соответствующих l-му состоянию системы;

rl= (1-xln) класс кода l-го состояния системы;

(1-xln) класс кода l-го состояния системы;

Yl [ymn] двоичная матрица кодов частых сумм, соответствующих l-му состоянию системы;

ρm= (-1) величина, характеризу- ющая арифметический знак m-ой частной суммы;

величина, характеризу- ющая арифметический знак m-ой частной суммы; (1-y

(1-y

Первая строка матрицы Yl совпадает с кодом l-го состояния системы, а каждая последующая отличается двоичной комбинацией "1" и "0" в нулевых разрядах кода l-го состояния системы. Соответственно все разряды кода последней (Мl-й) частной суммы равны единице.

Таким образом с учетом (4) и (5) окончательное выражение имеет вид

TS=

ρm (6)

ρm (6)

Формирование матрицы кодов частных сумм осуществляется с помощью счетчика адаптивного, содержащего группу из n-триггеров разрядов, первую, вторую и третью группу соответственно из (n 1), n и (n 1) элементов И и группу из n-элементов ИЛИ-НЕ, входы которых являются группой управляющих входов счетчика адаптивного и соединены, кроме входа n-го элемента ИЛИ-НЕ, со вторыми входами соответствующих элементов И третьей группы, первые входы последних соединены с первыми входами соответствующих элементов И второй группы, вторые входы которых подключены к выходам соответствующих элементов ИЛИ-НЕ, а их выходы соединены с установочными входами соответствующих триггеров разрядов, прямые выходы триггеров разрядов образуют группу информационных выходов счетчика адаптивного, а их инверсные выходы, кроме триггера (n 1)-го разряда, соединены со вторыми входами соответствующих элементов И первой группы, первые входы которых подключен к выходам соответствующих элементов И третьей группы, а их выходы соединены с первыми входами соответствующих, начиная со второго, элементов И второй группы, первый вход первого элемента И второй группы является счетным входом счетчика адаптивного.

Арифметический знак каждой частной суммы определяется с помощью блока знакового, содержащего n-го элементов ИЛИ-НЕ, n-элементов И, элемент ИЛИ и триггер, прямой выход которого является знаковым выходом блока, а установочный вход соединен с выходом элемента ИЛИ, каждый из n-входов последнего подключен к выходу соответствующего элемента И, группы вторых и третьих входов элементов И образуют соответственно вторую и третью группы входов блока знакового, а первый вход каждого элемента И соединен с выходом соответствующего элемента ИЛИ-НЕ, входы элементов ИЛИ-НЕ образуют первую группу входов блока знакового.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается более широкими функциональными возможностями, а именно обеспечением вычисления значения средней наработки на полный отказ структурно-сложной системы. Таким образом, заявляемое устройство соответствует критерию "новизна". В результате сравнения заявляемого решения не только с прототипом, но и с другими техническими решениями в данной области техники, в них не выявлены признаки, отличающие заявляемое решение от прототипа. Это позволяет сделать вывод о соответствии заявляемого решения критерию "существенные отличия".

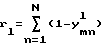

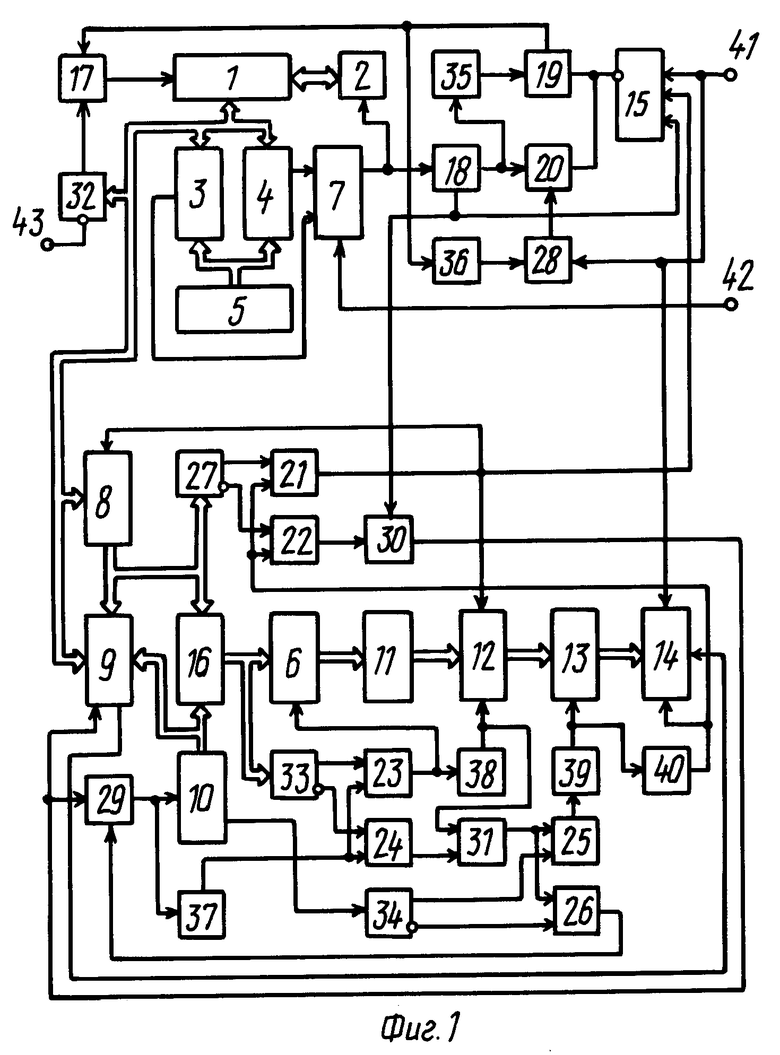

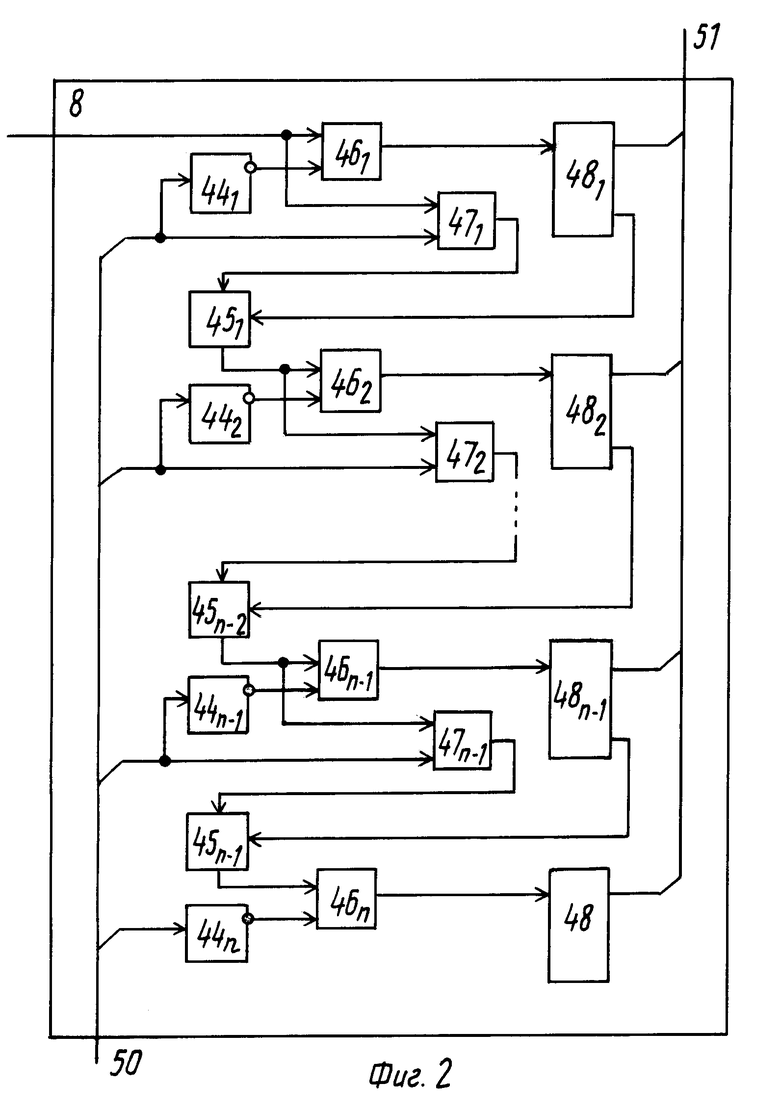

На фиг. 1 представлена структурная схема устройства; на фиг. 2 схема счетчика адаптивного; на фиг. 3 схема блока знакового.

Устройство (фиг. 1) содержит счетчик 1 состояний, формирователь сигналов сброса 2, первый 3 и второй 4 узлы сравнения, блок памяти кодов модели системы 5 и блок 6 памяти интенсивностей отказов, коммутатор 7, счетчик 8 адаптивный, блок 9 знаковый, счетчик 10 кольцевой, регистр 11, сумматор 12, блок 13 арифметический, сумматор-вычислитель 14, триггер 15, блок 16 элементов И, первый 17, второй 18, третий 19, четвертый 20, шестой 21, седьмой 22, восьмой 23, девятый 24, десятый 25 и одиннадцатый 26 элементы И, пятый элемент 27 И, первый 28, четвертый 29, третий 30 и шестой 31 элементы ИЛИ, второй 32, пятый 33 и седьмой 34 элементы ИЛИ, первый 35, второй 36, третий 37, четвертый 38, шестой 39 и пятый 40 элементы задержки. На схеме обозначены установочный вход 41, режимный вход 42 и выход 43 остановки.

Счетчик 8 адаптивный (фиг. 2) содержит группу 441-44n элементов ИЛИ-НЕ, первую группу 451-45n-1, вторую группу 461-46n и третью группу 471-47n-1 элементов И, а также группу 481-48n триггеров разрядов. На схеме обозначены вычитающий счетный 49 вход, входная шина кодов состояний и выходная 51 шина кодов частных сумм.

Блок 9 знаковый (фиг. 3) содержит группу 521-52n элементов ИЛИ-НЕ, группу 531-53n элементов И, элемент 54 ИЛИ и триггер 55. На схеме обозначены вход 56 установки нулевого состояния, кодовая входная 57 шина и знаковый 58 выход.

Работа устройства в целом состоит в формировании на выходе счетчика 1 состояний с помощью формирователя сигналов сброса 2 двоичных чисел, отображающих коды работоспособных и части неработоспособных состояний исследуемой системы, выдачи с первого 3 или второго 4 узлов сравнения (в зависимости от типа выбранной модели надежности системы) сигналов разрешения считывания кодов работоспособных состояний, формировании на выходе счетчика 8 адаптивного двоичных чисел, отображающих коды частных сумм, соответствующих анализируемому состоянию системы, выделении с помощью счетчика 10 кольцевого и блоков 16 элементов И единиц номеров элементов, входящих в код данной частной суммы, выборе в соответствии с данными номерами из второго 6 блока памяти значений интенсивностей отказов, слежении их в сумматоре 12, вычислении обратных величин частных сумм в арифметическом 13 блоке определении с помощью знакового 9 блока арифметических знаков частных сумм и суммировании последних в сумматоре-вычитателе 14.

В исходном состоянии в n младших разрядов счетчика 1 состояний и счетчика 8 адаптивного записываются единицы, а в счетчик 10 кольцевой нули. Кроме того во второй блок 6 памяти заносятся интенсивности отказов элементов, а в первый блок 5 памяти модель надежности системы (в виде минимальных путей работоспособности или минимальных сечений отказов), в зависимости от типа которой задается режим работы коммутатора 7. Сигнал начала работы устройства поступает на вход 41, устанавливает в нулевое состояние триггер 15 сумматор-вычитатель 14 и проходит на вход элемента ИЛИ 28. С выхода элемента ИЛИ 28 сигнал проходит через открытый потенциалом с выхода триггера 15 элемент И 20, поступает на вход элемента И 18 и с задержкой на элементе 35 (время задержки должно быть больше суммы времени переходных процессов счетчика 1 состояний и формирователя сигналов сброса 2) поступает на вход элемента И 19. Это необходимо для обеспечения следующих действий.

Если сформированное счетчиком 1 состояний число соответствует коду работоспособного состояния системы, то на выходе коммутатора 7 формируется единичный потенциал (N). Тогда сигнал с выхода элемента И 20 проходит через открытый этим потенциалом элемент И 18 и перебрасывает триггер 15 в единичное состояние, чем обеспечивается запрет прохождения задержанного на элементе 35 сигнала через элемент И 19. Если же число на выходе счетчика 1 состояний соответствует коду неработоспособного состояния, то на выходе коммутатора 7 формируется нулевой потенциал, чем включается формирователь сигналов сброса 2, который обнуляет триггеры разрядов cчетчика 1 cоcтояний, начиная с младшего, до первого разряда, имеющего нулевое значение. Этим осуществляется переключение счетчика 1 состояний на число, соответствующее коду последнего из выявленной группы неработоспособных состояний. Кроме того, нулевой потенциал с выхода коммутатора 7 закрывает элемент И 18. Тогда сигнал с выхода элемента И 20, задержанный на элементе 35, проходит элемент И 19, так как триггер 15 находится в нулевом состоянии, поступает через открытый элемент И 17 на вычитающий счетный вход счетчика 1 состояний, уменьшая на единицу записанное в нем число и формируя тем самым новый код состояния системы. Этот же сигнал, задержанный на элементе 36 (время задержки должно быть больше суммарного времени переходных процессов счетчика 1 состояний, первого 3 узла сравнения и коммутатора 6), проходит через открытый элемент ИЛИ 28, открытый элемент И 20 и выполняет описанные действия, т.е. проходит на элемент И 18, если код состояния окажется работоспособным, или на выход элемента И 19 и далее на формирование кода нового состояния. Этот процесс заканчивается тогда, когда счетчик 1 состояний окажется в нулевом состоянии, чем будут обеспечены выдача на выход 43 сигнала остановки и запрещении инверсным ему сигналом прохождения импульса через элемент И 17 на вычитающий счетный вход счетчика 1 состояний.

Таким образом, работа данной части устройства обеспечивает формирование кодов работоспособных состояний системы, после каждого из которых на выходе элемента И 18 появляется единичный сигнал. Этот сигнал временно приостанавливает процесс формирования очередного работоспособного состояния путем перевода триггера 15 в единичное состояние, а затем обеспечивает выполнение следующих действий. Проходит через ИЛИ 30 и с его выхода поступает на сумматор 12 и обнуляет его, проходит через элемент ИЛИ 29 на счетный вход счетчика 10 кольцевого и на вход элемента задержки 37, поступает на знаковый 9 блок и устанавливает его в нулевое состояние. Кроме этого, сигнал с выхода элемента И 30 поступает на счетный вычитающий вход счетчика 8 адаптивного, чем обеспечивает, совместно с поступающим на счетчик 8 кольцевой кодом анализируемого состояния системы, формирование кода первой частной суммы, соответствующей этому состоянию системы. Код данной суммы поступает на элемент И/И-НЕ 27, знаковый 9 блок и блок 16 элементов И. На знаковый 9 блок кроме этого поступают код анализируемого состояния системы от счетчика 1 состоянии и сигналы разрядов счетчика 10 кольцевого. В результате их совместной обработки на выходе блока 9 знакового вырабатывается сигнал, описывающий арифметический знак частной суммы, соответствующей данному состоянию системы. Этот сигнал в виде единичного потенциала (если знак частной суммы отрицательный) или в виде нулевого потенциала (если знак частной суммы положительный) поступает на режимный вход сумматора-вычитателя 14.

На вторую группу входов блока 16 элементов И поступают также сигналы разрядов счетчика 10 кольцевого. В результате поступления с выхода элемента ИЛИ 29 единичного потенциала на счетный вход счетчика 10 кольцевого на его выходе в нулевом разряде формируется единичный потенциал. Если нулевой разряд кода анализируемой частной суммы равен единице, то в первом разряде кода на выходе блока 16 элементов И будет сформирован единичный потенциал, который поступит на соответствующий регистр второго блока 6 памяти, а также с помощью элемента ИЛИ/ИЛИ-НЕ 33 открыт элемент И 23 и закрыт элемент И 24. В результате этого единичный потенциал с выхода элемента задержки 37 (время задержки должно быть больше суммарного времени переходных процессов счетчика 10 кольцевого, блока 16 элементов И и элемента ИЛИ/ИЛИ-НЕ 33) пройдет через открытый элемент И 23 на вход разрешения считывания блока 6 памяти, обеспечив тем самым считывание значений интенсивности отказов первого элемента системы в регистр 11, а также поступит на вход элемента задержки 38. С выхода элемента задержки 38 (время задержки должно быть больше времени считывания значений интенсивностей отказов в регистр 11) сигнал проходит на синхронизирующий вход сумматора 12, чем обеспечивается сложение его содержимого с содержимым регистра 11, и поступает на первый вход элемента ИЛИ 31.

Если же первый разряд кода анализируемой частной суммы равен нулю, то значения всех разрядов кода на выходе блока 16 элементов И будут равны нулю, а значит под действием сигнала с элемента ИЛИ/ИЛИ-НЕ 33 элемент И 23 будет закрыт, а элемент И 24 открыт. В результате этого единичный потенциал с выхода элемента задержки 37 через открытый элемент И 24 поступит на второй вход элемента ИЛИ 31. Сигнал с выхода элемента ИЛИ 31 подается на первые входы элементов И 25 и И 26, на вторые входы которых через элемент ИЛИ/ИЛИ-НЕ 34 поступают соответственно прямой и инверсный ему сигналы (n 1)-го разряда счетчика 10 кольцевого. Так как на данном шаге значение n-го разряда счетчика 10 кольцевого равно нулю, то этот сигнал откроет элемент И 26 и закроет элемент И 25. Тогда сигнал с выхода элемента ИЛИ 31 через открытый элемент И 26 поступит на элемент ИЛИ 29, а через него на счетный вход счетчика 10 кольцевого, чем обеспечит формирование на его выходе единичного сигнала в первом разряде и обнуление нулевого разряда (в результате этого начинается выполнение вышеописанных действий). Когда на выходе счетчика 10 кольцевого формируется единичный потенциал в (n 1)-ом разряде (что соответствует началу анализа последнего разряда кода частной суммы), то под его действием откроется элемент И 25 и закроется элемент И 26. Тогда сигнал с элемента ИЛИ 31 через открытый элемент И 25 поступит на вход элемента задержки 39 (время задержки должно быть больше времени переходных процессов сумматора 12), а с его выхода на элемент задержки 40 и на вход синхронизации блока 13 арифметического. В результате блок 13 арифметический произведет вычисление обратной величины частной суммы, значение которой получено в сумматоре 12. С выхода элемента задержки 40 (время задержки должно быть больше времени переходных процессов блока 13 арифметического) сигнал поступает на вход синхронизации сумматора-вычитателя 14. В результате этого обеспечивается суммирование содержимого сумматора-вычитателя 14 с содержимым выходного регистра блока 13 арифметического. Знак обратной величины частной суммы к моменту суммирования определен в блоке 9 знаковым и в виде единичного или нулевого потенциала поступает на режимный вход сумматора вычитателя 14.

Сигнал с выхода элемента задержки 40 также поступает на вторые входы элементов И 21 и И 22. Первый вход элемента И 21 подключен к прямому выходу элемента И/И-НЕ 27, а первый вход элемента И 27 к инверсному выходу элемента И/И-НЕ 27. Если на вход элемента И/И-НЕ 27 с выхода счетчика 8 адаптивного поступит код, все разряды которого равны единице (что соответствует коду последней частной суммы для анализируемого состояния системы), то под действием сигнала с выхода элемента И/И-НЕ 27 элемент И 21 откроется, а элемент И 22 закроется. Тогда сигнал с выхода элемента задержки 40 пройдет через открытый элемент И 21 на вход триггера 15 и установит его в нулевое состояние, в результате чего начнется работа устройства по формированию очередного работоспособного состояния исследуемой системы. Если же на вход элемента И/И-НЕ 27 с выхода счетчика 8 адаптивного поступают коды очередных частных сумм, соответствующих анализируемому состоянию системы, то под действием сигнала с выхода элемента И/И-НЕ 27 элемент И 21 будет закрыт, а элемент И 22 открыт. Тогда сигнал с выхода элемента задержки 40 пройдет через открытый элемент И 22 на вход элемента ИЛИ 30, а с его выхода обеспечит выполнение описанных выше действий к формированию кодов и вычислению частных сумм, соответствующих анализируемому состоянию системы. Работа устройства заканчивается тогда, когда счетчик 1 состояний окажется в нулевом состоянии, чем будет обеспечена выдача на выход 43 сигнала остановки и запрещения инверсным ему сигналом прохождения импульса через элемент И 17 на всасывающий счетный вход счетчика 1 состояний. После прекращения работы устройства окончательный результат вычисления средней наработки на полный отказ исследуемой системы находится в сумматоре-вычитателе 14.

Счетчик 8 адаптивный (фиг. 2) работает следующим образом. Перед началом формирования кодов частных сумм, соответствующих поступающему на входную шину 50 коду работоспособного состояния системы, все триггеры 482-48n разрядов находятся в исходном (единичном) состоянии. Значения от нулевого до (n 2)-го разрядов кода состояния системы поступают соответственно на вторые входы элементов И 471-47n-1, кроме того значения от нулевого до (n 1)-го разрядов проходят соответственно через элементы ИЛИ-НЕ 441-ИЛИ-НЕ 44n на вторые входы элементов И 461-И 46n. Значит, если значение К-го разряда кода состояния системы равно единице, то соответствующий элемент И 46К+1 будет закрыт, а элемент И 47К+1 открыт. Благодаря этому счетный импульс с вычитающего счетного входа 49 или с инверсного выхода триггера предшествующего разряда не поступит на счетный вход триггера 48К+1, а пройдет через открытый элемент И 47К+1 и элемент ИЛИ 45К+1 на первые входы элементов И 46К+2 и И 47К+2. Если же значение К-го разряда кода состояния системы равно нулю, то счетный импульс пройдет через открытый элемент И 46К+1 на установочный вход триггера 48К+1 и изменит его состояние на противоположное, а потенциал с инверсного выхода триггера 48К+1 поступит через элемент ИЛИ 45К на первые входы элементов И 45К+2 и И 47К+2. Таким образом, под действием счетного импульса на вычитающем счетном входе 49 будет изменяться состояние триггеров только тех разрядов, значения которых в коде состояний системы равно нулю. Этим самым осуществляется перебор всех возможных состояний триггеров данных разрядов, что соответствует формированию на выходной шине 51 кодов частных сумм для поступившего на шину 50 кода состояния системы. При подаче на шину 50 кода первого работоспособного состояния системы, в котором значения всех разрядов равны единице, счетный импульс со входа 49 не изменит состояния ни одного триггера 481-48n, а на выходе 51 будет код единственной частной суммы, соответствующей данному состоянию системы, с единицами во всех разрядах. При формировании группы кодов частных сумм, соответствующих анализируемому состоянию системы, код предпоследней частной суммы будет совпадать с кодом данного состояния системы, а код последней будет состоять из единиц во всех разрядах. После этого на шину 50 поступает код очередного состояния системы и под действием счетных импульсов со входа 49 начнется формирование кодов соответствующих ему частных сумм.

Блок 9 знаковый (фиг. 3) работает следующим образом. Так как знак частной суммы, соответствующей анализируемому состоянию системы, будет положительным, если разность класса ее кода (количества нулевых разрядов в коде) и класса кода состояния системы является четным числом, и отрицательной, если нечетным, то основной функцией блока 9 знакового является определение четности или нечетности общего количества несовпадений значений соответствующих разрядов данных кодов. Для ее осуществления код состояния системы поступает на шину 50, а инверсные значения его разрядов через элементы ИЛИ-НЕ 521-ИЛИ-НЕ 52n подаются на первые входы соответственно элементов И 531-И 53n. На вторые входы элементов И 531-И 53n поступают со входа 51 значения соответствующих разрядов кода анализируемой частной суммы, а на третьи входы через входную шину 57 значения разрядов счетчика 10 кольцевого. Выходные сигналы элементов И 531-И 53n поступают через элемент ИЛИ 54 на установочный вход триггера 55. Исходное состояние триггера 55 (нулевое) устанавливается перед началом определения знака очередной частной суммы сигналом, поступающим на вход 56 с элемента ИЛИ 30 (фиг. 1). От счетчика 10 кольцевого поступают единичные потенциалы поочередно в каждом из разрядов. При неравенстве значений К-го разряда кодов состояния системы и частной суммы и поступлении на элемент И 53К+1 единичного потенциала от счетчика 10 кольцевого, на выходе элемента И 53К+1 будет сформирован единичный сигнал, который через элемент ИЛИ 54 пройдет на установочный вход триггера 55 и переключит его в единичное состояние. В случае повторения такой ситуации второй раз триггер 55 будет переключен в нулевое состояние, третий раз в единичное состояние и т. д. Таким образом, если после поступления единичного сигнала с последнего (n-го) разряда счетчика 10 кольцевого на выходе 58 будет единичный потенциал, то анализируемая частная сумма имеет отрицательный знак, а если нулевой положительный знак.

Технико-экономический эффект от применения предлагаемого изобретения заключается в обеспечении возможности вычисления обобщенного временного показателя безотказности структурно-сложной системы средней наработки на полный отказ, что дает возможность анализировать и прогнозировать безотказность сложной системы с учетом ее структурной и функциональной избыточности.

П р и м е р. Пусть для всех элементов системы, представленной мостиковой схемой, содержащей пять элементов с третьим элементом в диагонале, средняя наработка на отказ Тс 100 ч. Тогда средняя наработка системы на отказ любого элемента равна 20 ч. Предлагаемое устройство позволяет, используя формулу (6), получить среднюю наработку на полный отказ системы Т 81,7 ч. Как видно, второй показатель более полно отражает заложенные в структуру системы возможности по безотказности ее работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения работоспособных состояний структурно-сложной системы | 1990 |

|

SU1785003A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для деления | 1986 |

|

SU1325467A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2451328C1 |

| АДАПТИВНОЕ ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2475831C1 |

| Устройство для определения медианы случайного процесса | 1990 |

|

SU1718233A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

Изобретение относится к вычислительной технике, а именно к устройствам для анализа и прогнозирования надежности сложных систем, позволяет расширить функциональные возможности устройства путем обеспечения возможности вычисления значения средней наработки на полый отказ структурно-сложной системы. В устройство введены блок памяти интенсивностей отказов, счетчик адаптивный, блок знаковый, счетчик кольцевой, регистр, сумматор, блок арифметический, сумматор-вычитатель, блок элементов И и другие вспомогательные элементы. Причем знаковый выход блока знакового соединен с режимным входом сумматора-вычитателя, а на первую группу его входов и группу управляющих входов счетчика адаптивного поступает код анализируемого состояния исследуемой системы. Вторая группа входов блока знакового и первая группа входов блока элементов И подключены к группе информационных выходов счетчика адаптивного, а третья группа входов блока знакового и вторая группа входов блока элементов И соединены с группой информационных выходов счетчика кольцевого. Группа выходов блока памяти интенсивностей отказов подключена к группе входов регистра, а группа выходов регистра к группе информационных входов сумматора. Группа информационных выходов сумматора соединена с группой информационных входов блока арифметического, а группа информационных выходов последнего с группой информационных входов сумматора-вычитателя. На счетчике адаптивном в соответствии с кодом анализируемого состояния системы формируются двоичные числа, отображающие коды частных сумм, являющихся слагаемыми при определении значения средней наработки на полный отказ системы. С помощью счетчика кольцевого и блока элементов И в соответствии с единицами в разрядах кода данной частной суммы из блока памяти интенсивностей отказов выбираются значения интенсивностей отказов элементов системы, которые складываются в сумматоре. Полученные в арифметическом блоке обратные величины частных сумм суммируются в сумматоре-вычитателе со знаком, определяемым в блоке знаковом. 2 з.п. ф-лы, 3 ил.

| Устройство для определения работоспособных состояний структурно-сложной системы | 1990 |

|

SU1785003A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-08-09—Публикация

1992-05-15—Подача