112

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам программного управления станками, а также к устройствам ото бражения графической информации на дисплеях или графопостроителях.

Целью изобретения является увеличение точности.

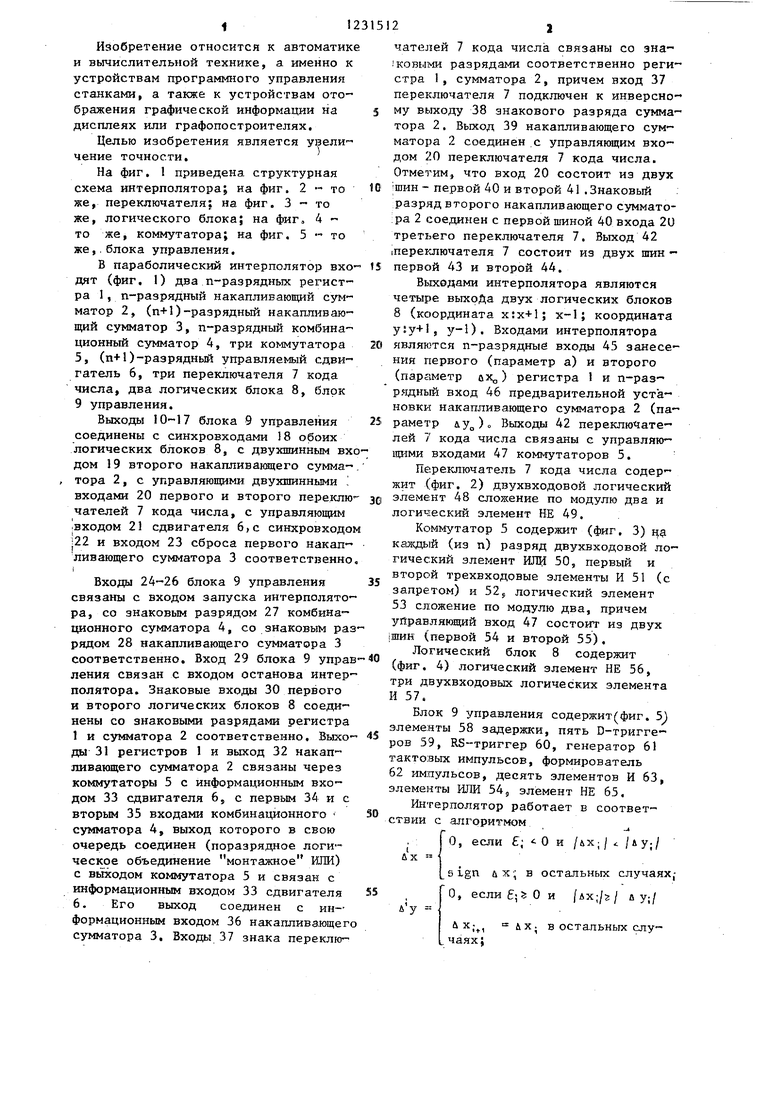

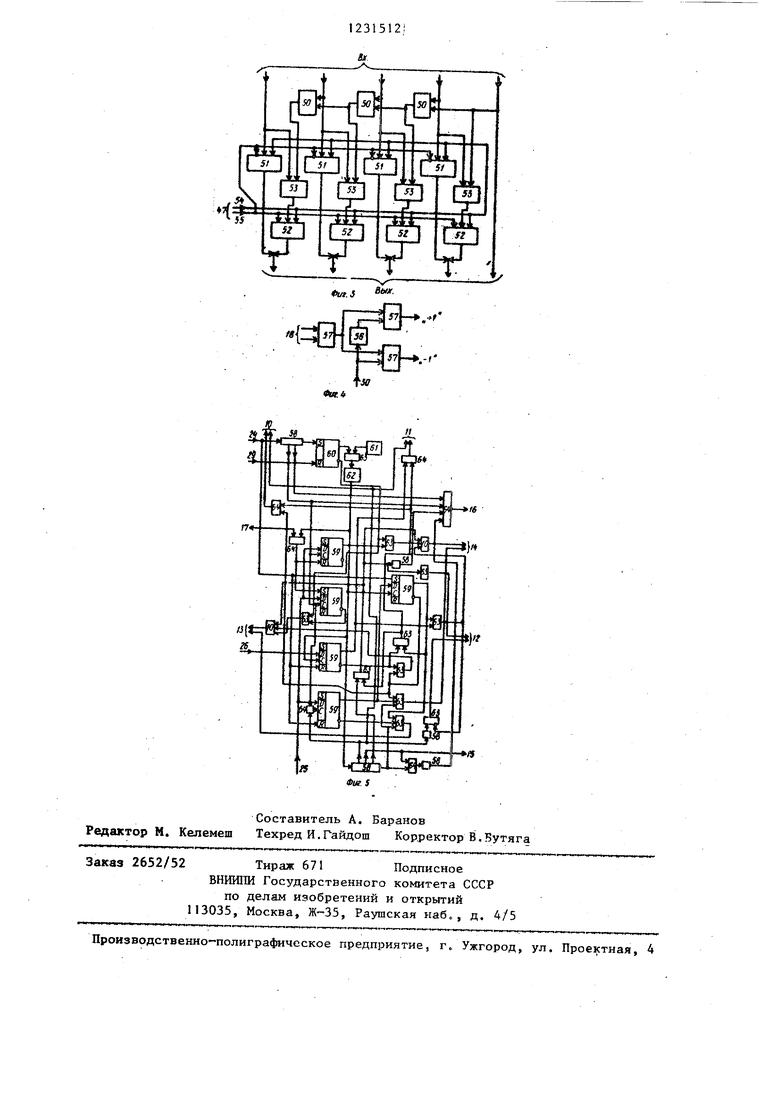

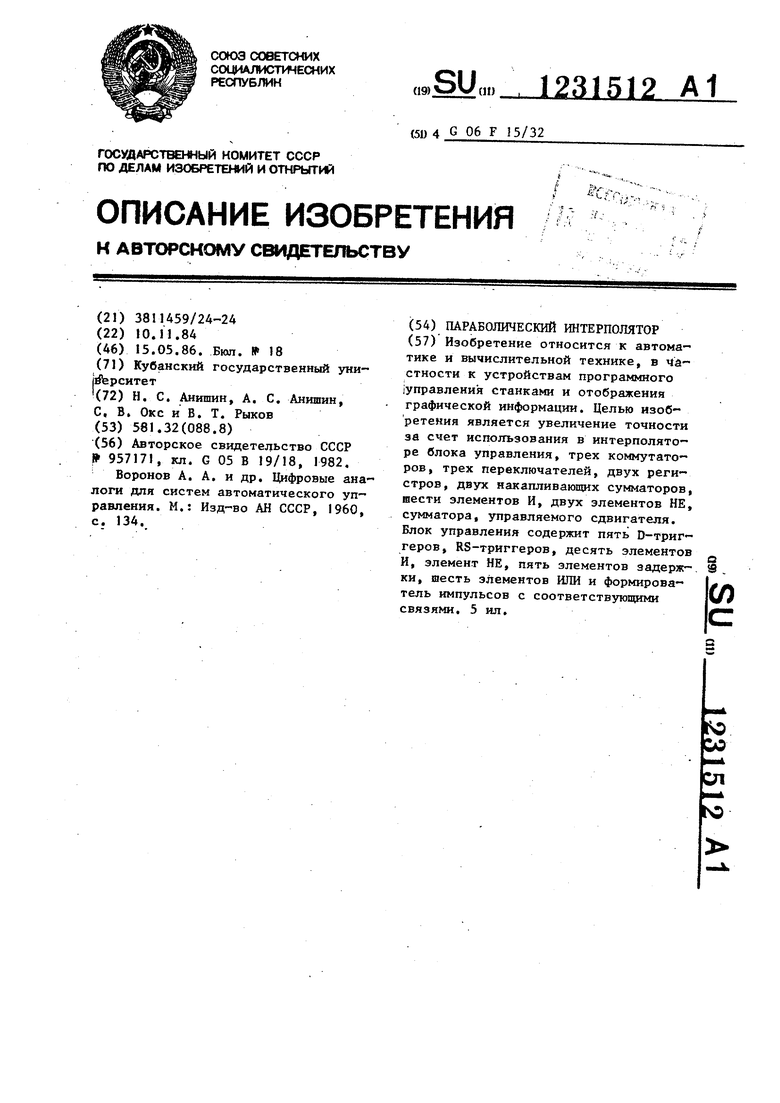

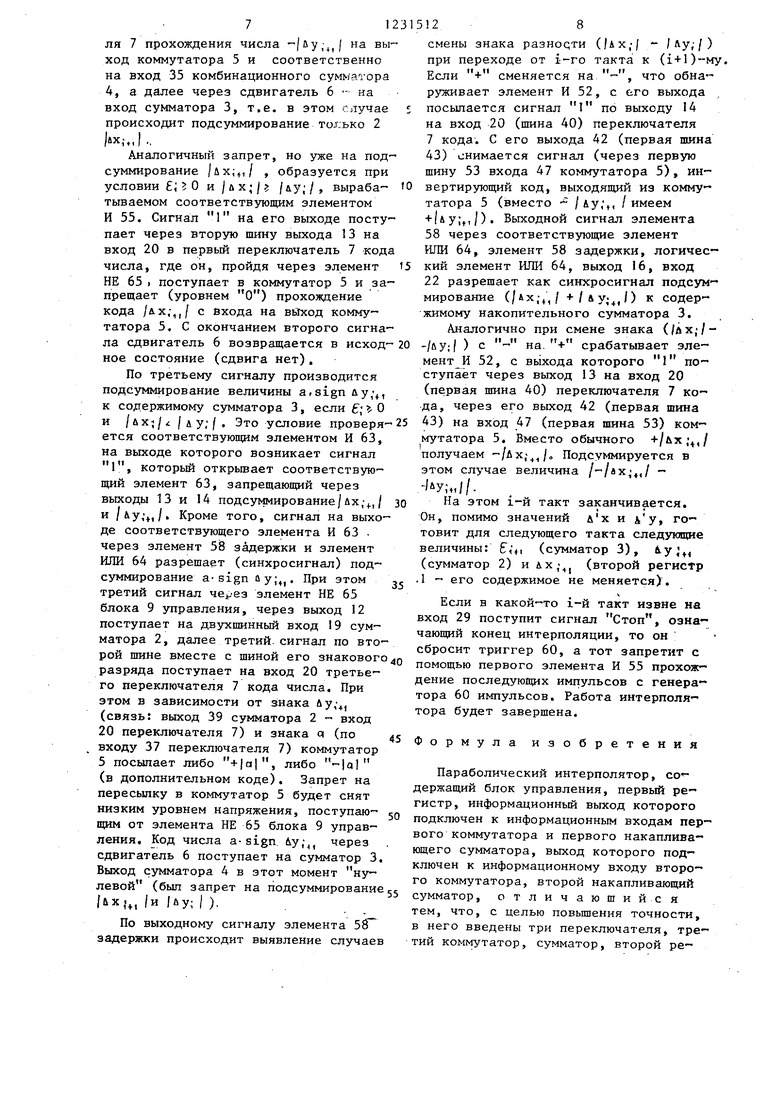

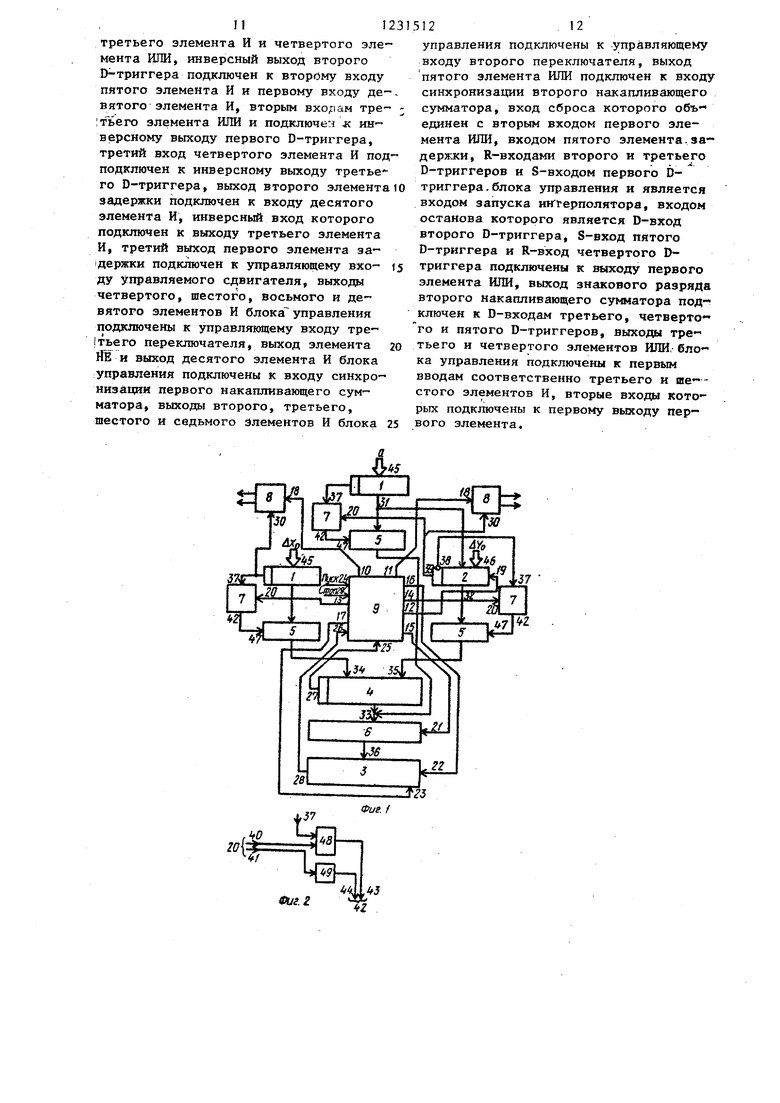

На фиг. 1 приведена структурная схема интерполятора; на фиг. 2 - то же, переключателя; на фиг. 3 - то же, логического блока; на фиг, 4 - то же, коммутатора; на фиг. 5 - то же,.блока управления.

В параболический интерполятор вхо- дят (фиг. 1) два п-разрядных регистра 1, п-разрядный накапливающий cyti матор 2, (п+1)-разрядный накапливающий сумматор 3, п-разрядный комбинационный сумматор 4, три коммутатора

5,(п+1)-разрядный управляемый сдви- гатель 6, три переключателя 7 кода числа, два логических блока 8, блок 9 управления.

Выходы 10-17 блока 9 управления соединены с синхровходами 18 обоих логических блоков 8, с двухшинным входом 19 второго накапливанщего сумматора 2, с управляющими двухшинными входами 20 первого и второго переклю чателей 7 кода числа, с управляющим входом 21 сдвигателя 6,с синхровходом |22 и входом 23 сброса первого накап ливающего сумматора 3 соответственно

I

Входы 24-26 блока 9 управления связаны с входом запуска интерполятора, со знаковым разрядом 27 комбинационного сумматора 4, со знаковым разрядом 28 накапливающего сумматора 3 соответственно. Вход 29 блока 9 управ ления связан с входом останова интерполятора. Знаковые вхо,цы 30 первого и второго логических блоков 8 соединены со знаковыми разрядами регистра 1 и сумматора 2 соответственно. Выхо- ды 31 регистров 1 и выход 32 накапливающего сумматора 2 связаны через коммутаторы 5 с информационным входом 33 сдвигателя 6, с первым 34 и с вторым 35 входами комбинационного сумматора 4, выход которого в свою очередь соединен (поразрядное логическое объединение монтажное ИЛИ) с выходом коммутатора 5 и связан с информационньм входом 33 сдвигателя

6.Его выход соединен с информационным входом 36 накапливающего сумматора 3. Входь: 37 знака переклюа

чателей 7 кода числа связаны со зна- KOBbiiMH разрядами соответственно регистра 1, сумматора 2, причем вход 37 переключателя 7 подключен к инверсному выходу 38 знакового разряда сумматора 2. Выход 39 накапливающего сумматора 2 соединен .с управлякндим входом 20 переключателя 7 кода числа. Отметим, что вход 20 состоит из двух шин - первой 40 и второй 4 .Знаковый разряд второго накапливающего суммато- :ра 2 соединен с первой шиной 40 входа 2U третьего переключателя 7. Выход 42 .перегелючателя 7 состоит из двух шин - первой 43 и второй 44.

Выходами интерполятора являются четыре выхода двух логических блоков 8 (координата к:х+1; х-1; координата уО. Входами интерполятора являются п-разрядныб входы 45 занесения первого (параметр а) и второго (параметр йх,) регистра 1 и п-разрядный вход 46 предварительной установки накапливающего сумматора 2 (параметр йУо)о Выходы 42 переключателей 7 кода числа связаны с управляющими входами 47 коммутаторов 5.

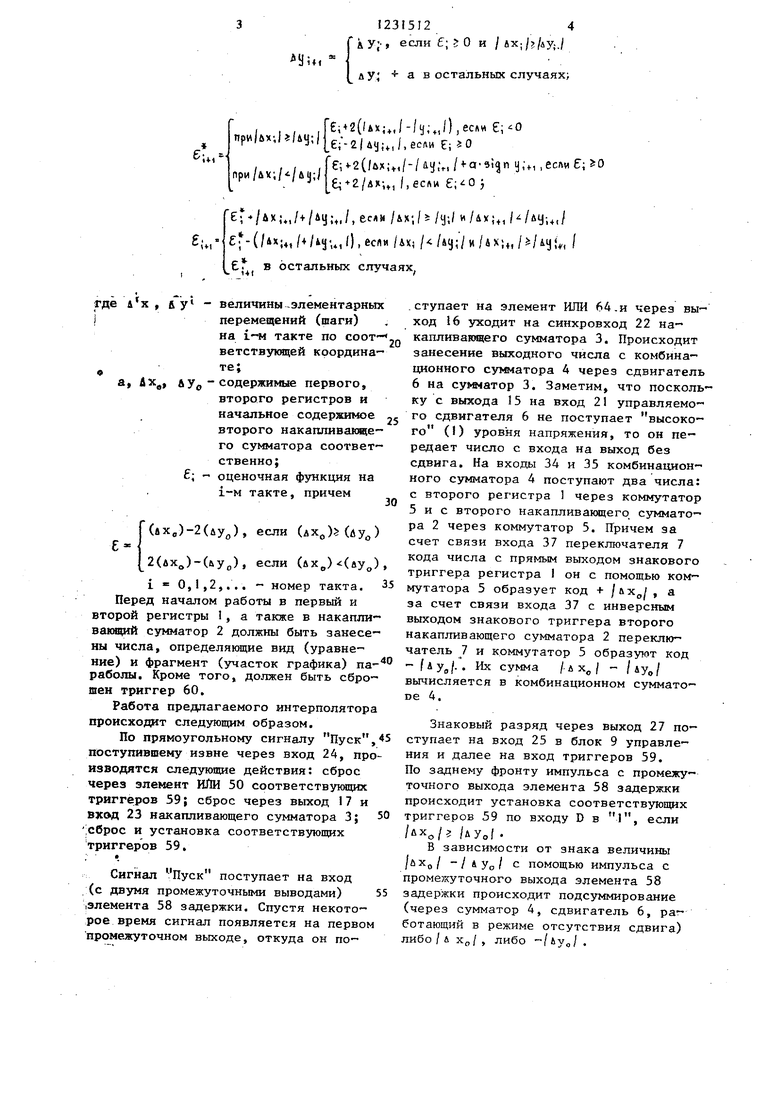

Пере1слючатель 7 кода числа содержит (фиг. 2) двухвходовой логический элемент 48 сложение по модулю два и логический элемент НЕ 49.

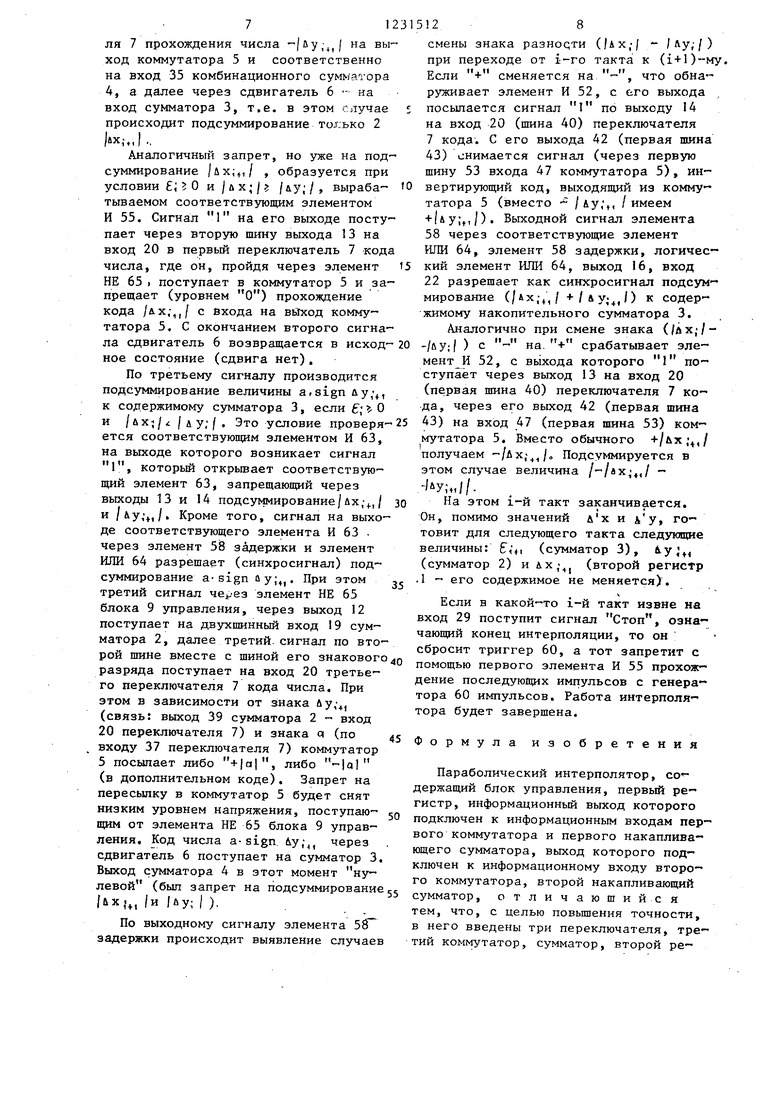

Комментатор 5 содержит (фиг. 3) вд каждый (из п) разряд двухвходовой логический элемент ИЩ 50, первый и второй трехнходовые элементы И 51 (с запретом) и 52, логический элемент 53 сложение по модулю два, причем управляющий вход 47 состоит из двух шин (первой 54 и второй 55).

Логический блок 8 содержит (фиг. 4) логический элемент НЕ 56, три двухвходовык логических элемента И 57.

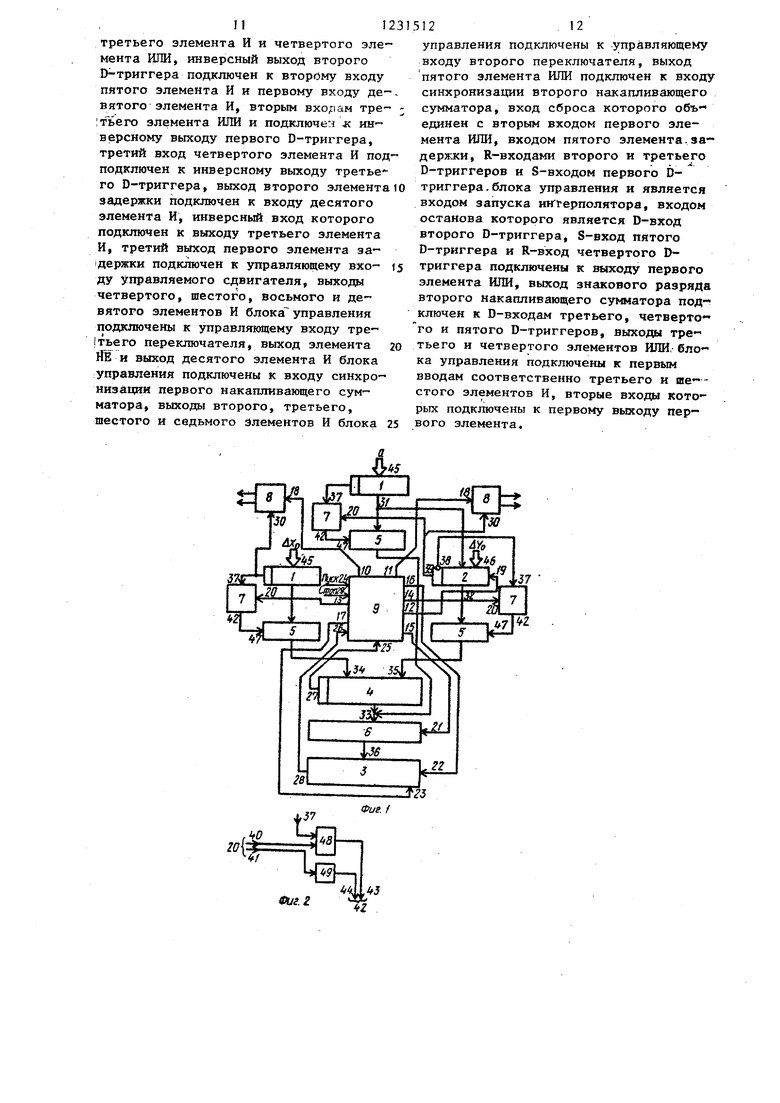

Блок 9 управления содержит(фиг. 5) элементы 58 задержки, пять D-тригге- ров 59, RS-триггер 60, генератор 61 тактовых импульсов, формирователь 62 импульсов, десять элементов И 63, элементы ИЛИ 54, элемент НЕ 65.

Интерполятор работает в соответствии с .алгоритмом.

О, если ; О и /лх; | / А у;/

л х

д у

) Lgn а X ; в остальных случаях- 0, если e;5 О и |AX;/S/ а У;/

ь х.Ч, ,чаях;

4Х. В остальных слуАН;

1+1

При/их;) /4у;| при/4ч;/ /61);|

еи2(|А)си./-/у,чЛ),если

ei -2Uyu,|,ecAv« Е; гО e;v2(/uxu,/-/uy,V,/ -a-9ign у,ч, ,если5; 0

б + г/Ак;, |,если

ж

ЕИ/ЛХ.,/, если /iv./i /У;/ И/AVU, ,4,/

ef-(/Axu,/+ /4«juiо. ес«« /А и . . /

в остальных случаях.

где л х , & у - величины-элементарных 1перемещений (шаги)

на i- такте по соот- - ветствукнцей крордина- те;

а, АХ, А у, - содержимые первого, второго регистров и начальное содержимое jj второго накапливающего сумматора соответственно;

; - оценочная фзжкция на i-M такте, причем

(ах,)-2(луд), если (AX)s(uy)

2(4х„)-(луо), если (лХо)(йу„),

i 0,1,2,.., номер такта. 35 Перед началом работы в первый и второй регистры 1, а также в накапливающий сумматор 2 должны быть занесены числа, определяющие вид (уравнение) и фрагмент (участок графика) раболы. Кроме того, должен быть сброшен триггер 60.

Работа предлагаемого интерполятора происходит следующим образом.

По прямоугольному сигналу Пуск,5 поступившему извне через вход 24, производятся следующие действия: сброс через элемент ИЛИ 50 соответствующих триггеров 59; сброс через выход 17 и вход 23 накапливающего сумматора 3; 50 :Сброс и установка соответствующих триггеров 59.

,

Сигнал Пуск поступает на вход (с двумя промежуточными выводами) 55

.элемента 58 задержки. Спустя некоторое время сигнал появляется на первом

промежуточном выходе, откуда он по-

I23I5I24

iyj., если 5; $0 и / У;./

ду; -i- а в остальных случаях;

.ступает на элемент ИЛИ 64.и через выход 16 уходит на синхровход 22 накапливающего сумматора 3. Происходит занесение выходного числа с комбинационного сумматора 4 через сдвигатель 6 на сумматор 3. Заметим, что поскольку с выхода 5 на вход 21 управляемого сдвигателя 6 не поступает высокого (1) уровня напряжения, то он передает число с входа на выход без сдвига. На входы 34 и 35 комбинационного сзгмматора 4 поступают два числа: с второго регистра I через коммутатор 5 и с второго накапливакнцего сумматора 2 через коммутатор 5. Причем за счет связи входа 37 переключателя 7 кода числа с прямым выходом знакового триггера регистра I он с помощью коммутатора 5 образует код + , а за счет связи входа 37 с инверсным выходом знакового триггера второго накапливающего сумматора 2 переключатель 1 и коммутатор 5 образуют код - f А у„ /. . Их сумма / л х / - / ду„ / вычисляется в комбинационном суммато- ое 4.

Знаковый разряд через выход 27 поступает на вход 25 в блок 9 управления и далее на вход триггеров 59. По заднему фронту импульса с промежуточного выхода элемента 58 задержки происходит установка соответствующих триггеров 59 по входу D в 1, если /дуо/ .

В зависимости от знака величины /йХо/ - / АУо/ с помощью импульса с промежуточного выхода элемента 58 задержки происходит подсуммирование (через cyMNiaTop 4, сдвигатель 6, работающий в режиме отсутствия сдвига)

либо /4 Хо/ , либо -/Ауо / .

Первый случай /Д - 5- О выявляется элементом И 63, выходной сигнал которого через монтажное ИЛИ поступает на выход 13, а далее на вход 20 (вторая шина 41) блока 7 и запрещает через элемент НЕ 65, через вторую шину 44 выхода 42, через вторую шину 54 входа 47 подсуммирова- ние / U , закрыв низким уровнем все элементы И 51 и 32. В то же вре мя подсуммирование кода -/луо/ обес печивается путем его подачи из сумматора 2 через коммутатор 5 на вход 35 сумматора 4.

Второй случай выявляется элементом И 63 (при /iXp/ - /uyoJ- O), выходной сигнал которого через монтажное ИЛИ поступает на выход 14 и далее на вход 20 второго блока 7 (вторая шина 41). Это также (как и в только что рассмотренном случае) приведет к за-- крытию коммутатора 5, а в конечном случае к запрету подсуммирования ко- да /йУо/ . В то же время код /лх„/ будет подсуммирован через коммутатор 6.

Выходной сигнал элемента 58 за- держки поступает на вход S триггера 60, устанавливает его в 1, Сигнал с его прямого выхода открывает эле- мент И 63 и закрывает (сигналом с инверсного выхода) соответствующие зле менты И 63, На этом заканчивается начальный этап работы интерполятора, связанный с вычислением начального значения оценочной функции о.

Дальнейшая работа интерполятора проходит по аналогичному для

каждого i-ro такта, а начало каждого

, , такта задается генератором Ы,

пульсы которого проходят через открытый элемент И 63 и запускают формирователь 62. Его очередный сигнал прямоугольной формы поступает через элемент ИЛИ 69 на вход R первого и вход S соответствующих триггеров 58, ста- вя их в О и I соответственно, Кроме того, этот же сигнал переписывает содержимое одного из триггеров 58.в другой, т.е. заполняется старое значение sign (/4х;/- /ау;/). Кроме того, знак содержимого сумматора 3, поступающий через выход 28, вход 26 на вход D триггера 58 (;), заносится в этот триггер с помощью импульса с выхода формирователя 62. Далее этот же прямоугольный импульс поступает на элемент 58 задержки с тремя

промежуточными выводами (сигналы с них будем назьгоать первым, вторым и третьим сигналами),

Первый сигнал поступает в качестве синхросигнала через выходы 10 и 11 в логические блоки 8 (через их входы 18),. На выход 10 (координата х) чере з элемент ИЛИ 64 и элемент И 63 поступает сигнал об элементарном пе- редЕ1Ижении по координате х. Направление этого передвижения определяется в первом логическом блоке 8 в зависимости от сигнала, поступающего по входу 30 от знакового разряда второг регистра J, содержащего лх,-. Аналогичные действия, но уже через выход II, выполняются по коодинате у. Знак (по входу 30) берется со старшего разряда (выход 39) накапливающего сумматора 2 и в работе участвуют соответствующие элемент ИЛИ 64 и элемент И 63.

Первый сигнал, пройдя через эле - мент 58 задержки, через элемент И 63 (сигнал запрета вырабатывается соот- ветств тощим элементом И 63, если в i-M такте не было движения по координате х). через выход 12 поступает в качестЕ1е синхросигнала на вторую шину входа I9 накапливающего сумматора 2, совершая подсуммирование содержимого первого регистра 1 к содержимому сумматора 2.

По заднему фронту первого сигнала, через второй элемент ИЛИ 64 происходит запись в соответствующий триггер 59 нового значения Sign (/йх ;., / - 1дУ, и1 поступающего со знакового выхода 27 комбинационного сумматора 4 через вход 25 блока 9 управления на вход D этого триггера.

Второй сигнал с элемента 58 задержка по выходу 15 и входу 2 устанавливает (на время действия сигнала сдвигатель 6 в состояние сдвига на один разряд влево. Кроме того, через соответствующие элемент ИЛИ 64 и элемент 58 задержки, элемент ИЛИ 64 и выход 16 он поступает на вход 22 сумматора 3 в качестве синхросигнала. Этим самым производится подсуммирование 2 (/&.Х, /-/ 4у;/ ) по переднему фронту синхросигнала. При этом, если Е,- О и /ux;/t /&У; / а выходе соответствующего элемента И 63 появляется Г, запрещающая .через вторую шину выхода 14, вход 20 (вторая шина 41), через элемент НЕ 65 переключате71

ля 7 прохождения числа /йу;, | выход коммутатора 5 и соответственно на вход 35 комбинационного сум атора 4, а далее через сдвигатель 6 - на вход сумматора 3, т.е. в этом случае происходит подсуммирование то1:ько 2 |&х,ч,1 „

Аналогичный запрет, но уже на подсуммирование /ixit,/ , образуется при условии ; О и ах |г /лу;/, выраба- тываемом соответствующим элементом И 55. Сигнал 1 на его выходе поступает через вторую шину выхода 13 на вход 20 в первый переключатель 7 кода числа, где он, пройдя через элемент НЕ 65 . поступает в коммутатор 5 и запрещает (уровнем О) прохождение кода /дх;,,/ с входа на вйход коммутатора 5. С окончанием второго сигнала сдвигатель 6 возвращается в исход- вое состояние (сдвига нет).

По третьему сигналу производится подсуммирование величины a,, к содержимому сумматора 3, если Е; О и / д у; / . Это условие проверяется соответствующим элементом И 63, на выходе которого возникает сигнал 1, который открьгоает соответствующий элемент 63, запрещающий через выходы 13 и 14 подсуммирование/Дх;, / и /Лу,,/. Кроме того, сигнал на выходе соответствующего элемента И 63 . через элемент 58 задержки и элемент ИЛИ 64 разрешает (синхросигнал) подсуммирование а-sign fly;,. При этом третий сигнал через элемент НЕ 65 блока 9 управления, через выход 12 поступает на двухщинный вход I9 сумматора 2, далее третий, сигнал по второй шине вместе с шиной его знакового разряда поступает на вход 20 третьего переключателя 7 кода числа. При этом в зависимости от знака Лу;, (связь: выход 39 сумматора 2 - вход 20 переключателя 7) и знака а (по входу 37 переключателя 7) коммутатор 5 посыпает либо +|а|, либо -|а) (в дополнительном коде). Запрет на пересылку в коммутатор 5 будет снят низким уровнем напряжения, поступаю- щим от элемента НЕ 65 блока 9 управления. Код числа а-sign. &у;, через сдвигатель 6 поступает на сумматор 3. Выход сумматора 4 в этот момент нулевой (бып запрет на подсуммирование /ьх., |и /fiy; I ).

По выходному сигналу элемента 5S задержки происходит выявление случаев

смены знака разности (|АХ;| - /лу,-/) при переходе от i-ro такта к (i+l)-M Если + сменяется на -, что обна- руживает элемент И 52, с tro выхода посьшается сигнал 1 по выходу 14 на вход 20 (шина 40) переключателя 7 кода. С его выхода 42 (первая шина 43) снимается сигнал (через первую шину 53 входа 47 коммутатора 5), инвертирующий код, выходящий из коммутатора 5 (вместо - /АУ;,, /имеем (iyit l) Выходной сигнал элемента 58 через соответствующие элемент ИЛИ 64, элемент 58 задержки, логический элемент ИЛИ 64, выход 16, вход 22 разрешает как синхросигнал подсуммирование (/4х; + , / /ау;,/) к содержимому накопительного сумматора 3.

Аналогично при смене знака (/дх,-/ -/fty.-f ) с - на. + срабатывает элемент И 52, с выхода которого 1 поступает через выход 13 на вход 20 (первая шина 40) переключателя 7 кода, через его выход 42 (первая шина 43) на вход 47 (первая шина 53) коммутатора 5. Вместо обычного +/Дх ,/ получаем -/Лх., Под суммируется в этом случае величина .к/ -

У,Ч.//.

На этом i-й такт заканчивается. Он, помимо значений л х и i y, готовит для следующего такта следующие величины: f,, (сумматор 3), У.« (сумматор 2) и лх, (второй регистр Л - его содержимое не меняется).

Если в какой-то i-й такт извне на вход 29 поступит сигнал Стоп, означающий конец интерполяции, то он сбросит триггер 60, а тот запретит с помощью первого элемента И 55 прохождение последующих импульсов с генератора 60 импульсов. Работа интерполятора будет завершена.

Формула изобретения

Параболический интерполятор, со держащий блок управления, первый регистр, информационный выход которого подключен к информационным входам первого коммутатора и первого накапливающего сумматора, выход которого подключен к информационному входу второго коммутатора, второй накапливающий

сумматор.

отличаюши и с я

тем, что, с целью повышения точности, в него введены три переключателя, третий коммутатор, сумматор, второй ре-

гистр, управляемый сдвигатель, шесть элементов И и два элемента НЕ, причем выход знакового разряда первого регистра подключен к информационному входу первого переключателя, выход которого подключен к управляющему входу первого коммутатора, выход ка торого соединен с выходам сумматора и подключен к информационному входу управляемого сдвигателя, выход кото-- рого подключен к информационному входу второго накапливающего сумматораj информационный выход ззторого регистра подключен к информационному входу третьего коммутатора, выход которого подключен к первому входу сумматора, второй вход которого подключен к выходу второго коммутатора, управляющий вход которого подключен к выходу второго переключателя, информационный вход которого подключен к инверсному выходу знакового разряда первого накапливающего сумматора, прямой выход знакового разряда которого подключен к управляющему входу первого переключателя, управляющий вход третьего коммутатора подключен к выходу третьего переключателя, информационные вход которого подключен к выходу знакового разряда второго регистра, информаи,- онные входы первого и второго регистров и установочный вход первого накапливающего сумматора являются соответственно входами задания первого и второго параметров и входом началь- ной установки интерполятора, выход знакового разряда второго регистра подключен-к первому входу первого элемента И и входу первого элемента НЕ, выход которого подключен к пер- вому входу второго элемента И, второй вход которого объединен с вторым входом первого элемента И и подключен к выходу третьего элемента И, прямой выход знакового разряда пер- вого накапливающего сумматора подключен к первому входу четвертого элемента И и входу второго элемента НЕ, выход которого подключен к первому входу пятого элемента И, второй вход которого объединен с вторым входом четвертого элемента И и подключен к выходу шестого элемента И, а выходы первого, второго, четвертого и пятого элементов И являются информацией- ными выходами группы интерполятора, при этом блок управления содержит пять D-триггеров, RS-триггер, фор5

О 0 5 0 5

мирователь импульсов, десять элементов И, шесть элементов ИЖ, элемент НЕ, пять элементов задержки и гене рато)э тактовых импульсов, выход кото рого подключен к первому входу первого элемента И, выход которого подключен к входу формирователя импульсов, выход которого подключен к первому входу первого элемента ИЛИ, входам синхронизации первого и второго D- триггеров, и входу первого элемента задержки, первый выход которого подключен к ВХОДУ второго элемента задержки и первому входу второго элемента ИЛИ, выход которого подключен к входу синхронизации третьего D- тригг ера, прямой выход которого подключен к первому входу второго эле- мента, и и D-входу первого В-триггерЗ, прямой Е(ыход которого подключен к первьш Е1ходам третьего и четвертого элементов И и первому входу пятого элемента И, выход которого подключен к первый входам третьего и четвертого элементов ИЛИ и первому входу шестого , элемента И, выход которого подключен к входу элемента НЕ. и входу третьего элемента задержки, выход которого подключен к первому )зходу пятого элемента ШШ, второй вход которого подключен к выходу четвертого элемента задержки, вход котЪ- рого подключен к выходу шестого элемента ИЛИ, первый вход которого обы единен с вторыми входами второго и

четвертого элементов И и подключен к второму выходу первого элемента эат

держки, третий и четвертьй. выходы которого подключены соответственно к второму входу шестого элемента ИШ и второму входу, шестого элемента И, первый выход питого элемента задержки подключен к третьему входу пятого элемента ИЛИ, второму входу второго элемента ИЛИ и входам синхронизации четвертого и пятого D-триггеров, второй и третий выходы пятого элемента задержки подключены соответственно к четвертому входу пятого элемента ШШ и S-входу RS-триггера, прямой выход которого подключен к второму входу первого элемента И, инверсный выход RS-триггера подключен к первым входам седьмого и восьмого элементов И, прямой выход четвертого D-триггера подключен к второму входу седьмого элемента И, инверсный выход восьмого

элемента И, прямой выход второго О-триггера подключен к вторым входам

n1

третьего элемента И и четвертого элемента ИЛИ, инверсный выход второго 1 -триггера подключен к второму входу пятого элемента И и первому входу де- вятого элемента И, вторым входам тре- элемента ИЛИ и подключен к ин-- версному вьпсоду первого D-триггера, третнй вход четвертого элемента И под подключен к инверсному выходу третье го D-триггера, выход второго элемента задержки подключен к входу десятого элемента И, инверсный вход которого подключен к выходу третьего элемента И, третий выход первого элемента за- держки подключен к управляющему вхо- ДУ управляемого сдвигателя, выходал четвертого, шестого, восьмого и де вятого элементов И блока управления подключены к управляющему входу тре- тьего переключателя, выход элемента ЯЁ и выход десятого элемента И блока управления подключены к входу синхронизации первого накапливающего сумматора, выходы второго, третьего, шестого и седьмого Элементов И блока

1212

управления подключены к управляющему входу второго переключателя, выход пятого элемента ИЛИ подключен к входу синхронизации второго накапливающего сумматора, вход сброса которого объ единен с вторым входом первого элемента ИЛИ, входом пятого элемента.задержки, R-входами второго и третьего D-триггеров и S-входом первого D- триггера.блока управления и является входом запуска и П-ерполятора, входом останова которого является D-вход второго D-триггера, S-вход пятого О-триггера и R-вход четвертого D- триггера подключены к выходу первого элемента ИЛИ, выход знакового разряда второго накапливающего сумматора подключен к D-входам третьего, четвертого и пятого D-триггеров, выходы тре тьего и четвертого элементов ИЛИ. блока управления подключены к первым вводам соответственно третьего и ше-- стого элементов И, вторые входы которых подключены к первому выходу перого элемента.

AL

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интерполятор | 1983 |

|

SU1140098A1 |

| Цифровой линейный интерполятор | 1981 |

|

SU957171A1 |

| Круговой интерполятор | 1982 |

|

SU1024880A1 |

| Цифровой генератор синусоидальной функции | 1982 |

|

SU1043615A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

| Устройство для вычисления логарифма | 1984 |

|

SU1179328A1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам программного {управления станками и отображения графической информации. Целью изобретения является увеличение точности за счет использования в интерполяторе блока управления, трех коммутаторов, трех переключателей, двух регистров, двух накапливающих сумматоров, шести элементов И, двух элементов НЕ, сумматора, управляемого сдвигателя. Блок управления содержит пять D-триг- геров, RS-триггеров, десять элементов И, элемент НЕ, пять элементов задерж-. ки, шесть элементов ИЛИ и формирователь импульсов с связями. 5 ил. соответствующими (/) С

Фиг. 2

0i/e. f

«

Составитель A, Баранов Редактор М. Келемеш Техред И.Гайдош Корректор В.5утяга

Заказ 2652/52 Тираж 671 Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., , д. 4/5

Производственио-полиграфичсское предприятие, г„ Ужгород, ул. Проектная, 4

| Цифровой линейный интерполятор | 1981 |

|

SU957171A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Воронов А | |||

| А | |||

| и др | |||

| Цифровые аналоги для систем автоматического управления | |||

| М.: Изд-во АН СССР, 1960, с | |||

| Халат для профессиональных целей | 1918 |

|

SU134A1 |

Авторы

Даты

1986-05-15—Публикация

1984-11-10—Подача